目录

1.PD/DFT常用工具及流程

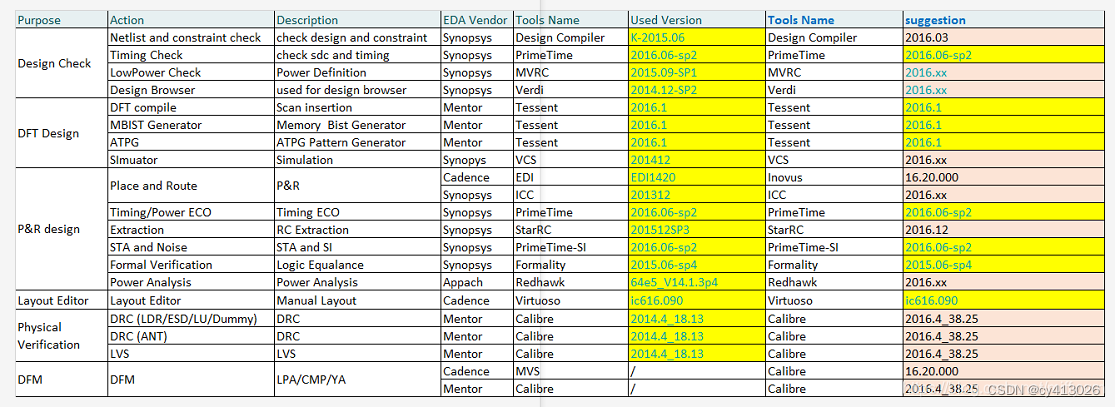

上面的表格即显示了从RTL到GDS要做的工作,也列举了相应的工具。由于版本较为久远,并没有提到今年来出现的Fusion compiler,这是一个可以完成综合和PR的工具,功能相当于DCG+ICC2,后文后简单介绍。

还少了一个lib转db的工具 Library compiler。

另外会同时介绍STA工具PrimeTime;功耗分析的Redhawk;PR工具ICC2和物理验证---Physical Verification的Calibre.

1.1 FC和ICC2

FC :是Fusion Compiler的简称,是 单个工具,能完成综合和布局布线 。 即输入RTL,输出GDS,故称RTL2GDS的工具。

IC Compiler II (ICC2): 是行业领先的布局布线解决方案,旨在支持FinFET 16nm以下先进工艺,消除前沿设计面临的性能、功耗、面积 (PPA) 和上市时间等紧迫压力。

而在FC之前只能用DCG/DCT完成带物理信息的综合【和前端的DC预综合还不太一样,一般BE也不会用FE的DC综合网表】,然后用ICC2来完成CTS+PR。FC在设计的PPA上有很好的表现,而且runTime要比ICC2快很多。这是因为FC是综合引擎代码是全部重新写过的,构架和算法是全新的。具体介绍可以参考本人的另一篇转自SNPS的介绍文章。

Fusion Compiler介绍 | 业内唯一RTL2GDS工具

1.2 LC (Library compiler)

在很多的时候,我们需要使用IP设计,比如SRAM IP(通常使用memory compiler 生成)得到的是.lib文件而不是.db文件。这时就需要Synopsys提供的library compiler工具将.lib文转为.db文件,提供给DC综合工具。

Library compiler的基本使用教程_数字芯片设计的博客-CSDN博客

1.3 PrimeTime

PrimeTime(PT)是Synopsys的签收品质(sign-off quality)的静态时序分析工具。静态时序分析(STA)无疑是设计流程中最重要的一步,它决定了设计是否在所要求的速度下工作,PT分析设计中的时序延迟并标注出必须改正的违例。

PT是一个不在DC工具套件中集成的单独的工具,它是一个和DC并行工作的单独的工具。PT与DC有一致的命令,它们生成类似的报告,并支持共同的文件格式。此外PT也能生成DC用于综合和优化的时序断言,PT的命令行界面是基于称为Tcl为工业标准语言。与DC的内部STA引擎相比,PT更快,占用的内存更少,并且还有其他的一些特色。

1.4 Redhawk与PA(power analysis)

PA:关注芯片功耗,静态和动态IR降,电荷迁移等;

redhawk是业内最流行的power signoff工具。ICC2可以直接调用redhawk的引擎进行IR drop, Power EM的分析.

IR Drop分析之Redhawk分析流程_redhawk pi_IC拓荒者的博客-CSDN博客

1.5 Calibre和物理验证PV

物理验证:关注芯片是否满足工艺设计规则,物理设计与逻辑网表的一致性;通常有两个简写

LV:layout verification

PV:physical verification

物理验证是基于设计的GDS(Graphic Data System,目前是第二代GDS,一般也会写作GDSII,已经成为业界的标准格式了。GDS的第一版基本作古,现在的提到的GDS其实都是指的是GDSII了,目前的版权属于C家),使用RSF(Run-Set-File)的物理规则描述文件对GDS版图进行检查。常用的工具有Calibre、ICV等,比较老的工具有Hercules,Dracula等。如前述,目前比较通用就是Calibre了。随着先进工艺的不断演进,最近几年S家也开始追随工艺趋势在LV市场上发力,ICV(IC Validation)就是S家最近几年在先进工艺领域力推的physical signoff 工具。在过往常用的工艺里边,大部分的RSF都是基于Calibre的SVRF(Standard Verification Rule Format)、TVF(Tcl Verification Format)语法格式的,可见Calibre在业界悠久的影响力。

随着工艺节点的越来越小,芯片的GDS数据量越来越大,为了便于文件传输,产生了OASIS(Open Artwork System Interchange Standard)格式,文件更小传输更便捷,也是SEMI力推的下一代版图数据格式,用于替代已经服役30多年的GDS格式。

上面一段内特摘自:

Calibre物理验证技术点滴 (上)_svrf语法_艾思芯片设计的博客-CSDN博客

物理验证是基于GDS的验证,常包含以下几项:

-

ant (Antenna)

-

dfm :Design for manufacturability

-

drc(design rule checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求;

-

erc (Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例等等;

-

lvs(layout versus schematic)验证:简单说,就是版图与逻辑综合后的门级电路的对比验证

-

pad

LVS 就是这么简单(数字后端物理验证篇)_lvs验证_IC拓荒者的博客-CSDN博客

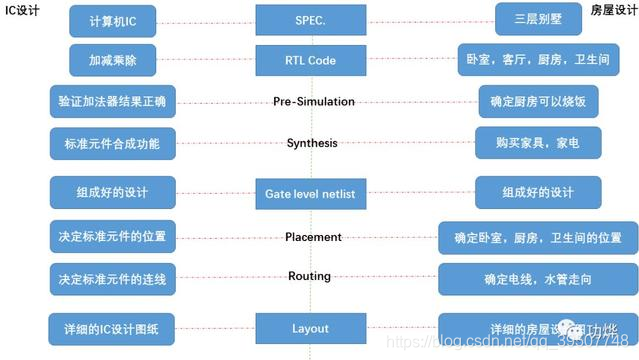

1.6 芯片设计流程

原创: 芯片设计流程及各步骤使用工具简介_研发中pdr cdr fdr是什么意思_耐心的小黑的博客-CSDN博客

转载:

2.后端、DFT、ATPG的一些常见文件

后端设计各种文件说明_cy413026的博客-CSDN博客 中已经给出部分文件,这里在补充一些。

2.1 LEF和DEF

| 文件名 | 全称 | 场景 |

|---|---|---|

| DEF | Design Exchange FIle | STA-PECO, APR数据交付以及重构,绕线/布局信息传递等和设计相事宜 |

| LEF | Library Exchange FIle | 物理库文件,工艺技术文件,APR层次化设计交付(配合ETM使用) |

芯片设计中的LEF文件浅析_def lef文件_艾思芯片设计的博客-CSDN博客

2.2 ATPG的CTL和STIL

IEEE Standard Test Interface Language (STIL) for Digital Test Vector Data—Core Test Language(CTL)

CTL:Core Test Language

STIL:IEEE Standard Test Interface Language

ctl用来描述一个模块的内部scan结构,比如内部scanchain长度,链首和链尾时钟等信息。

因为有的时候某些IP vendor不会让你知道里面的详细结构,但是ip包含scanchain,这个时候

就会给你一个ctl model,插链的时候读ctl model

stil是一种向量格式,用于ATE测试。

常用工具为TetraMAX(tmax)

TetraMAX II是以新的测试生成(test generation)、故障模拟(fault simulation)及诊断引擎(diagnosis engines)为基础所设计,这些引擎运作极其快速,并具备超高记忆体效率且针对型样生成优化所设计,它还可以有效执行ATPG及诊断流程的细质执行绪(fine-grained multithreading)。这些创新能大幅减少测试型样,并将ATPG时间从数天缩短至数小时。

2.3 BSDL

BSDL(边界扫描描述语言)文件是使用边界扫描进行电路板级和系统级测试与在系统编程所必需的。 BSDL 文件是描述一个 IC 中的 IEEE 1149.1 或 JTAG 如何在一个器件中实现的以及它是如何运行的,这些文件由 IC 供应商提供,作为其设备规格的一部分。

其实对大部分人来说 bsdl最重要的一个作用是描述boundary scan chain的结构。

2.4 IPXACT

IP-XACT首先由SPIRIT Consortium发布的标准,其唯一目标是在设计社区内促进IP的可重用性。它使IP提供商能够为组件和设计提供可读和可机器处理的IP的单一描述,并与其他所需的数据一起分享给IP用户。IP-XACT还描述了系统设计和IP之间的互连以及其他细节,如地址映射、接口等。提供了一个通用的设计表示,可供IP供应商、设计集成商和EDA工具提供商在其流程内进行交换。

IPXCT是以xml文件的形式存在,可以用Excel打开xml,比用文本编辑器要直观。

2.5 CDL netlist

CDL:circuit design Language,是网表的一种,是对电子电路的一种描述,可以由门级网表转化而来【cdl是带电源和地的verilog网表用工具(比如v2lvs)转出来的】,也可以来自 circuit schematic。

https://en.wikipedia.org/wiki/Circuit_design_language

电路级 SPICE/CDL网表,用于器件仿真或LVS检查。和SPICE的netlist相似。

LVS检查可以是GDS和CDL之间的check。

LVS Runset验证的另一种方法 - 腾讯云开发者社区-腾讯云

calibre做LVS需要两个文件,gds和cdl。calibre工具GUI上的layout就是指gds,而netlist是指cdl(或者说叫spice)

3.PCB设计的一些工作和工具

3.1 PI 电源完整性

Power Integrity:电源完整性简称PI,分析工具Hspice;

PI是确认电源来源及目的端的电压及电流是否符合需求,就是为板级系统提供一个稳定可靠的电源分配系统(PDS)。实质上是要使系统在工作时,电源、地噪声得到有效的控制,在一个很宽的频带范围内为芯片提供充足的能量,并充分抑制芯片工作时所引起的电压波动、辐射及串扰。目前,电源完整性还是高速PCB 设计最大的挑战之一。电源完整性涉及的层面包括芯片层面、芯片封装层面、电路板层面及系统层面。

电源完整性之仿真设计原理_电源完整性仿真_刘小同学的博客-CSDN博客

3.1.1 Hspice

- 对于片上仿真: 模拟设计、RF 设计、定制数字设计、标准单元设计和特征化、存储器设计和特征化,以及器件模型开发。

- 对于片外信号完整性仿真: 硅到封装到电路板到背板的分析和仿真

3.2 SI信号完整性

Signal integrity:信号完整性简称SI,分析工具ADS电子设计自动化(EDA软件全称为 Advanced Design System,是美国安捷伦(Agilent)公司所生产拥有的电子设计自动化软件。

SI是对于电子信号品质的一系列度量标准。在数字电路中,一串二进制的信号流是通过电压(或电流)的波形来表示。然而,自然界的信号实际上都是模拟的,而非数字的,所有的信号都受噪音、扭曲和损失影响。在短距离、低比特率的情况里,一个简单的导体可以忠实地传输信号。而长距离、高比特率的信号如果通过几种不同的导体,多种效应可以降低信号的可信度,这样系统或设备不能正常工作。信号完整性工程是分析和缓解上述负面效应的一项任务,在所有水平的电子封装和组装,例如集成电路的内部连接、集成电路封装、印制电路板等工艺过程中,都是一项十分重要的活动。信号完整性考虑的问题主要有振铃(ringing)、串扰(crosstalk)、接地反弹、扭曲(skew)、信号损失和电源供应中的噪音。---------该段摘自维基百科

信号完整性实践的重点是识别和修复PCB布局布线中的这些问题,从而使数字或模拟信号在传播过程中不会失真,并且能够在互连的过程中得到恢复。常见的眼图分析就属于SI分析的一种。

为了便于仿真,信号完整性工程师们提出了IBIS-AMI模型。IBIS(Input/Output Buffer Information Specification)模型;AMI的全称是:Algorithmic Modeling Interface,即算法建模接口。

4.IC signOff有哪些项

timing:setup check 建立时间检查——hold check 保持时间检查——drv check 最大传输时间检查和最大电容检查——SI check 信号一致性检查;

PA signoff:关注芯片功耗,静态和动态IR降,电荷迁移等;

PV signoff:关注芯片是否满足工艺设计规则,物理设计与逻辑网表的一致性;

RV signoff:关注ESD,latch up,ERC等检查;【什么是RV?rule verification?】

FM signoff:关注最终输出的逻辑网表与最初输入的逻辑网表之间的一致性;

CLP signoff:(Conformal Low Power)关注在低功耗设计中引入的特殊单元,电源域划分及组成单元的正确性;CLP 读入一个设计、一个power intent, 做power intent 本身quality 检查,并以power intent 为准则来check netlist 中low power cell 是否有多插、乱插、漏插,检查netlist 的pg 连接是否符合power intent 的定义,检查low power cell 的控制信号是否有问题

3488

3488

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?