基本概念

- timing arc

- cell delay

- net delay

- setup delay

- hold delay

- slack

- data arrive time

- data require time

- launch edge

- latch edge

时钟约束

生成时钟

使用create_generated_clock来约束生成时钟。

- 通过分频器生成的时钟

create_generate_clock -name clk_div_4 -divide_by 4 -source [get_pins reg|clk] [get_pins reg|q]

- 约束PLL输出的时钟

使用该命令会对设计中所有PLL的输出创建时钟。该命令会检测PLL设置,然后调用create_generated_clock命令约束PLL输出的时钟。

derive_pll_clocks

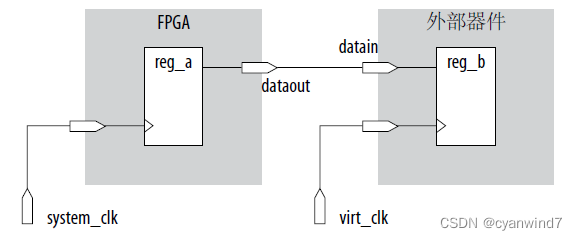

虚拟时钟

在I/O约束中使用虚拟时钟来表示驱动外部器件的时钟。

create_clock -period 5 [get_ports system_clk]

create_clock -period 10 -name virt_clk

set_output_delay -clock virt_clk -max 1.5 [get_ports dataout]

set_output_delay -clock virt_clk -min 0 [get_ports dataout]

时钟组

通过set_clock_groups约束可以指定哪些时钟是不相关的。

在默认情况下,所有时钟都是相关的。

以下命令表示clk_a1 clk_a2 clk_a3这3个时钟是一组的(即相关),clk_b1 clk_b2 clk_b3这3个时钟是一组的,如果整个设计还有别的时钟,则剩下的时钟是一组的。

set_clock_groups -asynchronous -group {clk_a1 clk_a2 clk_a3} -group {clk_b1 clk_b2 clk_b3}

I/O约束

- set_input_delay

通过set_input_delay设置input的约束。

set_input_delay -clock <clock_name> -min 2 [get_ports <input_port>]

set_input_delay -clock <clock_name> -max 4 [get_ports <input_port>]

- set_output_delay

通过set_output_delay设置output约束。在指定时钟时,需要指定输出端口的锁存(latch)时钟。

对于output_delay,max指定的值等效于外部电路的setup time,min指定的值等效于外部电路的hold time。

set_output_delay -clock <clock_name> -min -2 [get_ports <output_port>]

set_output_delay -clock <clock_name> -max 2 [get_ports <output_port>]

当我们使用分频器产生的时钟作为输出端口的锁存时钟时,没有指定这个时钟是通过FPGA的哪一个输出端口输出。这里需要怎么处理?是再定义一个时钟么?如果是需要再定义一个时钟,目前想到的是使用如下命令。

create_generated_clock -name <clock_name> -source [get_pins reg|clk] [get_pins reg|q]

create_generated_clock -name <clock_name> -source [get_pins reg|q] [get_ports <output_clock_port>]

我们在使用set_output_delay约束输出端口时,有时需要指定用于锁存数据的时钟为下降沿(默认是上升沿)。

set_output_delay -name <clock_name> -clock_fall [get_ports <output_port>]

2536

2536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?