洗衣机控制器verilog

名称:洗衣机控制器设计

代码下载链接:洗衣机控制器verilog_Verilog/VHDL资源下载

软件:Quartus

语言:Verilog

要求:

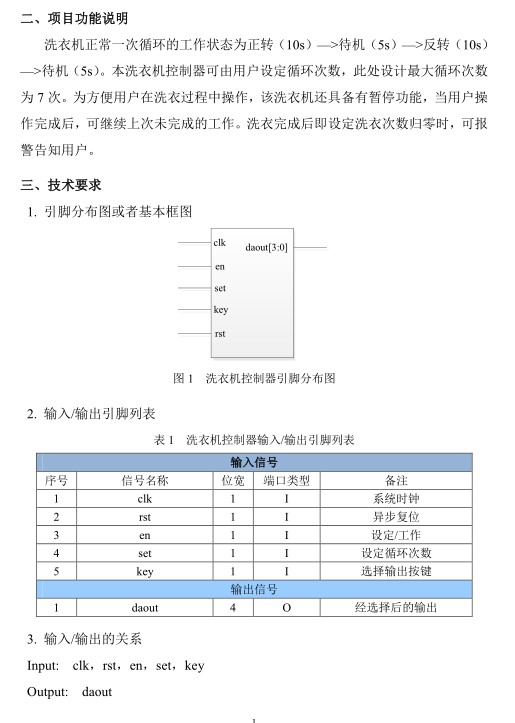

洗衣机正常一次循环的工作状态为正转(10s)—>待机(5s)→>反转(10s)一>待机(5s)。本洗衣机控制器可由用户设定循环次数,此处设计最大循环次数为7次。为方便用户在洗衣过程中操作,该洗衣机还具备有暂停功能,当用户操作完成后,可继续上次未完成的工作。洗衣完成后即设定洗衣次数归零时,可报警告知用户。

①clk为系统时钟,rst为复位键,控制整个系统复位。

②按set可以设置循环次数(拟设置一个寄存器,按键每按一次,寄存器值加

一,按set键超过7次仍算7次)。

③en为洗衣机启动或暂停控制信号。

④key为选择输出信号按键。key每次按下,daout在输出警报器alarm、洗衣机的工作状态lamp和输出剩余循环次数tim切换。

4.设计注意事项

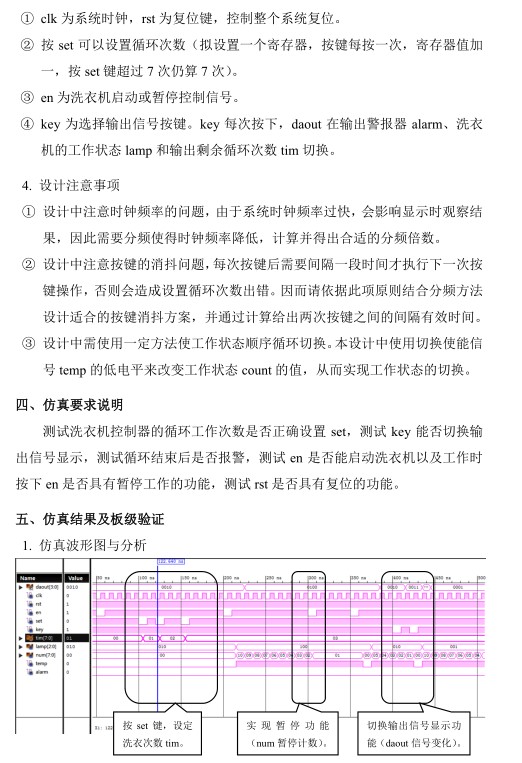

①设计中注意时钟频率的问题,由于系统时钟频率过快,会影响显示时观察结果,因此需要分频使得时钟频率降低,计算并得出合适的分频倍数。

②设计中注意按键的消抖问题,每次按键后需要间隔一段时间才执行下一次按键操作,否则会造成设置循环次数出错。因而请依据此项原则结合分频方法设计适合的按键消抖方案,并通过计算给出两次按键之间的间隔有效时间。③设计中需使用一定方法使工作状态顺序循环切换。本设计中使用切换使能信号temp的低电平来改变工作状态count的值,从而实现工作状态的切换。

四、仿真要求说明

测试洗衣机控制器的循环工作次数是否正确设置set,测试key能否切换输出信号显示,测试循环结束后是否报警,测试en是否能启动洗衣机以及工作时按下en是否具有暂停工作的功能,测试rst是否具有复位的功能。

代码下载链接:洗衣机控制器verilog_Verilog/VHDL资源下载

设计文档:

1816

1816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?