名称:FPGA的音乐彩灯VHDL流水灯LED

软件:Quartus

语言:VHDL

代码功能:

(1)设计一彩灯控制电路,按要求控制8路(彩灯由发光 二极管代替,受实验箱限制,多路同样控制方法)彩灯的亮灭。彩灯多种花样循环变换:从左至右一个一个点亮至全亮,然后从右至左一个一个熄灭至全灭;从左右两边同时向中间点亮至全亮,然后向两边逐个熄灭;中间间隔一个点亮。

(2)可以控制彩灯变换的节奏快慢:2个键控制四种节奏。

(3)加有清零开关,暂停键。

(4)有音乐模块,彩灯变换的同时伴有乐曲。

参数指标:系统时钟20MHz,存放4/4拍简单曲子,如梁祝,釆茶舞曲;至少一首。

演示视频:FPGA的音乐彩灯VHDL流水灯LED花样节奏变化_Verilog/VHDL资源下载

FPGA代码资源下载网:hdlcode.com

代码下载:

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY tonetab is PORT(index: in std_logic_vector(3 downto 0); tone:out std_logic_vector( 16 downto 0)); END; ARCHITECTURE one of tonetab is BEGIN search:PROCESS( index) BEGIN CASE index is--控制音调的预置数 WHEN "0000"=>tone<="11111111111111111";--0 WHEN "0001"=>tone<="10110101010110000";--中音 1 WHEN "0010"=>tone<="10111101011111011";--中音 2 WHEN "0011"=>tone<="11000100101111101";--中音 3 WHEN "0100"=>tone<="11001000000100101";--中音4 WHEN "0101"=>tone<="11001110001011000"; --- 中音 5 WHEN "0110"=>tone<="10100011100111000";--“ 中音 6 WHEN "0111"=>tone<="11011000011100111";---中音 7 WHEN "1000"=>tone<="11011010101011000";--一 高音 1 WHEN "1001"=>tone<="11011110101111101";----高音 2 WHEN "1010"=>tone<="11100010010111110";--“ 高音 3 WHEN "1011"=>tone<="11100100000010010";--一高音4 WHEN "1100"=>tone<="11100111000101100";--“ 高音 5 WHEN "1101"=>tone<="11101001110011011";--“ 高音 6 WHEN "1110"=>tone<="11101101010101100";--一 高高 1 when others =>null; END CASE; END PROCESS; END one; LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY speaker is PORT(clk: in std_logic; tone:in std_logic_vector( 16 downto 0);--17 spks:out std_logic); END speaker; ARCHITECTURE one of speaker is SIGNAL preclk,fullspks:std_logic; BEGIN PROCESS(clk,tone)---17位可预置计数器 VARIABLE count11:std_logic_vector(16 downto 0); BEGIN IF clk'event AND clk='1' THEN IF count11="11111111111111111" THEN--TONE〜11111111111111111 count11 :=tone; fullspks<='1'; ELSE count11:=count11+1;fullspks<='0';END IF; END IF;END PROCESS; PROCESS(fullspks)--二分频 VARIABLE count2: std_logic; BEGIN IF fullspks'event AND fullspks='1' THEN count2:=not count2; IF count2='1' THEN spks<='1'; ELSE spks<='0';END IF; END IF;END PROCESS;END;

设计文档:

1. 工程文件

2. 程序文件

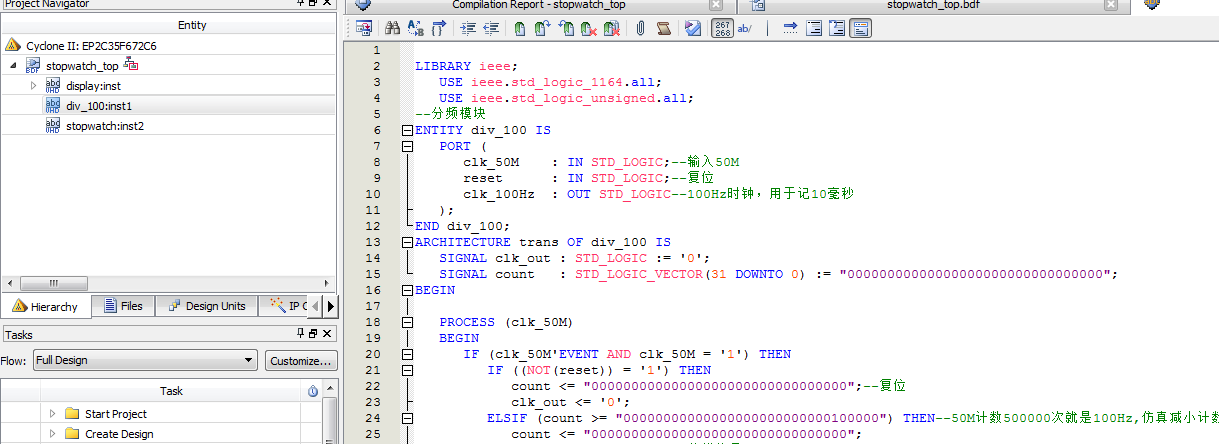

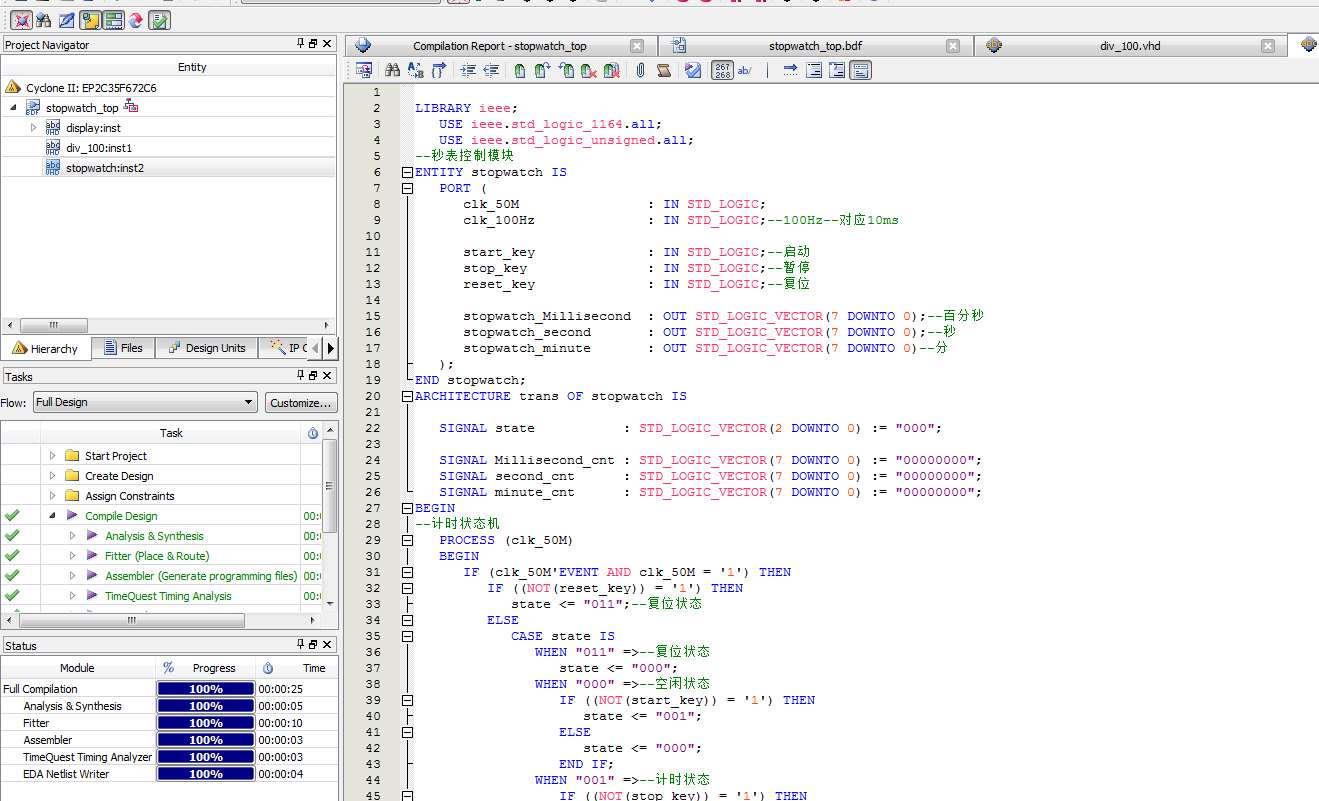

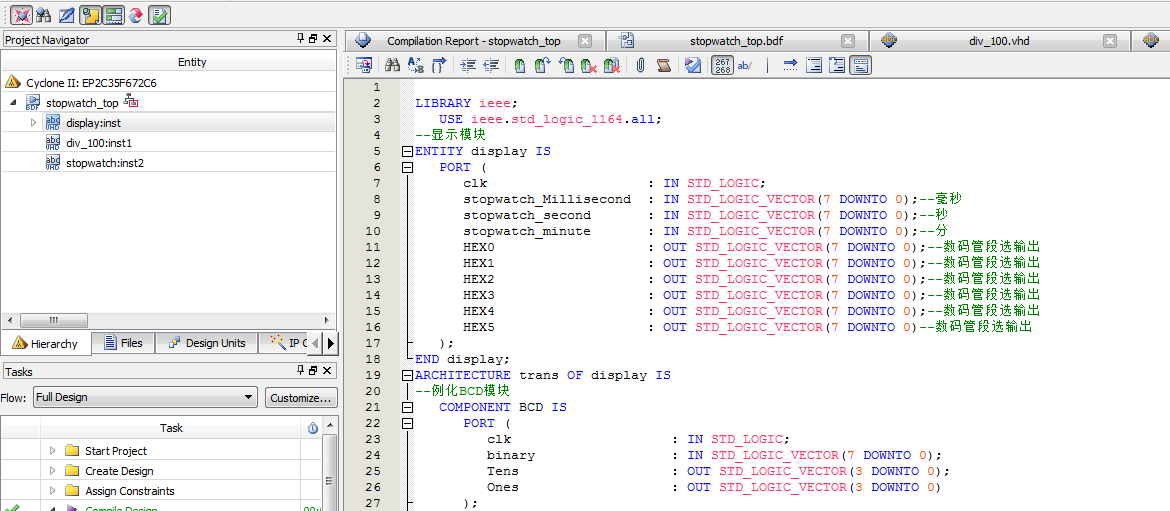

3. 程序编译

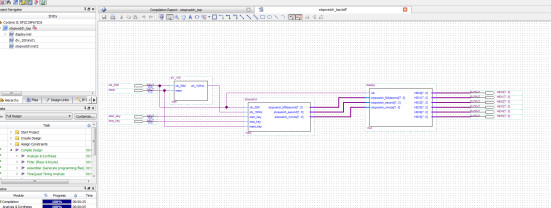

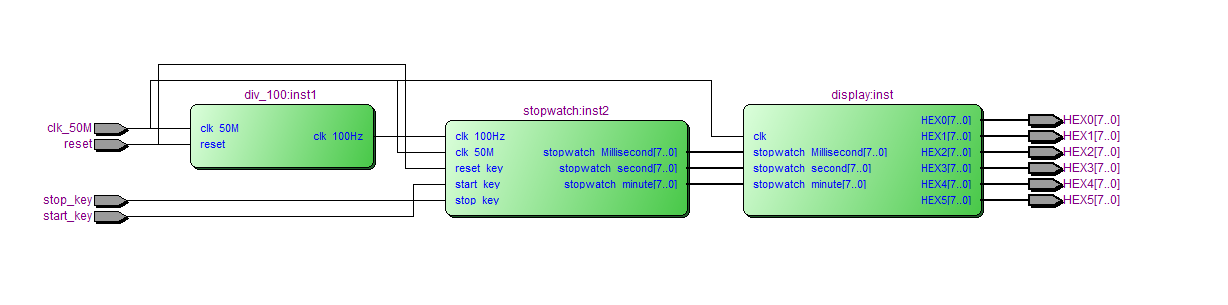

4. RTL图

5. 仿真图

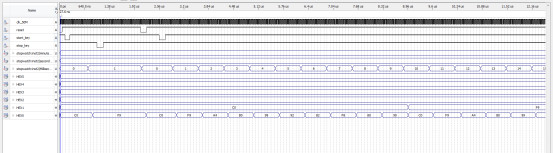

整体仿真图

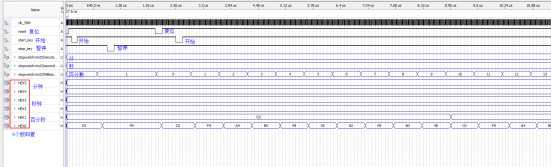

分频模块

控制模块

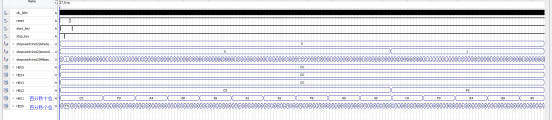

显示模块

2171

2171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?