名称:基于FPGA的彩灯流水灯控制器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

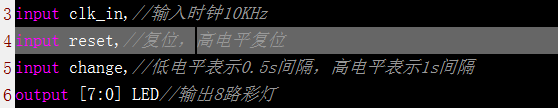

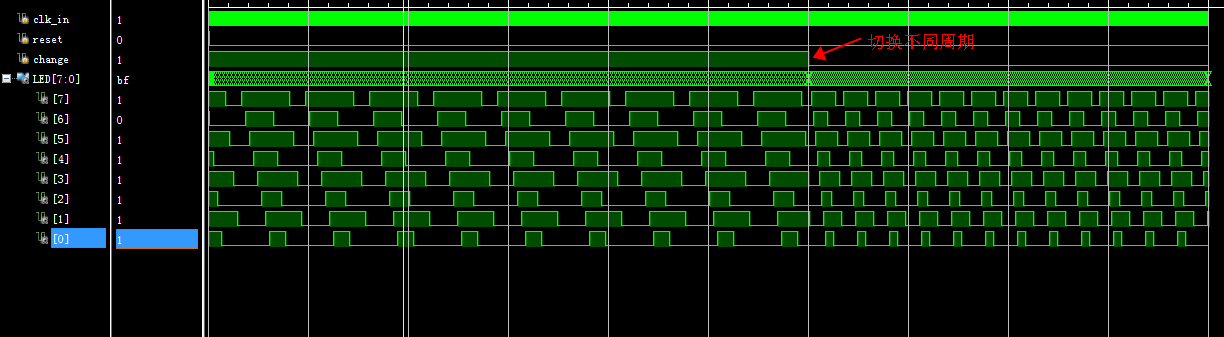

代码功能:八个LED彩灯L0到L7,显示方式为全亮,然后奇数灭,然后偶数灭,然后从L0到L7依次亮,循环进行,时间间隔0.5s,1s可调

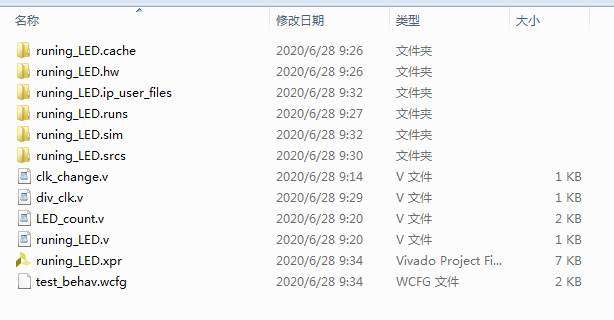

1. 工程文件

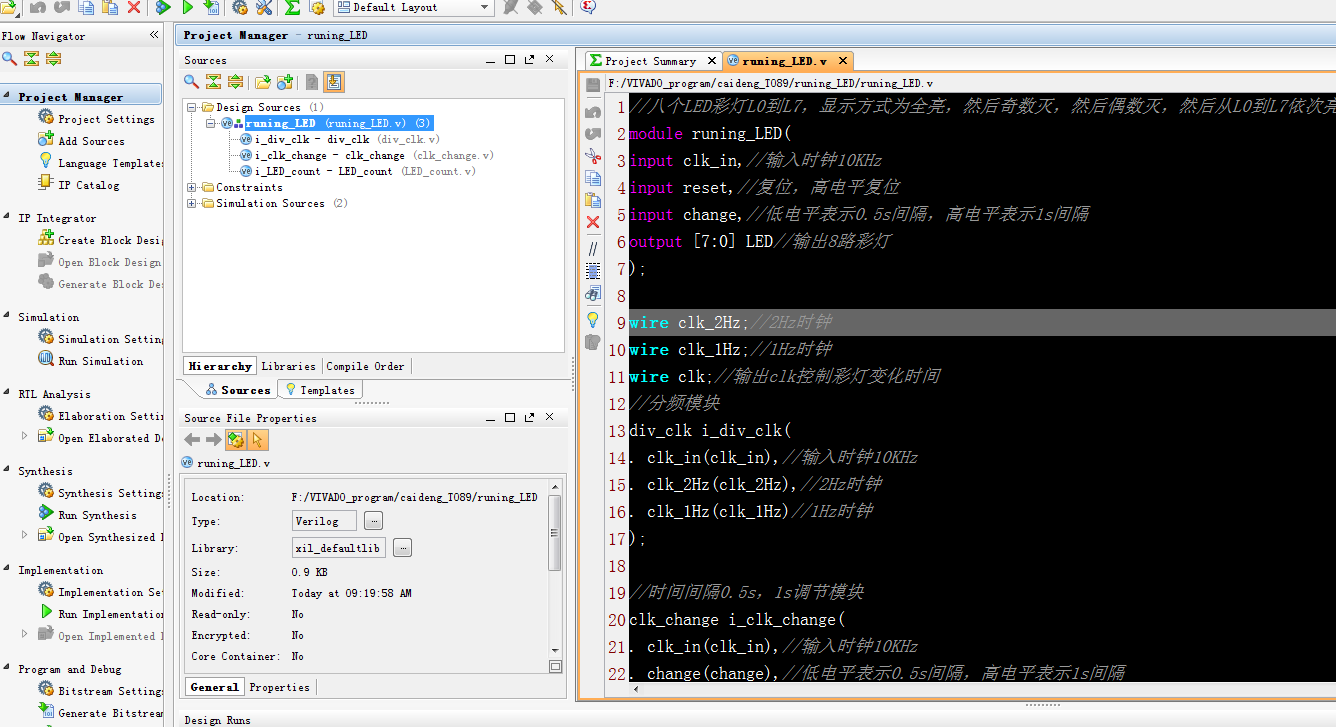

2. 程序文件

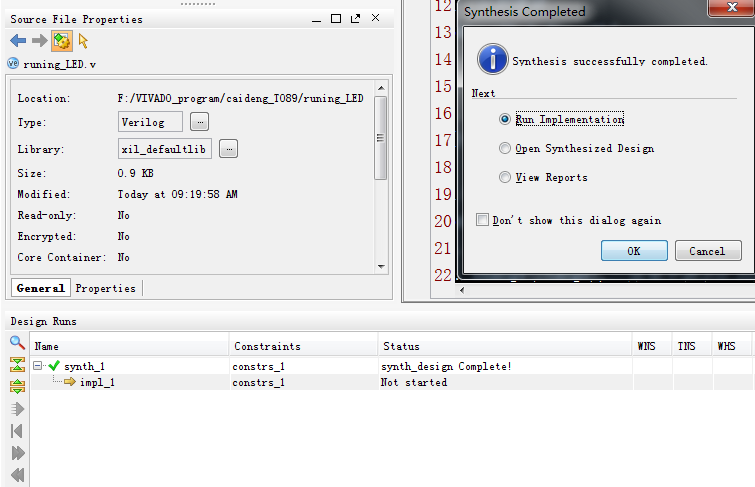

3. 程序编译

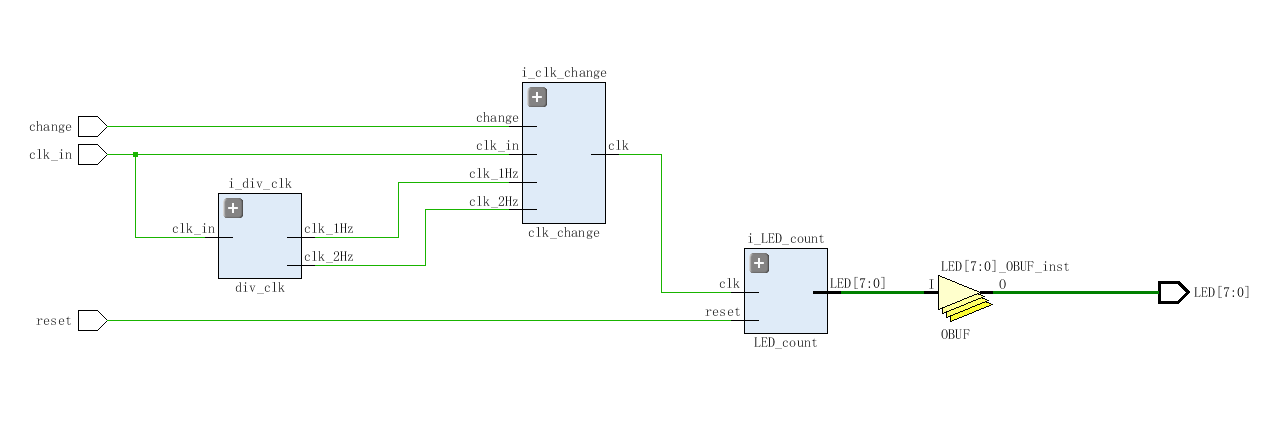

4. RTL图

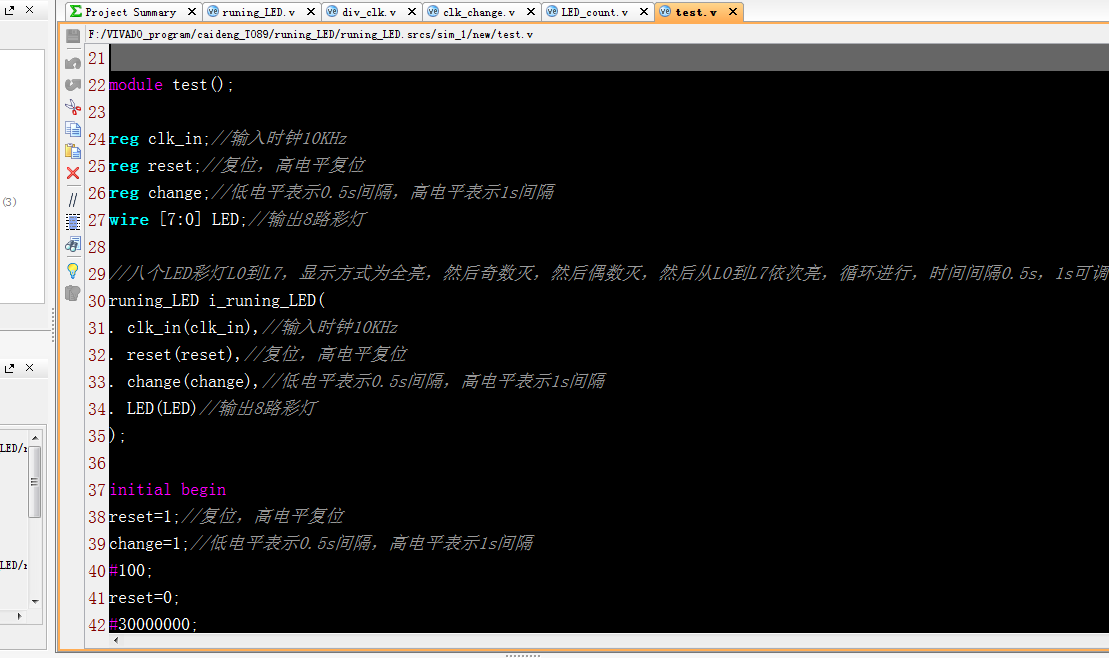

5. Testbench

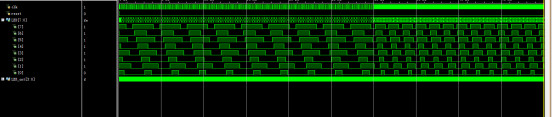

6. 仿真图

整体仿真

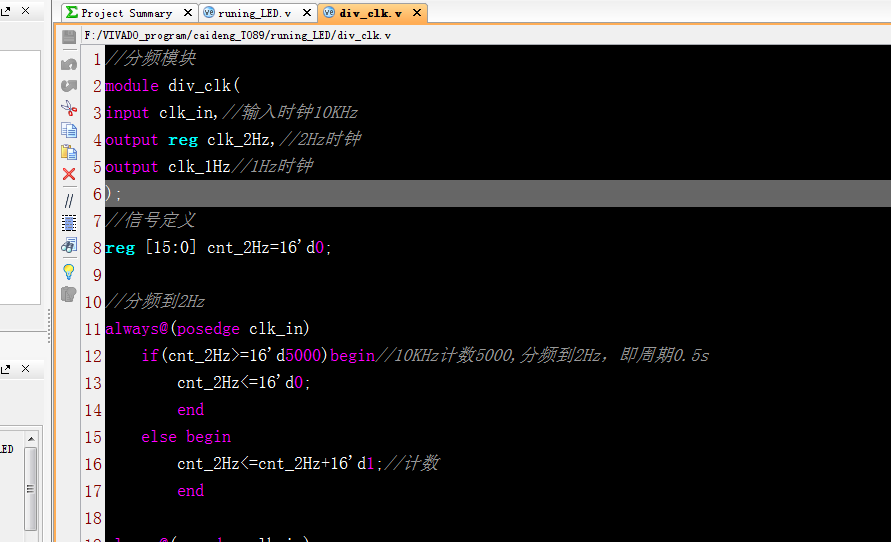

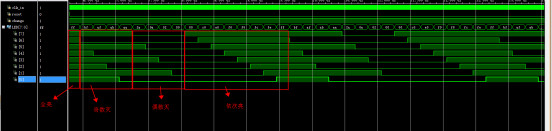

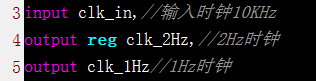

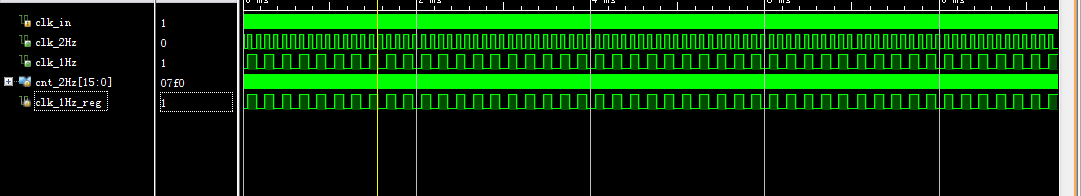

分频模块

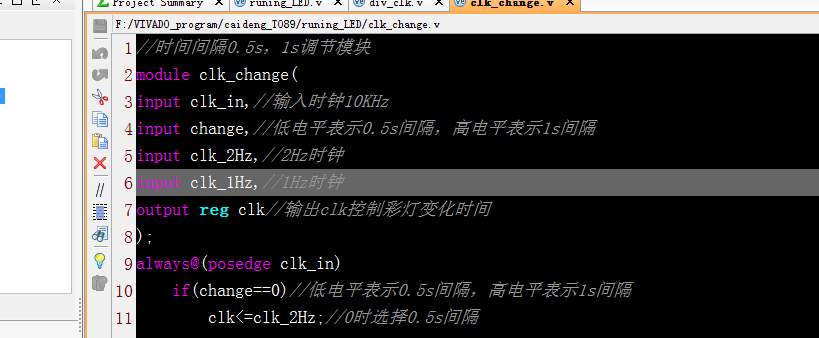

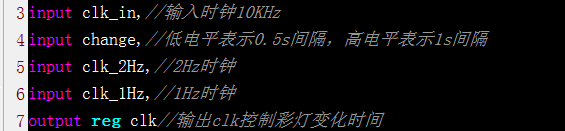

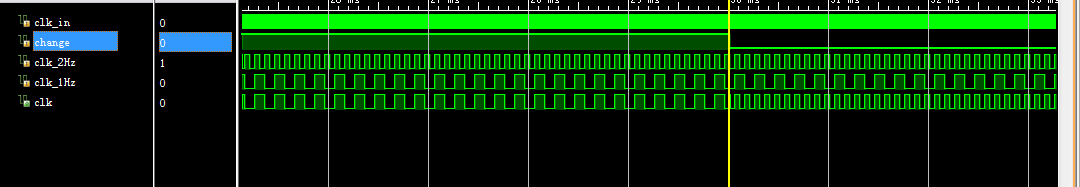

时间间隔0.5s,1s调节模块

彩灯控制模块

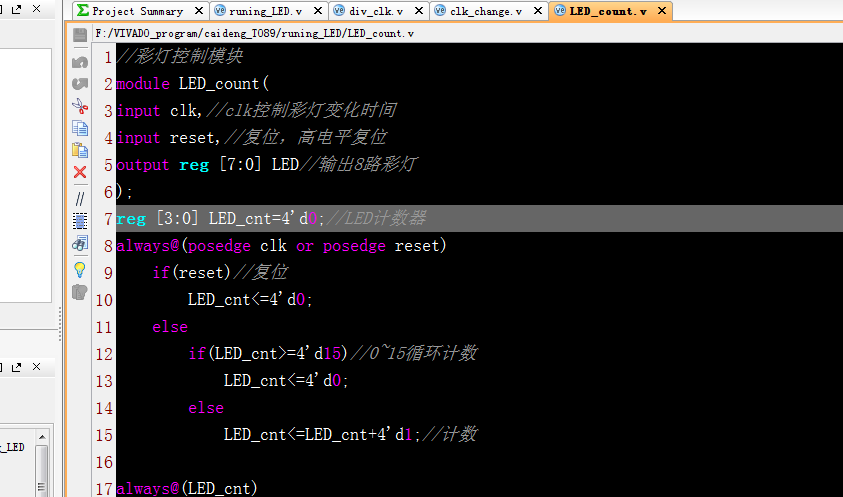

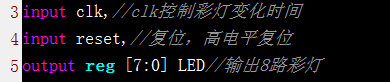

部分代码展示:

//彩灯控制模块 module LED_count( inp ut clk,//clk控制彩灯变化时间 input reset,//复位,高电平复位 output reg [7:0] LED//输出8路彩灯 ); reg [3:0] LED_cnt=4'd0;//LED计数器 always@(posedge clk or posedge reset) if(reset)//复位 LED_cnt<=4'd0; else if(LED_cnt>=4'd15)//0~15循环计数 LED_cnt<=4'd0; else LED_cnt<=LED_cnt+4'd1;//计数 always@(LED_cnt) case(LED_cnt)0~15循环计数,根据计数控制LED 4'd0: LED<=8'b11111111;//全亮 4'd1: LED<=8'b10111111;//奇数灯依次灭 4'd2: LED<=8'b10101111;//奇数灯依次灭 4'd3: LED<=8'b10101011;//奇数灯依次灭 4'd4: LED<=8'b10101010;//奇数灯依次灭 4'd5: LED<=8'b00101010;//偶数灯依次灭 4'd6: LED<=8'b00001010;//偶数灯依次灭 4'd7: LED<=8'b00000010;//偶数灯依次灭 4'd8: LED<=8'b00000000;//全灭 4'd9: LED<=8'b10000000;//依次亮 4'd10:LED<=8'b11000000;//依次亮 4'd11:LED<=8'b11100000;//依次亮 4'd12:LED<=8'b11110000;//依次亮 4'd13:LED<=8'b11111000;//依次亮 4'd14:LED<=8'b11111100;//依次亮 4'd15:LED<=8'b11111110;//依次亮,回到全亮循环 default:; endcase

源代码

扫描文章末尾的公众号二维码

1007

1007

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?