名称:基于Basys2开发板的7人表决器verilog代码

软件:ISE

语言:Verilog

代码功能:

设计一个7人表决器

1、7人表决,同意者大于3则表决通过

2、通过数码管显示赞成人数、反对人数

3、在开发板上进行验证

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在Basys2开发板验证,开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

2. 程序文件

3. 管脚约束

4. 程序编译

5. RTL图

整体框图

模块连接图

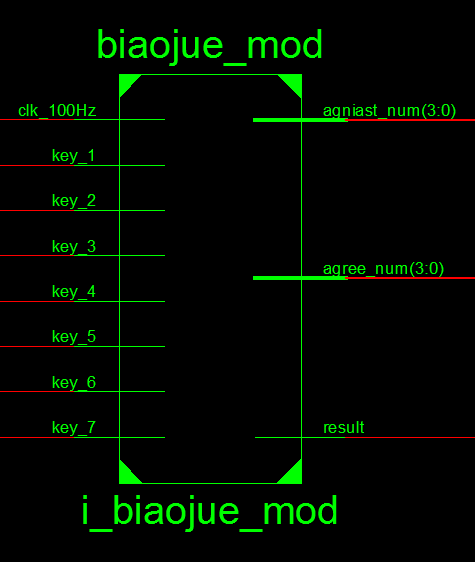

单模块

6. Testbench

7. 仿真图

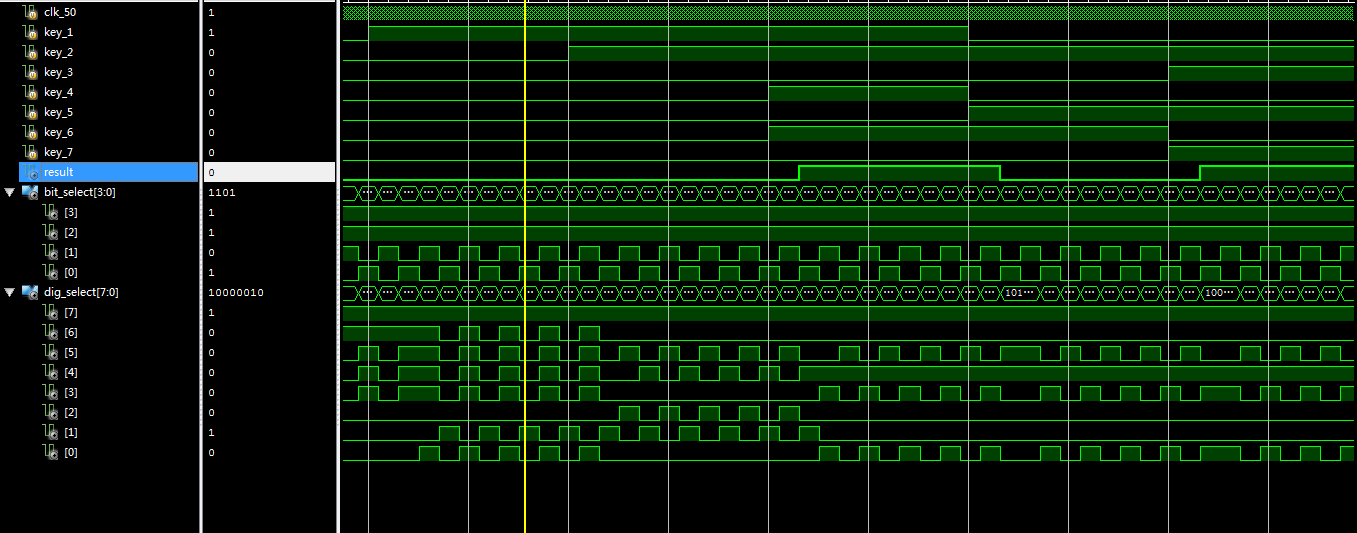

7.1 整体仿真图

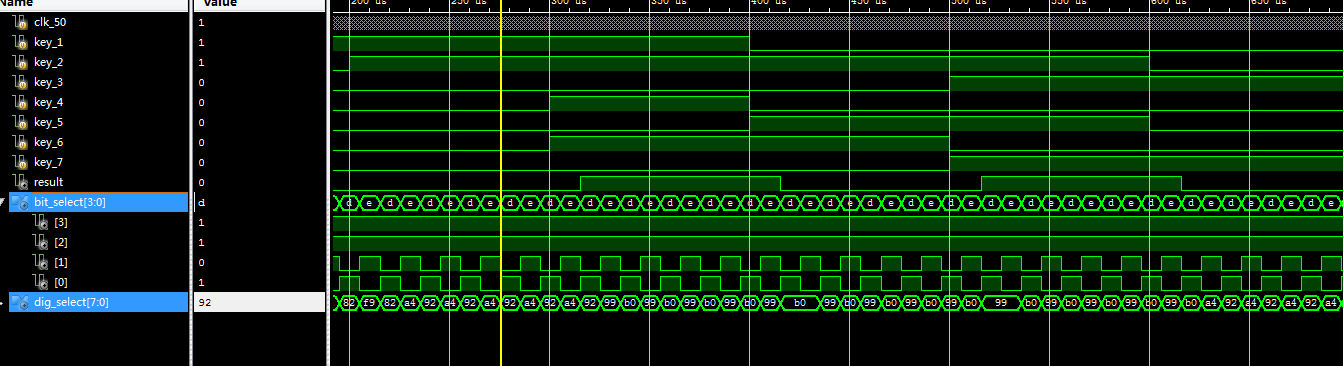

7.2 div_to_100模块

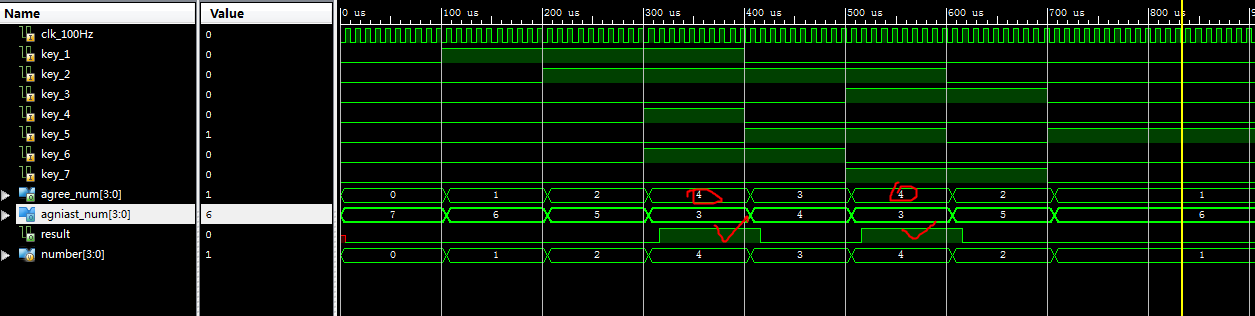

7.3 biaojue_mod模块

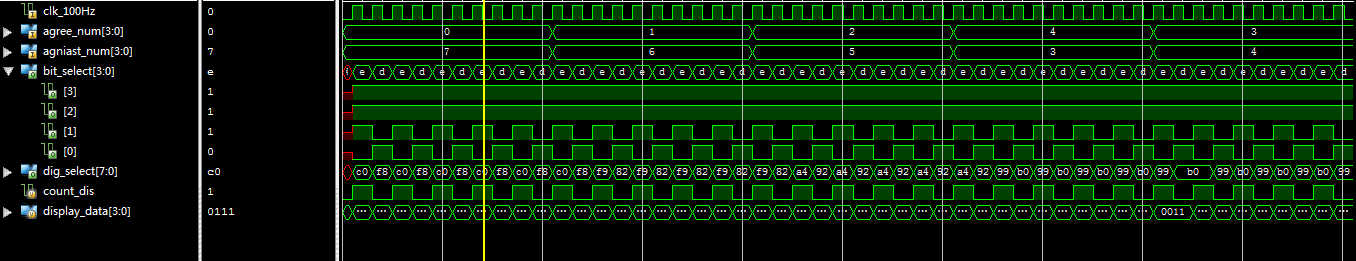

7.4 shumaguan模块

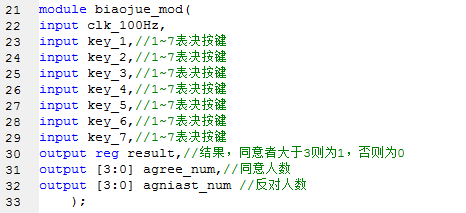

部分代码展示:

module biaojueqi( input clk_50,//50M时钟 input key_1,//1~7表决按键 input key_2,//1~7表决按键 input key_3,//1~7表决按键 input key_4,//1~7表决按键 input key_5,//1~7表决按键 input key_6,//1~7表决按键 input key_7,//1~7表决按键 output result,//结果,同意者大于3则为1,否则为0 output [3:0] bit_select,//位选 output [7:0] dig_select//段选 ); wire clk_100Hz; wire [3:0] agree_num;//同意人数 wire [3:0] agniast_num; //反对人数 //分频到100Hz模块 div_to_100 i_div_to_100 ( . clk_50(clk_50),//50M时钟 . clk_100Hz(clk_100Hz)//输出100Hz ); //表决模块 biaojue_mod i_biaojue_mod( . clk_100Hz(clk_100Hz), . key_1(key_1),//1~7表决按键 . key_2(key_2),//1~7表决按键 . key_3(key_3),//1~7表决按键 . key_4(key_4),//1~7表决按键 . key_5(key_5),//1~7表决按键 . key_6(key_6),//1~7表决按键 . key_7(key_7),//1~7表决按键 . result(result),//结果,同意者大于3则为1,否则为0 . agree_num(agree_num),//同意人数 . agniast_num(agniast_num) //反对人数 ); //数码管显示模块 shumaguan i_shumaguan ( . clk_100Hz(clk_100Hz),//100Hz时钟 . agree_num(agree_num),//同意人数 . agniast_num(agniast_num), //反对人数 . bit_select(bit_select),//位选 . dig_select(dig_select)//段选 ); endmodule

2062

2062

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?