名称:排队叫号电路系统verilog代码Basys3开发板验证

软件:VIVADO

语言:Verilog

代码功能:

设计一个排队叫号系统

1.进队,离队两个信号作为输入,当前服务号码和队长各由两个数码管显示

2.初始队长0,进队号码由1顺序递增,输出编号

3.有人入队长度加,有人出队长度减

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

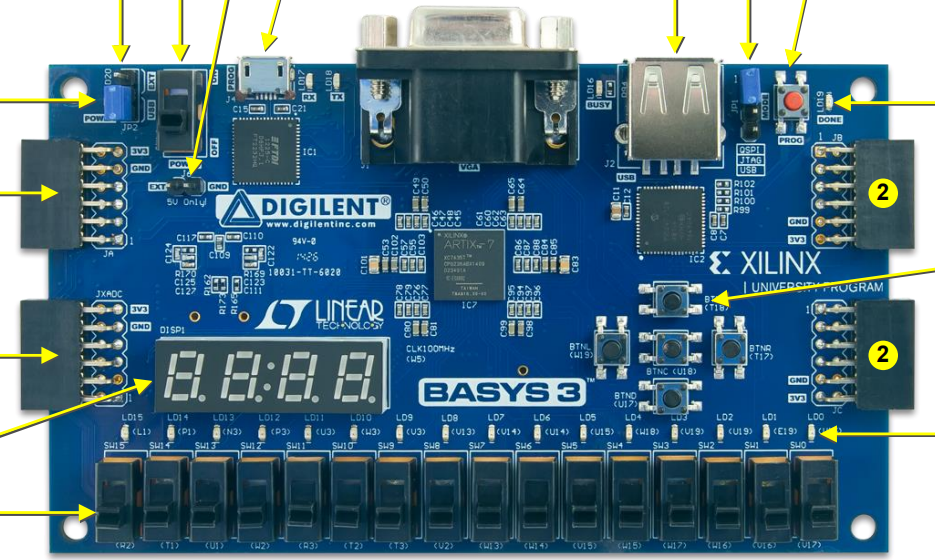

本代码已在Basys3开发板验证,开发板如下,其他开发板可以修改管脚适配:

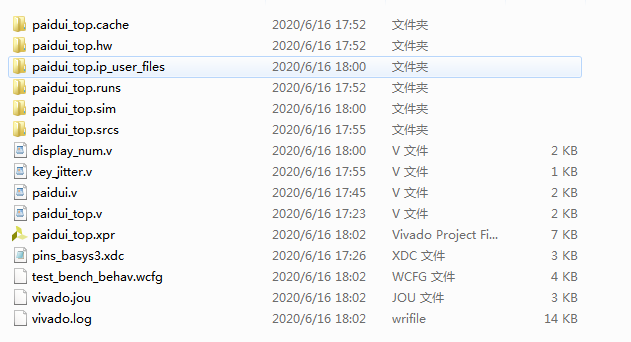

1. 工程文件

2. 程序文件

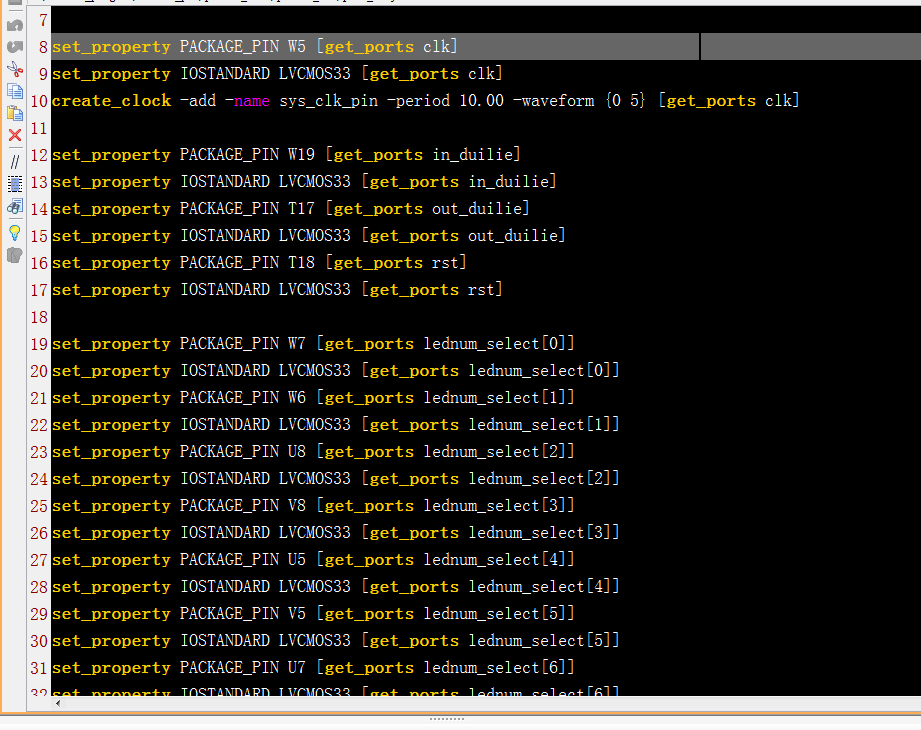

3. 约束文件

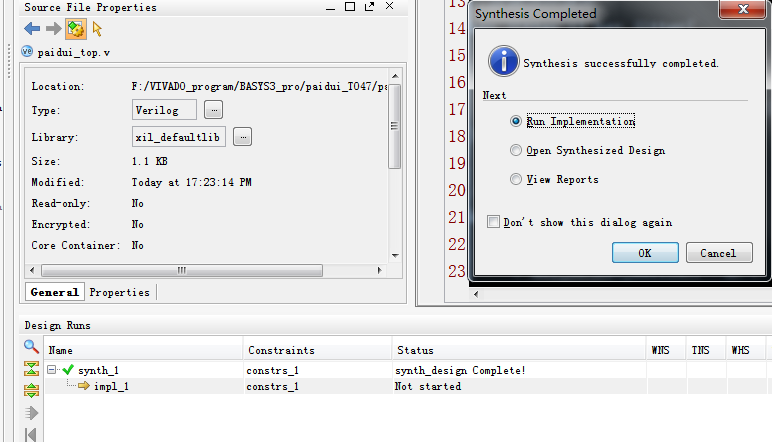

4. 程序编译

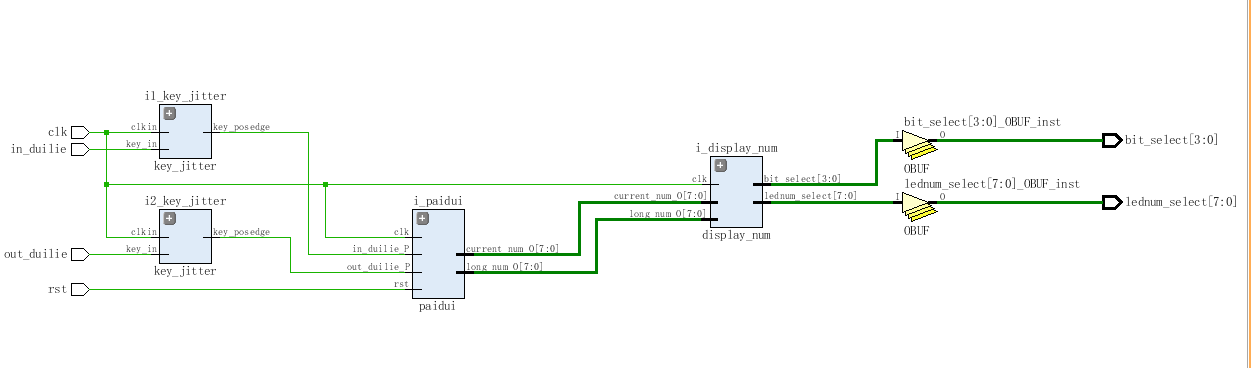

5. RTL图

6. Testbench

7. 仿真图

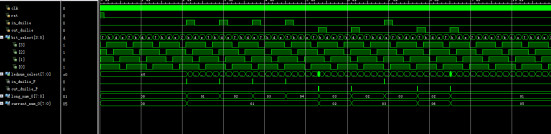

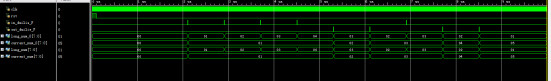

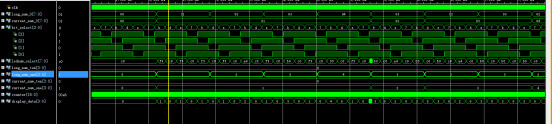

整体仿真

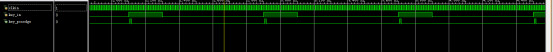

按键模块仿真

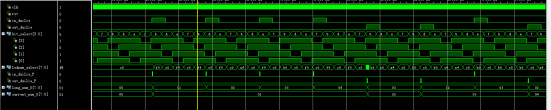

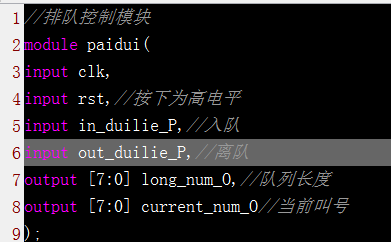

排队控制模块

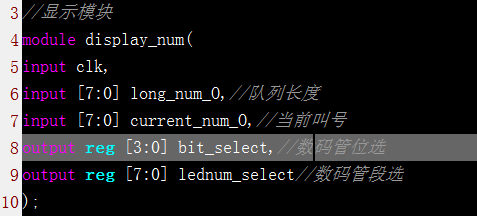

显示模块

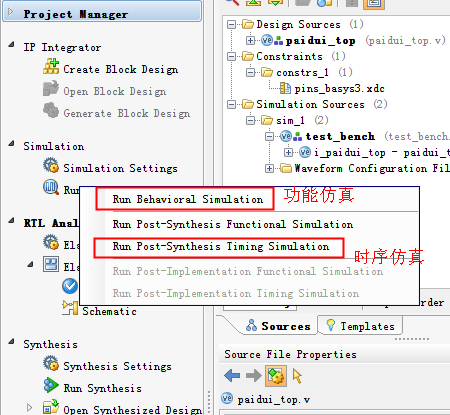

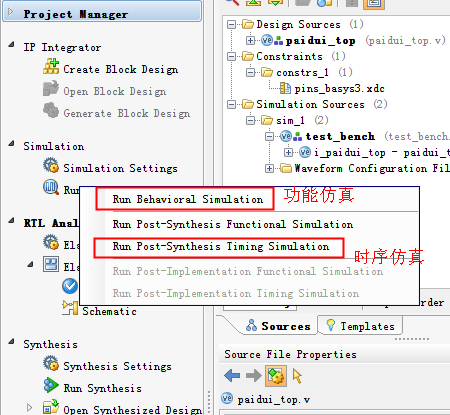

时序仿真与功能仿真类似,只需要编译综合后点击下图时序仿真即可,参考视频的步骤仿真

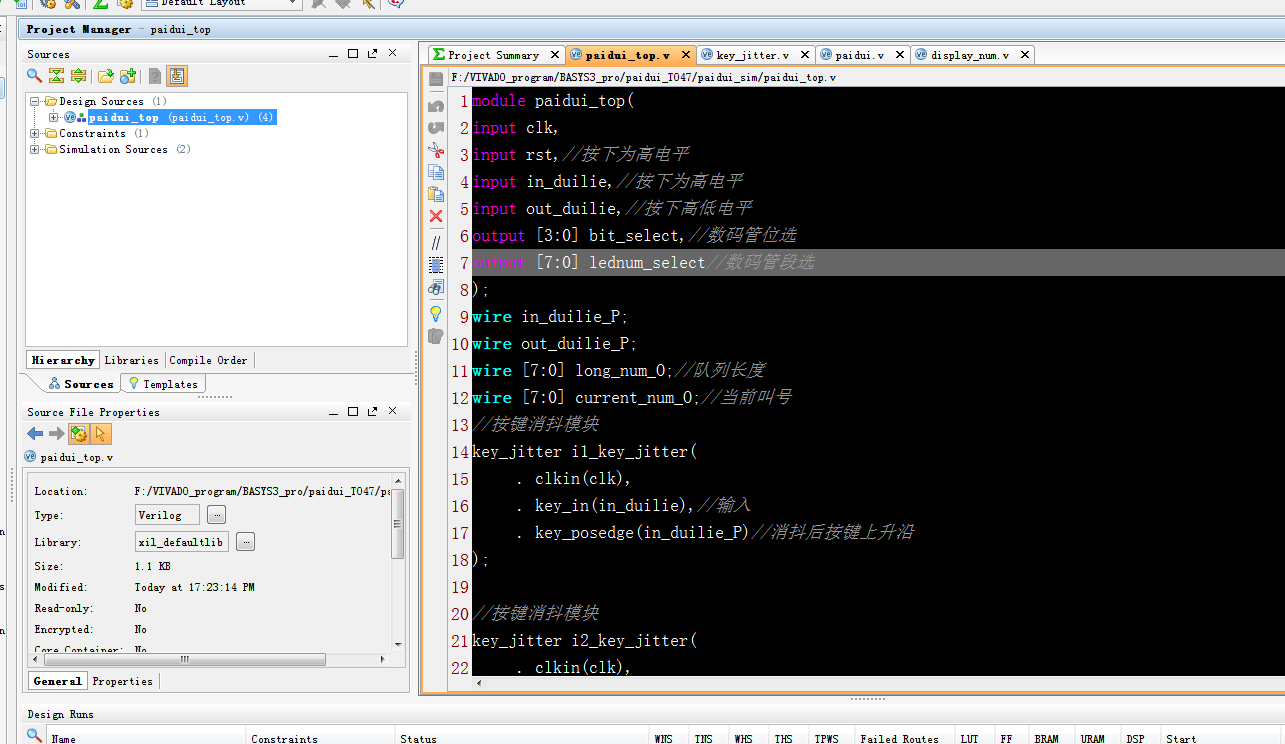

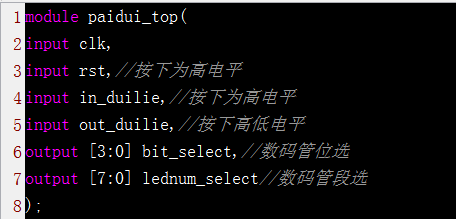

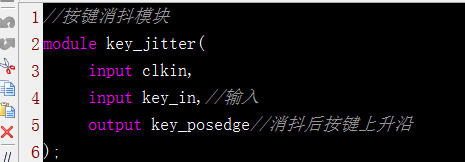

部分代码展示:

module paidui_top( input clk, input rst,//按下为高电平 input in_duilie,//按下为高电平 input out_duilie,//按下高低电平 output [3:0] bit_select,//数码管位选 output [7:0] lednum_select//数码管段选 ); wire in_duilie_P; wire out_duilie_P; wire [7:0] long_num_O;//队列长度 wire [7:0] current_num_O;//当前叫号 //按键消抖模块 key_jitter i1_key_jitter( . clkin(clk), . key_in(in_duilie),//输入 . key_posedge(in_duilie_P)//消抖后按键上升沿 ); //按键消抖模块 key_jitter i2_key_jitter( . clkin(clk), . key_in(out_duilie),//输入 . key_posedge(out_duilie_P)//消抖后按键上升沿 ); //排队控制模块 paidui i_paidui( . clk(clk), . rst(rst),//按下为高电平 . in_duilie_P(in_duilie_P),//入队 . out_duilie_P(out_duilie_P),//离队 . long_num_O(long_num_O),//队列长度 . current_num_O(current_num_O)//当前叫号 ); //显示模块 display_num i_display_num( . clk(clk), . long_num_O(long_num_O),//队列长度 . current_num_O(current_num_O),//当前叫号 . bit_select(bit_select),//数码管位选 . lednum_select(lednum_select)//数码管段选 ); endmodule

516

516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?