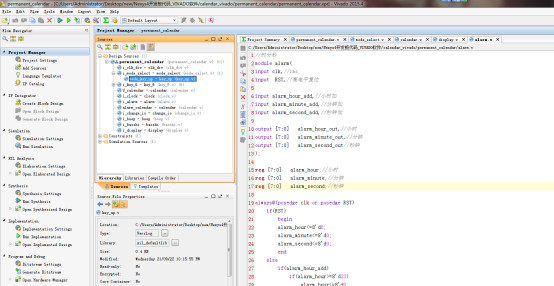

名称:VIVADO万年历verilog代码Nexys4开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

万年历要求

1、实现万年历功能,可以显示年月日,时分秒

2、支持按键调整时间,年月日,时分秒均可调整

3、使用按键切换年月日和时分秒的显示

FPGA代码Verilog/VHDL代码资源下载:hdlcode.com

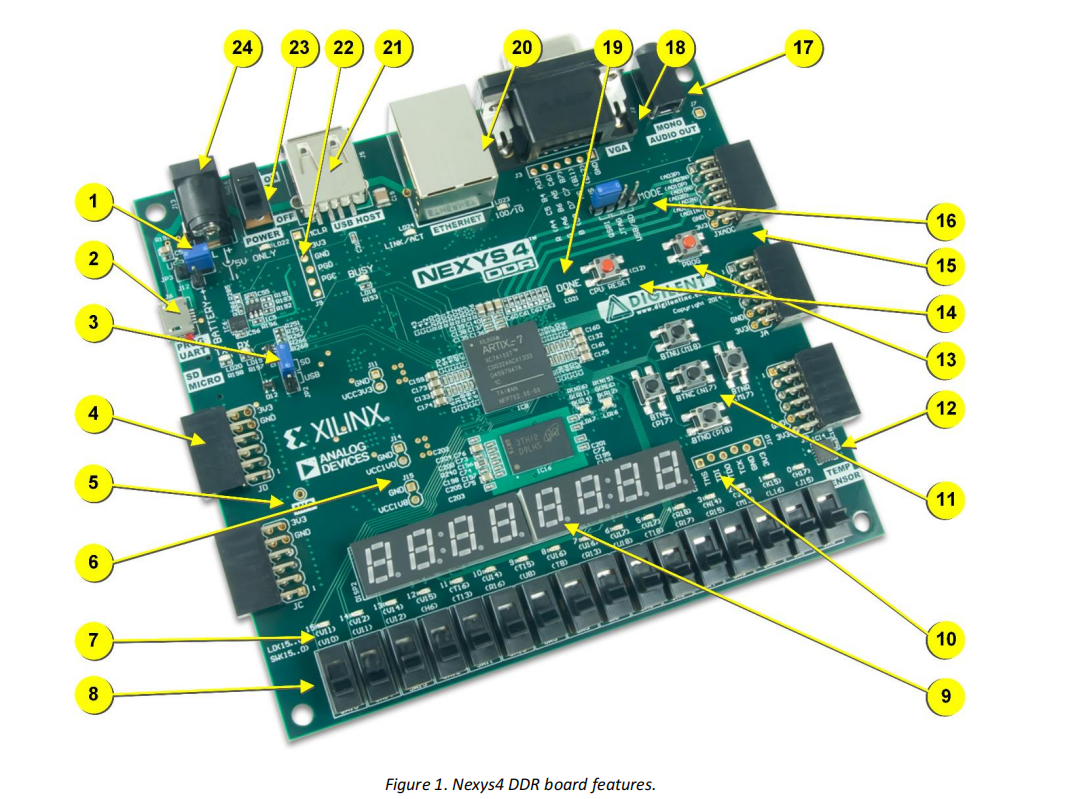

本代码已在Nexys4开发板验证,Nexys4开发板如下,其他开发板可以修改管脚适配:

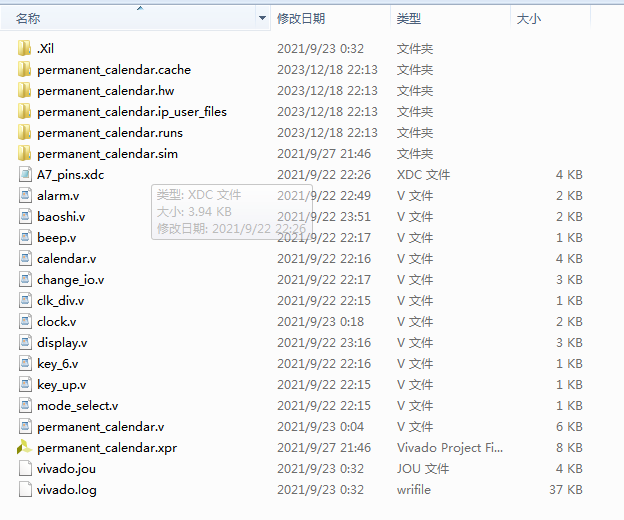

工程文件

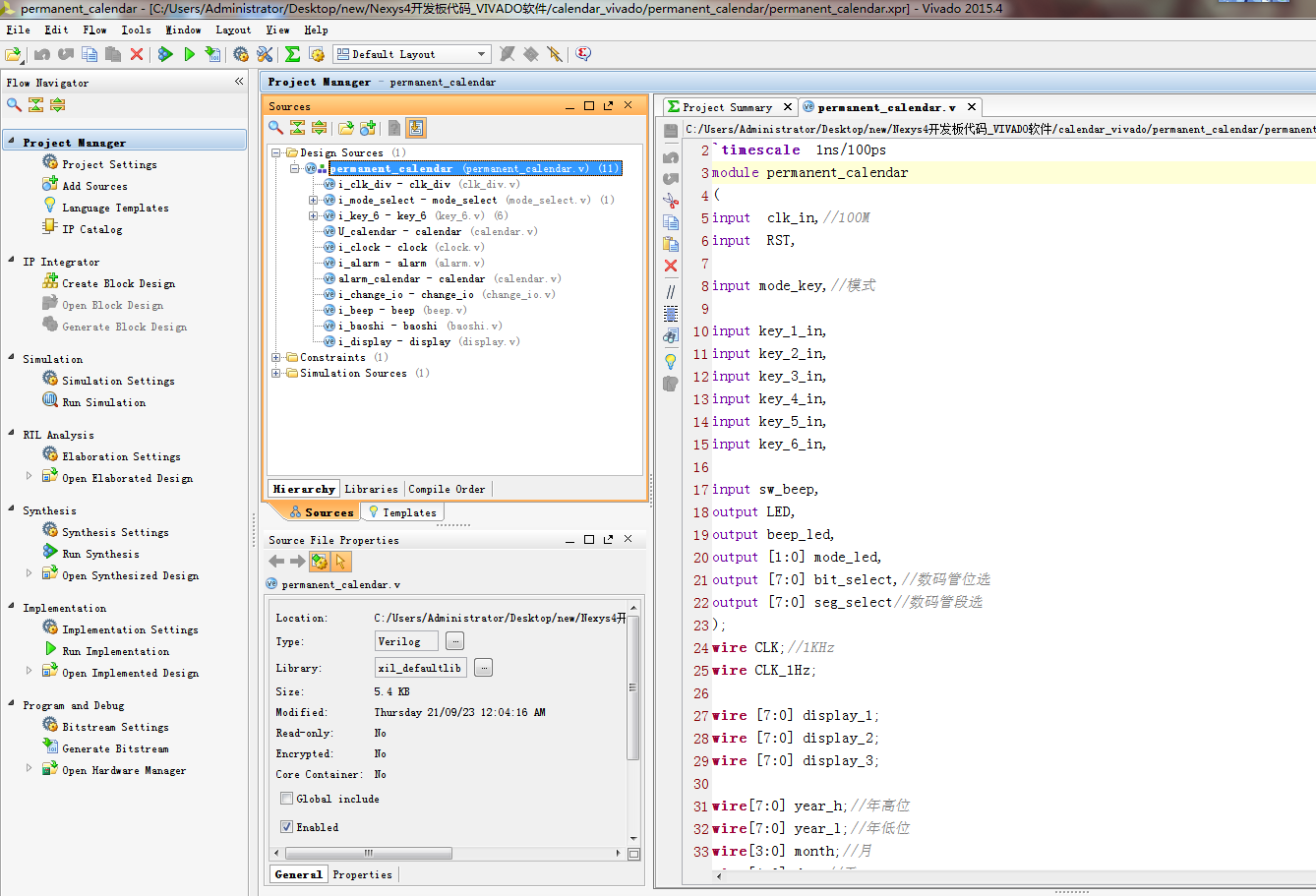

程序文件

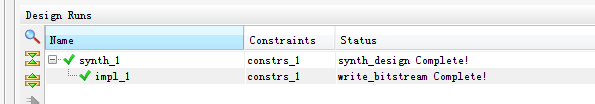

程序编译

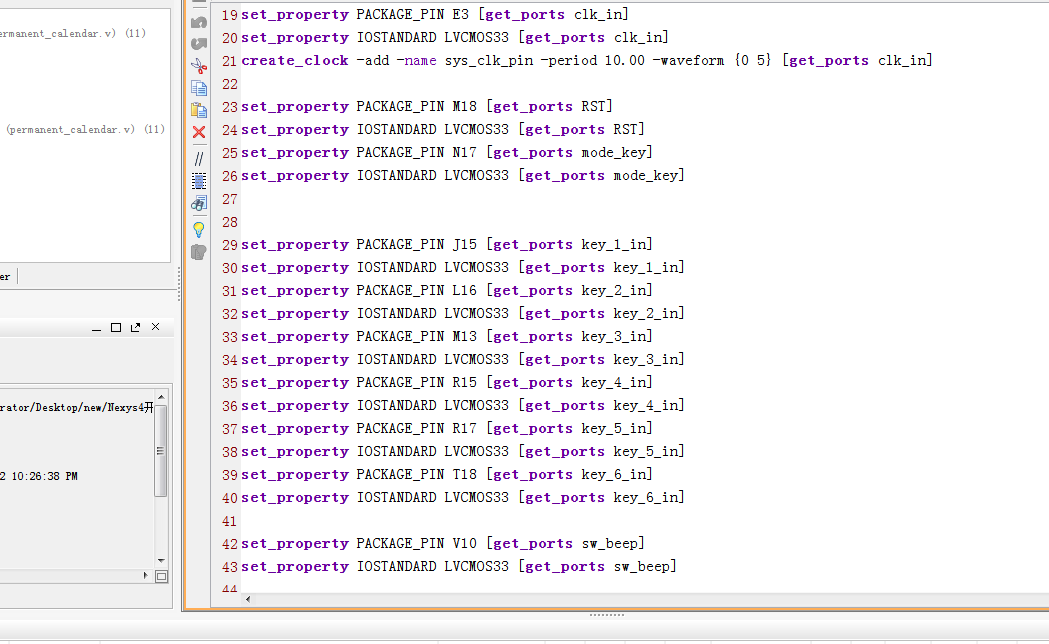

管脚分配

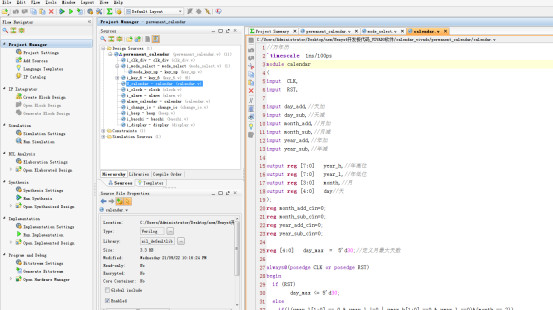

部分代码展示:

//万年历 `timescale 1ns/100ps module permanent_calendar ( input clk_in,//100M input RST, input mode_key,//模式 input key_1_in, input key_2_in, input key_3_in, input key_4_in, input key_5_in, input key_6_in, input sw_beep, output LED, output beep_led, output [1:0] mode_led, output [7:0] bit_select,//数码管位选 output [7:0] seg_select//数码管段选 ); wire CLK;//1KHz wire CLK_1Hz; wire [7:0] display_1; wire [7:0] display_2; wire [7:0] display_3; wire[7:0] year_h;//年高位 wire[7:0] year_l;//年低位 wire[3:0] month;//月 wire[4:0] day;//天 wire day_add;//天加 wire day_sub;//天减 wire month_add;//月加 wire month_sub;//月减 wire year_add;//年加 wire year_sub;//年减 wire [1:0] state; wire key_1; wire key_2; wire key_3; wire key_4; wire key_5; wire key_6; wire hour_add; wire minute_add; wire [7:0] hour_out;//小时 wire [7:0] minute_out;//分钟 wire [7:0] second_out;//秒 //分频模块 clk_div i_clk_div( . clk_in(clk_in),//100M . CLK_1Hz(CLK_1Hz), . CLK(CLK)//1KHz ); mode_select i_mode_select( . CLK(CLK), . RST(RST), . mode_key(mode_key), . state(state), . mode_led(mode_led) ); key_6 i_key_6( . CLK(CLK), . key_1_in(key_1_in), . key_2_in(key_2_in), . key_3_in(key_3_in), . key_4_in(key_4_in), . key_5_in(key_5_in), . key_6_in(key_6_in), . key_1(key_1), . key_2(key_2), . key_3(key_3), . key_4(key_4), . key_5(key_5), . key_6(key_6) ); wire day_cin; //万年历 calendar U_calendar ( . CLK(CLK),//1ms . RST(RST), . day_add(day_add | day_cin),//天加 . day_sub(day_sub),//天减 . month_add(month_add),//月加 . month_sub(month_sub),//月减 . year_add(year_add),//年加 . year_sub(year_sub),//年减 . year_h(year_h),//年高位 . year_l(year_l),//年低位 . month(month),//月 . day(day)//天 ); //时分秒 clock i_clock( . clk(CLK),//1ms . RST(RST),//高电平复位 . hour_add(hour_add),//小时加 . minute_add(minute_add),//分钟加 . day_cin(day_cin),//日增加 . hour_out(hour_out),//小时 . minute_out(minute_out),//分钟 . second_out(second_out)//秒 ); wire alarm_hour_add; wire alarm_minute_add; wire alarm_second_add; wire [7:0] alarm_hour_out;//小时 wire [7:0] alarm_minute_out;//分钟 wire [7:0] alarm_second_out;//秒钟 //闹钟时分秒 alarm i_alarm( . clk(CLK),//1ms . RST(RST),//高电平复位 . alarm_hour_add(alarm_hour_add),//小时加 . alarm_minute_add(alarm_minute_add),//分钟加 . alarm_second_add(alarm_second_add),//秒钟加 . alarm_hour_out(alarm_hour_out),//小时 . alarm_minute_out(alarm_minute_out),//分钟 . alarm_second_out(alarm_second_out)//秒钟 ); wire alarm_day_add;//天加 wire alarm_day_sub;//天减 wire alarm_month_add;//月加 wire alarm_month_sub;//月减 wire alarm_year_add;//年加 wire alarm_year_sub;//年减 wire [7:0] alarm_year_out;//年 wire [7:0] alarm_month_out;//月 wire [7:0] alarm_day_out;//日 //闹钟年月日 calendar alarm_calendar ( . CLK(CLK),//1ms . RST(RST), . day_add(alarm_day_add),//天加 . day_sub(alarm_day_sub),//天减 . month_add(alarm_month_add),//月加 . month_sub(alarm_month_sub),//月减 . year_add(alarm_year_add),//年加 . year_sub(alarm_year_sub),//年减 . year_h(),//年高位 . year_l(alarm_year_out),//年低位 . month(alarm_month_out),//月 . day(alarm_day_out)//天 ); change_io i_change_io( . CLK(CLK), . RST(RST), . state(state), . key_1(key_1), . key_2(key_2), . key_3(key_3), . key_4(key_4), . key_5(key_5), . key_6(key_6), // . year_l(year_l),//年低位 . month(month),//月 . day(day),//天 . day_add(day_add),//天加 . day_sub(day_sub),//天减 . month_add(month_add),//月加 . month_sub(month_sub),//月减 . year_add(year_add),//年加 . year_sub(year_sub),//年减 // . hour_out(hour_out),//小时 . minute_out(minute_out),//分钟 . second_out(second_out),//秒 . hour_add(hour_add), . minute_add(minute_add), // . alarm_hour_add(alarm_hour_add), . alarm_minute_add(alarm_minute_add), . alarm_second_add(alarm_second_add), . alarm_hour_out(alarm_hour_out),//小时 . alarm_minute_out(alarm_minute_out),//分钟 . alarm_second_out(alarm_second_out),//秒钟 // . alarm_day_add(alarm_day_add),//天加 . alarm_day_sub(alarm_day_sub),//天减 . alarm_month_add(alarm_month_add),//月加 . alarm_month_sub(alarm_month_sub),//月减 . alarm_year_add(alarm_year_add),//年加 . alarm_year_sub(alarm_year_sub),//年减 . alarm_year_out(alarm_year_out),//年 . alarm_month_out(alarm_month_out),//月 . alarm_day_out(alarm_day_out),//日 . display_1(display_1), . display_2(display_2), . display_3(display_3) ); //闹钟led提示模块 beep i_beep( .CLK(CLK),//1ms .RST(RST), .sw_beep(sw_beep),//关闹钟 .year_l(year_l),//年低位 .month(month),//月 .day(day),//天 .hour_out(hour_out),//小时 .minute_out(minute_out),//分钟 .second_out(second_out),//秒 .alarm_year_out(alarm_year_out),//年 .alarm_month_out(alarm_month_out),//月 .alarm_day_out(alarm_day_out),//日 .alarm_hour_out(alarm_hour_out),//小时 .alarm_minute_out(alarm_minute_out),//分钟 .alarm_second_out(alarm_second_out),//秒钟 .beep_led(beep_led) ); //整点报时 baoshi i_baoshi( . CLK(CLK), . RST(RST), . CLK_1Hz(CLK_1Hz), . hour_out(hour_out),//小时 . minute_out(minute_out),//分钟 . second_out(second_out),//秒 . LED(LED) ); //数码管显示模块 display i_display( . clk(clk_in), . display_1(display_1), . display_2(display_2), . display_3(display_3), . bit_select(bit_select),//数码管位选 . seg_select(seg_select)//数码管段选 ); endmodule

完整代码

扫描文章末尾的公众号二维码

3734

3734

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?