名称:分频器设计VHDL代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:VHDL

代码功能:

设计一个基于FPGA的分频器

设计要求

1.系统主要外设:自恢复式按键3个、共阴极数码管3个、系统时钟(50MH);

2.系统主要功能;三个按键分别控制分频器的开关和频率的增减,当开关按下时,输出频率为50MHz的方波,且频率可谓。可用增减按键控制输出频率,且由数码管显示当前输出方波频率。输出频率可调为25MHZ、50MHz、100MHZ、200MHz、500MHz

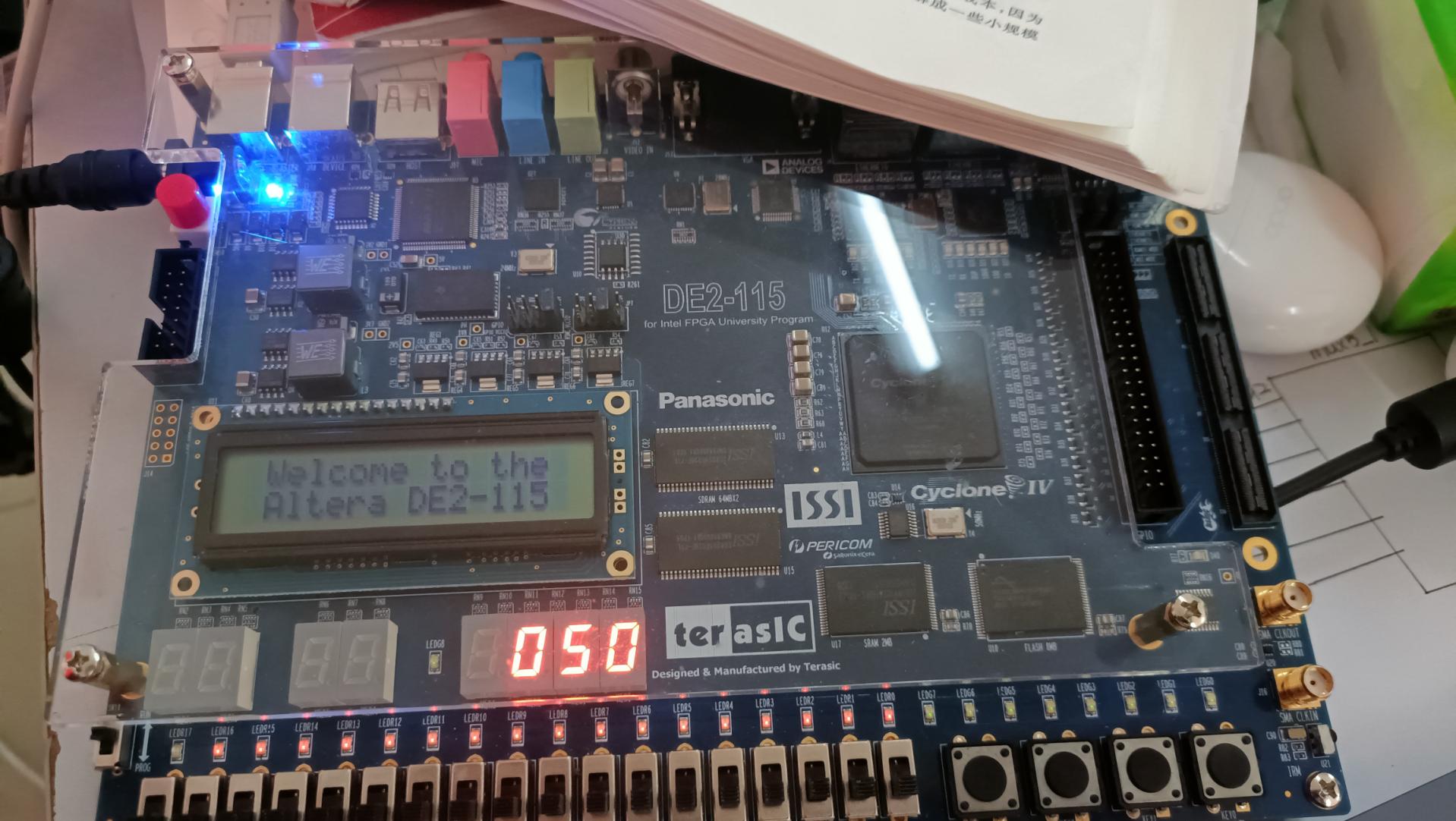

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

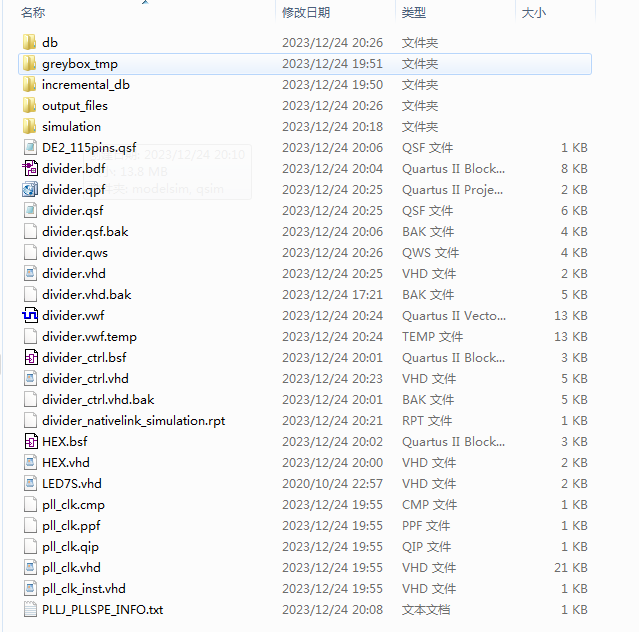

1 .工程文件

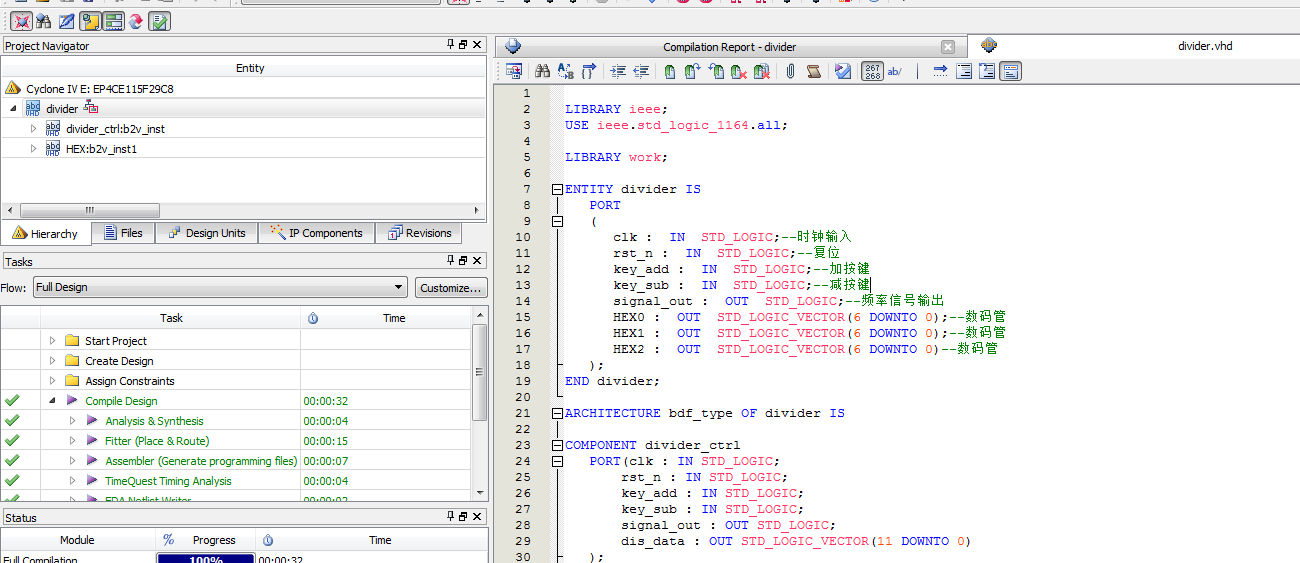

2. 程序文件

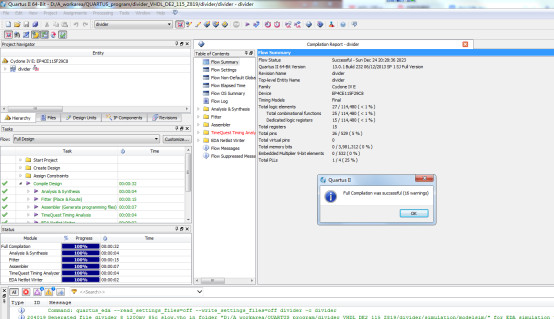

3. 程序编译

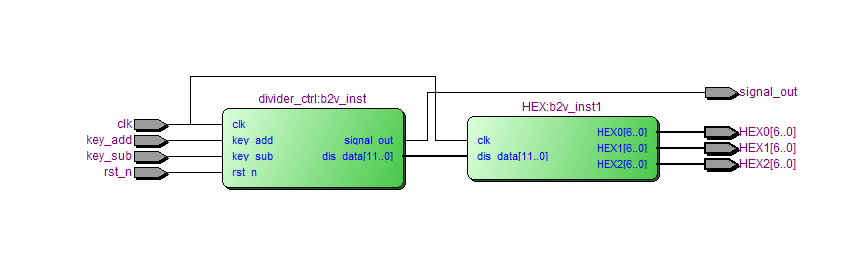

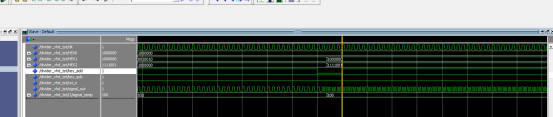

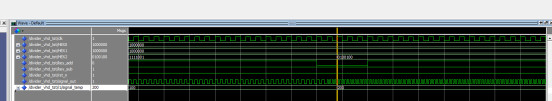

4. RTL图

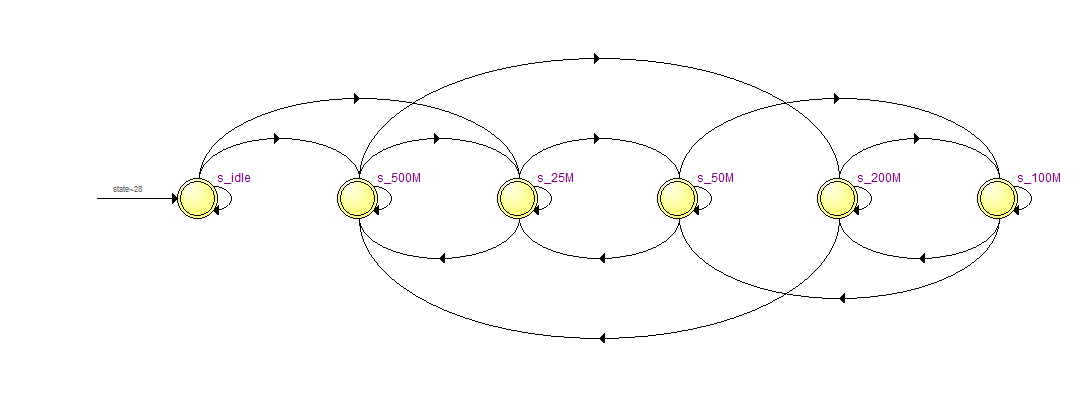

状态图

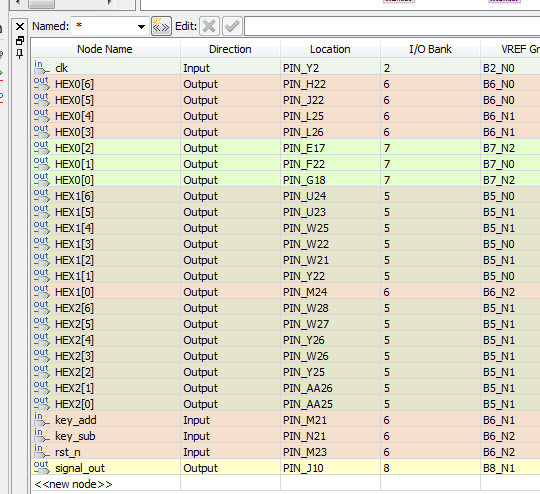

5. 管脚分配

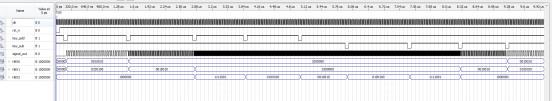

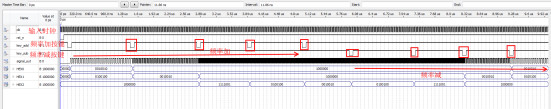

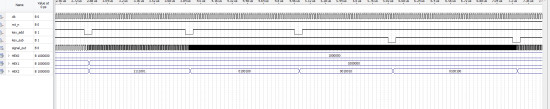

6. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY work; ENTITY divider IS PORT ( clk : IN STD_LOGIC;--时钟输入 rst_n : IN STD_LOGIC;--复位 key_add : IN STD_LOGIC;--加按键 key_sub : IN STD_LOGIC;--减按键 signal_out : OUT STD_LOGIC;--频率信号输出 HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管 HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管 HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)--数码管 ); END divider; ARCHITECTURE bdf_type OF divider IS COMPONENT divider_ctrl PORT(clk : IN STD_LOGIC; rst_n : IN STD_LOGIC; key_add : IN STD_LOGIC; key_sub : IN STD_LOGIC; signal_out : OUT STD_LOGIC; dis_data : OUT STD_LOGIC_VECTOR(11 DOWNTO 0) ); END COMPONENT; COMPONENT hex PORT(clk : IN STD_LOGIC; dis_data : IN STD_LOGIC_VECTOR(11 DOWNTO 0); HEX0 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ); END COMPONENT; SIGNALsignal_temp : STD_LOGIC_VECTOR(11 DOWNTO 0); BEGIN b2v_inst : divider_ctrl PORT MAP(clk => clk, rst_n => rst_n, key_add => key_add, key_sub => key_sub, signal_out => signal_out, dis_data => signal_temp);

源代码

点击下方的公众号卡片获取

894

894

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?