各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。上篇我们说到PCB的布局可根据功能、频率、信号类型划分,布局时考虑敏感信号远离噪声源。今天我们来看看多层板的常用叠层结构。

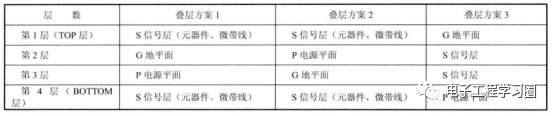

四层板的叠层结构

四层板的叠层结构包含1个电源平面、1个地平面和2个信号平面,这里列出了3种主流方案,叠层结构如下表所示:

四层板的叠层结构

1.叠层方案1:TOP、GND02、PWR03、BOTTOM此方案为目前业界主选叠层设置方案。TOP层下有完整的地平面,关键信号优先布在该层。且地平面和电源平面的厚度在5mil以下为最佳,以降低电源和地平面的分布阻抗。

2.叠层方案2:TOP、PWR02、GND03、BOTTOM类似方案1适用于主器件在BOTTOM层布局或关键信号底层布线的情况.

3.叠层方案3:GND01、S02、S03、GND04/PWR04方案3具有一定的屏蔽效果。但是电源平面和地平面距离过大,电源平面阻抗较大,且电源平面、地平面因元器件焊盘影响极不完整,信号阻抗不连续。

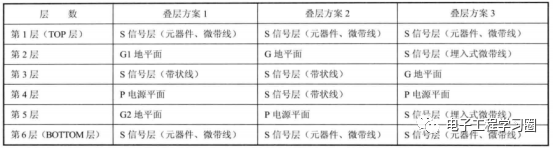

六层板的叠层结构

六层板的叠层结构一般包含1个电源平面、1个地平面和2个信号平面,这里列出了3种主流方案,如下表所示:

六层板的叠层结构

1.叠层方案1:TOP、GND02、S03、PWR04、GND05、BOTTOM此方案是目前业界主推的6层PCB的叠层设计方案,此方案有3个布线层,1个电源平面和2个地平面。第4、第5层电源平面和地平面之间的芯板厚度要尽可能小,第3层信号层是最优布线层,高速信号、敏感信号优先布置在该层。

2.叠层方案2:TOP、GND02、S03、S04、PWR05、BOTTOM当需要的布线层数多,对成本要求严格时,可以采用此方案。此方案有4个布线层,1个电源平面和1个地平面,在电源平面和地平面之间有2个信号层,间隔较大没有任何去耦作用,电源和地之间可适当添加去耦电容以降低电源和地之间的特性阻抗。第三层S03是最优布线层,高速信号、敏感信号优先布置在该层。

3.叠层方案3:TOP、S02、GND03、PWR04、S05、BOTTOM该方案也有4个布线层、1个电源平面和1个地平面,第3和第4层电源平面和地平面之间芯板厚度要尽量小,提供较好的去耦效果。但是第1和第2层,第5和第6层信号走线相邻,信号质量较差,走线时要注意交叉走线。靠近地平面的第2层是最优布线层。

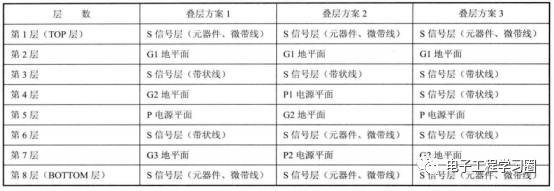

八层板的叠层结构

八层板的3种主流叠层结构如下面所示:

八层板的叠层结构分布

1.叠层方案1:TOP、GND02、S03、GND04、PWR05、S06、GND07、BOTTOM此方案是目前业界主推的8层PCB叠层方案,该方案有4个布线层,1个电源平面和3个地平面。该叠层结构,具有最优的信号完整性、电源完整性和EMC性能。第3层相邻2个地平面是最优的布线层,高速信号、敏感信号优先布置在该层。第4层和第5层距离要减小,有利于使第5层电源平面获得较低的平面阻抗。第2层和第7层都是地平面,可以作为高速信号的回流路径。

2.叠层方案2:TOP、GND02、S03、PWR1_04、GND05、S06、PWR2_07、BOTTOM此方案适用于板上电源种类多的情况,第3层和第6层为最佳布线层,降低第4和第5层间距。降低P2电源平面阻抗,尽量减少第8层信号走线,在第8层对第7层平面适当进行大面积敷铜处理。为兼顾PCB叠层对称,在TOP层也应进行适当的敷铜处理。

3.叠层方案3:TOP、GND1_02、S03、S04、PWR05、S06、GND2_07、BOTTOM此叠层方案有5个布线层,1个电源平面和2个地平面。此方案的电源和去耦效果很差,一般应用在布线层数要求多且成本控制严格的设计中,如消费类平板。第3层和第6层是较好的布线层。设计时应加大第3层和第4层的层间距,3、4层应交叉走线。

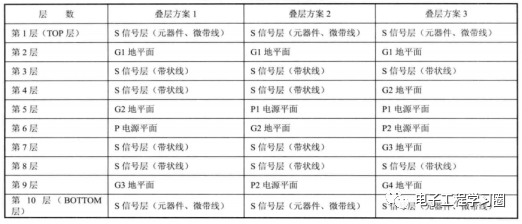

十层板的叠层结构

十层板的3种主流叠层结构如下面所示:

十层板的叠层结构

1.叠层方案1:TOP、GND1_02、S03、S04、GND2_05、PWR06、S07、S08、GND3_09、BOTTOM此方案有6个布线层、3个地平面和1个电源平面,对于单一电源平面的方案,优先采用此叠层结构。第3、4层是最优布线层,高速信号和时钟类敏感信号优先布置在该层。第5、6层之间芯板厚度尽量薄,以提高电源去耦效果。第3层和第4层,第7层和第8层采用交叉布线方式,并加大叠层的厚度。

2.叠层方案2:TOP、GND1_02、S03、S04、PWR1_05、GND2_06、S07、S08、PWR2_09、BOTTOM此方案有6个布线层,2个地平面和2个电源平面,对于需要考虑两种电源平面的叠层结构设计,优先考虑此方案。第3和第7层为最优走线层,减小第5层和第6层地平面之间芯板的厚度。第3层和第4层,第7层和第8层进行交叉走线,并加大两层之间的间距。为使第9层电源平面具有较好的去耦效果,可在第10层针对第9层的电源平面进行敷铜处理。

3.叠层方案3:TOP、GND1_02、S03、GND2_04、PWR1_05、PWR2_06、GND3_07、S08、GND4_09、BOTTOM此叠层方案包含4个走线层、4个地平面和2个电源平面层,适用于成本要求不高,EMC指标要求高且必须双电源供电要求的情况下。第3、8层是最优走线层,减小第6层和第7层,第4层和第5层之间的距离,以降低电源平面的特性阻抗。加大第5层和第6层电源平面的间距,以减弱平面间噪声的耦合。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

链接可在往期文章中找(在文章的最后有链接)~

本文详细介绍了四层板、六层板、八层板和十层板的常见叠层结构方案,强调了电源平面、地平面和信号平面的布局对信号完整性、电源完整性和EMC性能的影响。每个层次的布局考虑了优化布线层、去耦效果和敏感信号的布置,同时提供了不同层数PCB的叠层选择策略。

本文详细介绍了四层板、六层板、八层板和十层板的常见叠层结构方案,强调了电源平面、地平面和信号平面的布局对信号完整性、电源完整性和EMC性能的影响。每个层次的布局考虑了优化布线层、去耦效果和敏感信号的布置,同时提供了不同层数PCB的叠层选择策略。

828

828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?