- 建立工程

打开Modelsim

File->New->Project

弹出如下界面:

在Project Name中填写工程名,在Project Location中选择存放的路径,其余选择默认,最后点击OK。

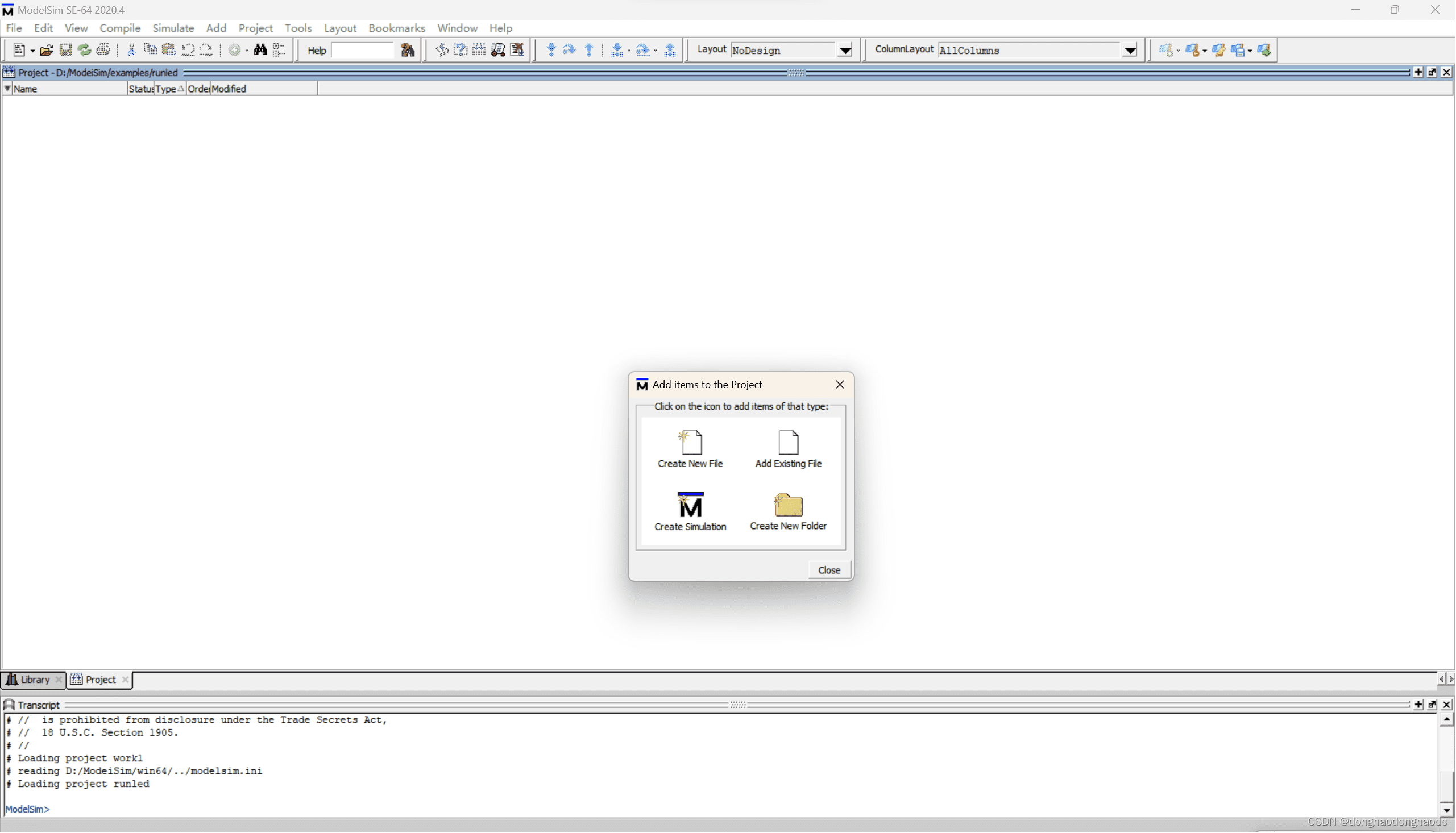

弹出以下界面:

有四个选项: Create New File(创建新文件)、Add Existing File(添加已有文件)、 Create Simulation(创建仿真)和 Create New Folder(创建新文件夹),这里可以选择 Create New File创建一个新的文件。

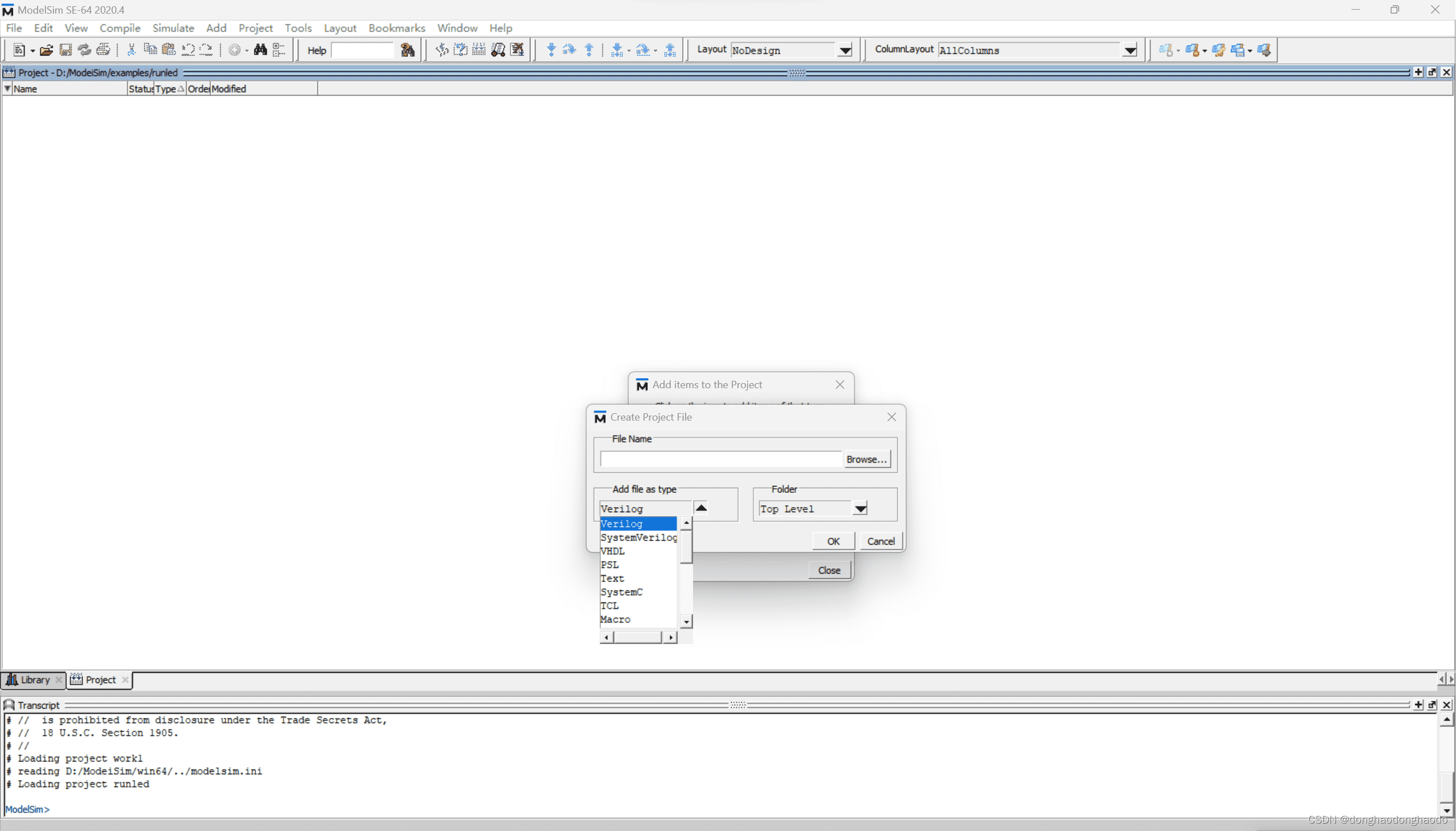

弹出以下界面:

在File Name中填写文件名称后,打开Add file as type的下拉菜单选择Verilog。

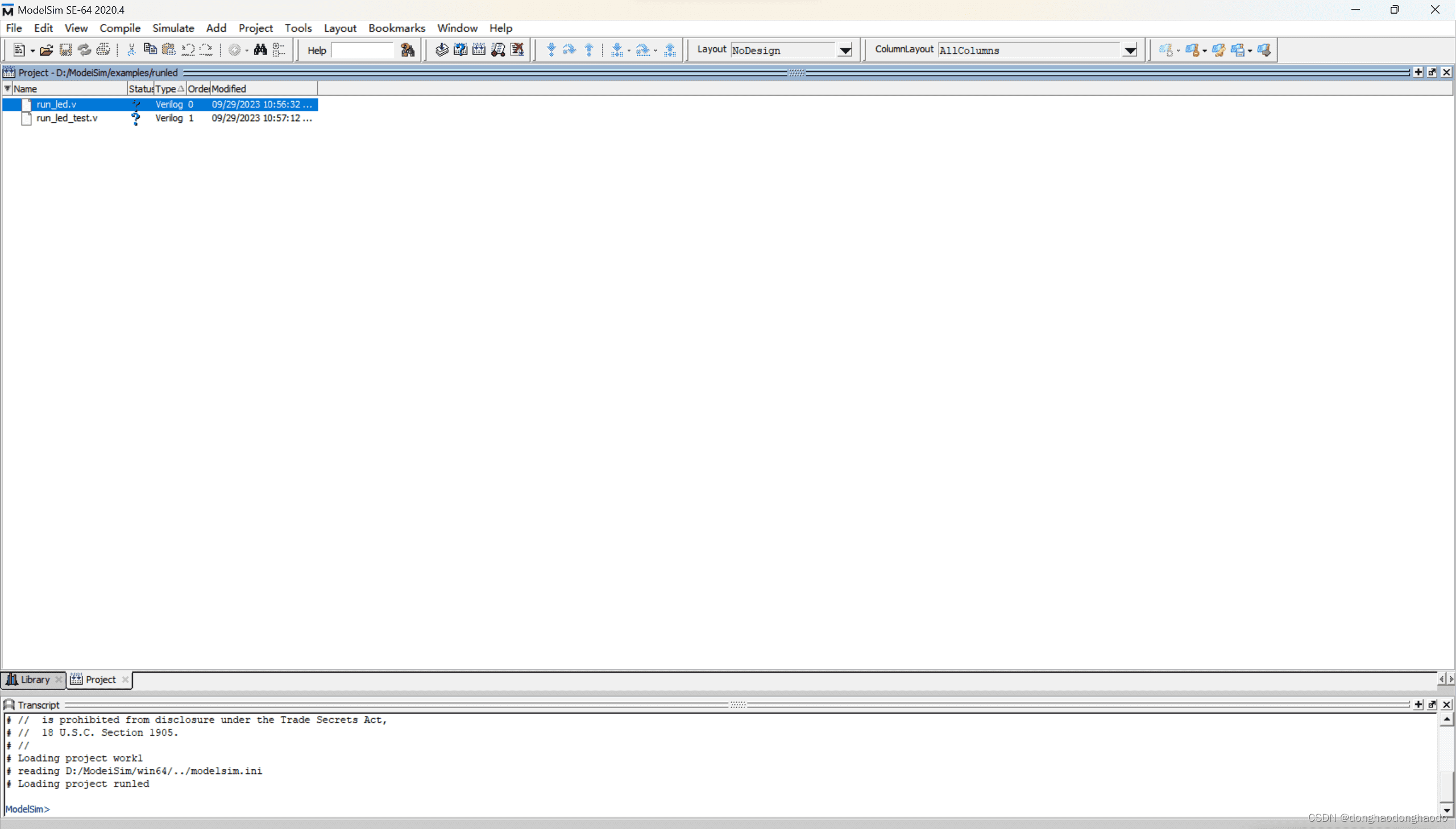

之后可以看到创建的文件:

双击文件名之后可以在右侧弹出的界面中编写代码:

- 编译文件

Compile->Compile All/Compile Selected

选择Compile All后可以编译所有文件,编译通过后会发现文件名后面的问号变成了对勾。

文件编译后“ Status”列可能会有三个不同状态。除了上图的用“√”表示的通过状态外,还有两个在设计中不希望出现的状态:编译错误(显示红色的“×”)和包含警告的编译通过(对号的后面会出现一个黄色的三角符号)。编译错误即Modelsim无法完成文件的编译工作。通常这种情况是因为被编译文件中包含明显的语法错误, Modelsim会识别出这些语法错误并提示使用者,使用者可根据Modelsim的提示信息进行修改。编译结果中包含警告信息是一种比较特殊的状态,表示被编译的文件没有明显的语法错误,但是可能包含一些影响最终输出结果的因素。

- 仿真

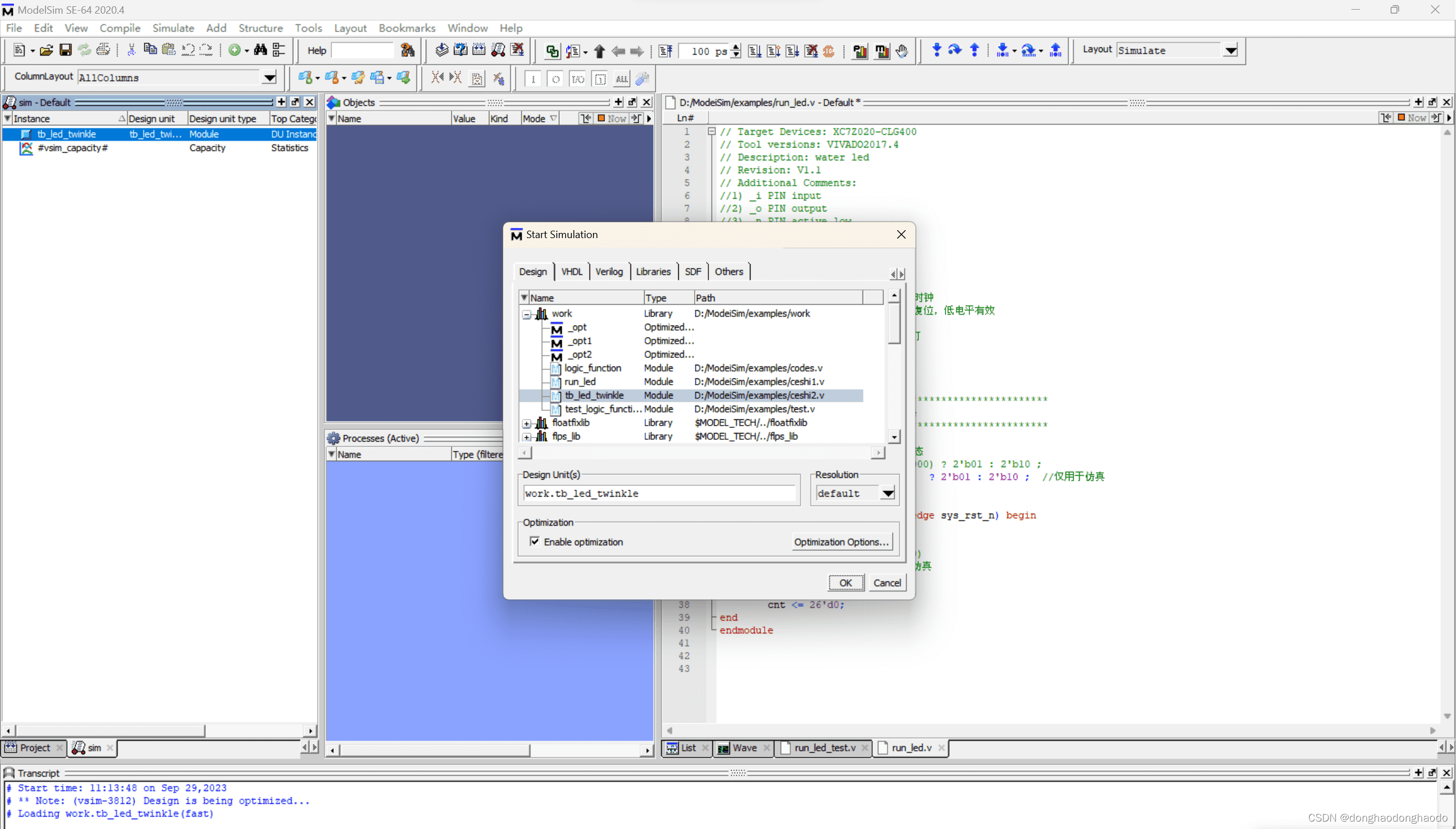

Simulate-> Start Simulation

弹出如下界面:

点击work前面的加号,会看到对应生成的模块,我们选择它再点击OK就可以了:

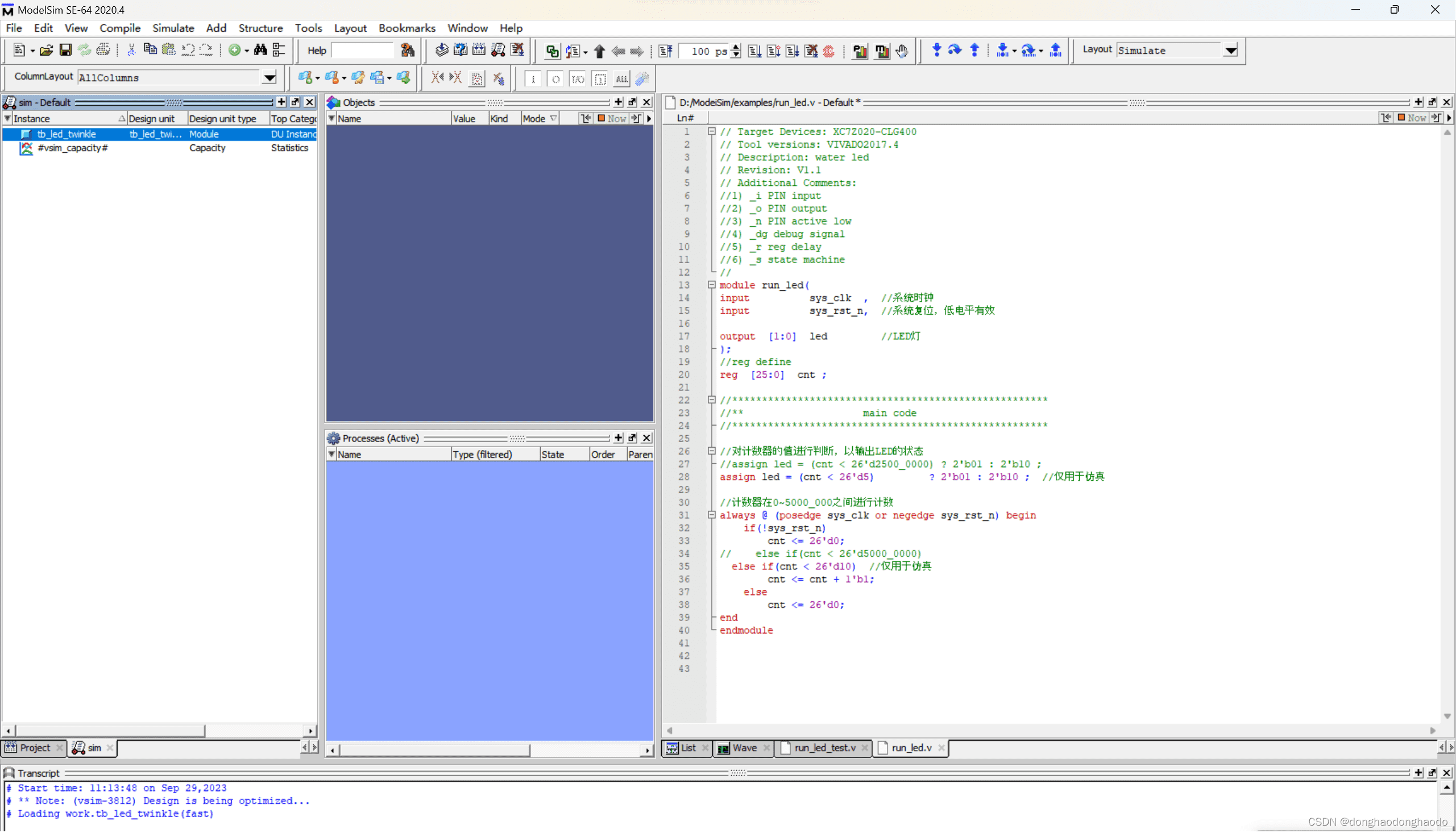

等待几秒后会自动弹出如下界面:

发现Objects和Process里面没有生成对应的模块,是空白的,不要慌,我们返回刚才的步骤,也就是如下界面:

我们打开Optimization Options:

可以发现刚刚默认选择的是No design object visibility,这里我们改选为第二行的Apply full visibility to all modules,然后点击OK继续仿真就可以了。

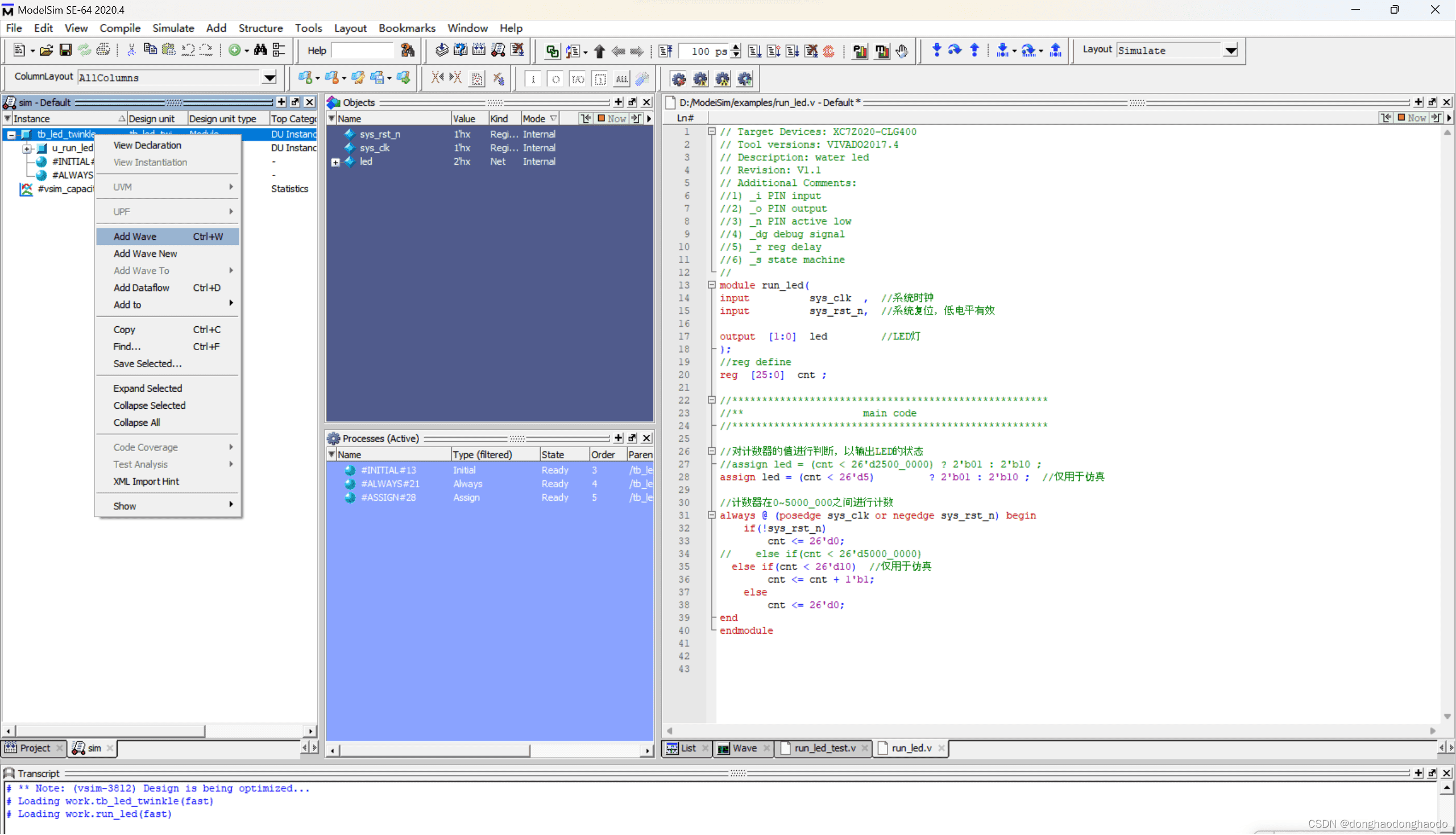

等待几秒后会再次弹出如下界面:

我们看到这时的Objects和Process里面出现了我们想要的对应生成的模块,接着鼠标右键单击“tb_led_twinkle” ,选择“Add Wave” 选项,如下图所示:

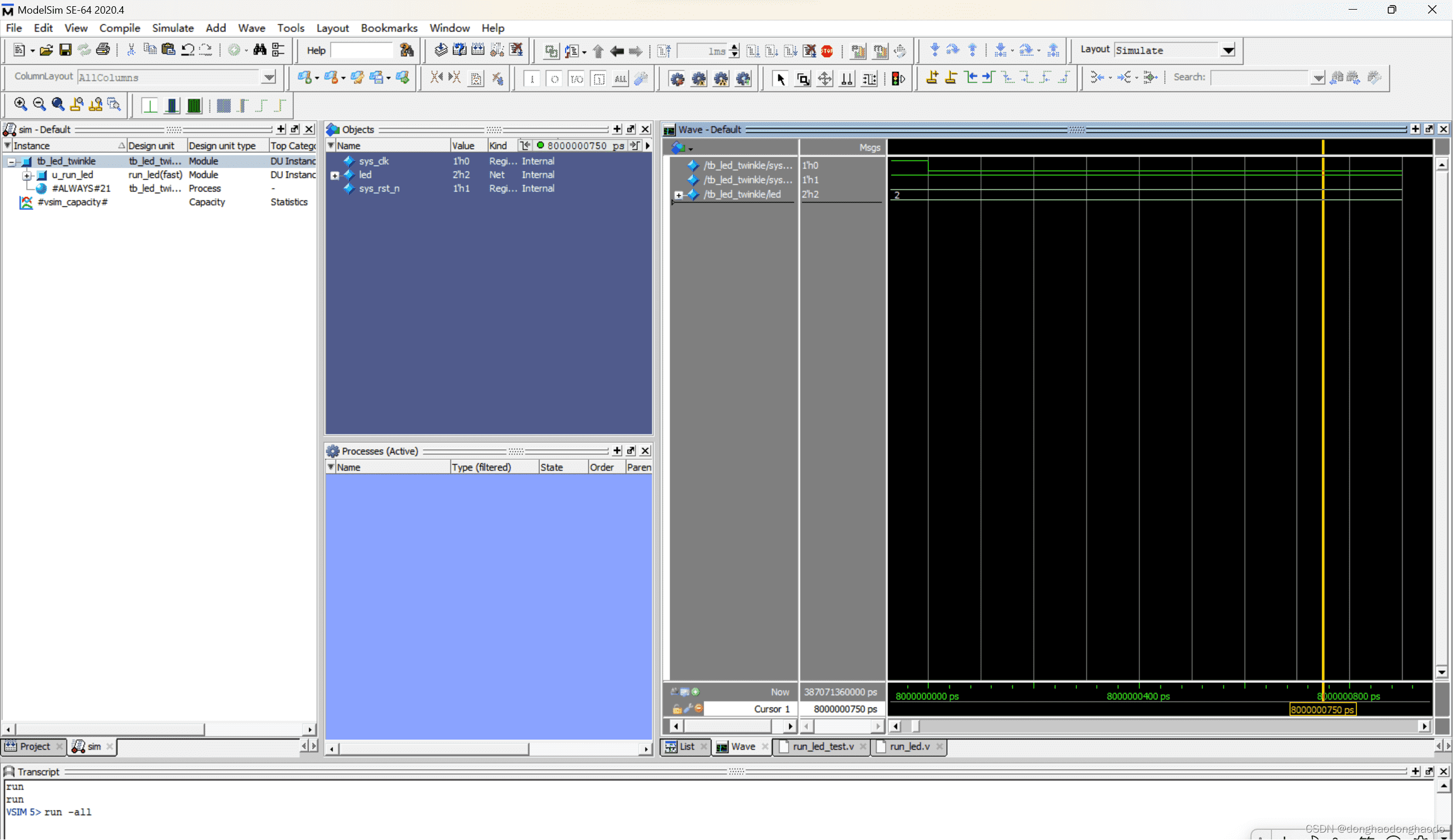

等待几秒后弹出右侧的波形窗口:

接下来单击Run

会发现仿真开始,波形出现:

这里再对几个观察波形的工具进行介绍:

前面的几个放大镜模样的工具是放大、缩小和全局显示功能,鼠标放到图标上会显示出它们的快捷键,后边的黄色图标是用来在波形图上添加用来标志的黄色竖线,紧跟着的是将添加的黄色竖线对齐到信号的下降沿和上升沿。

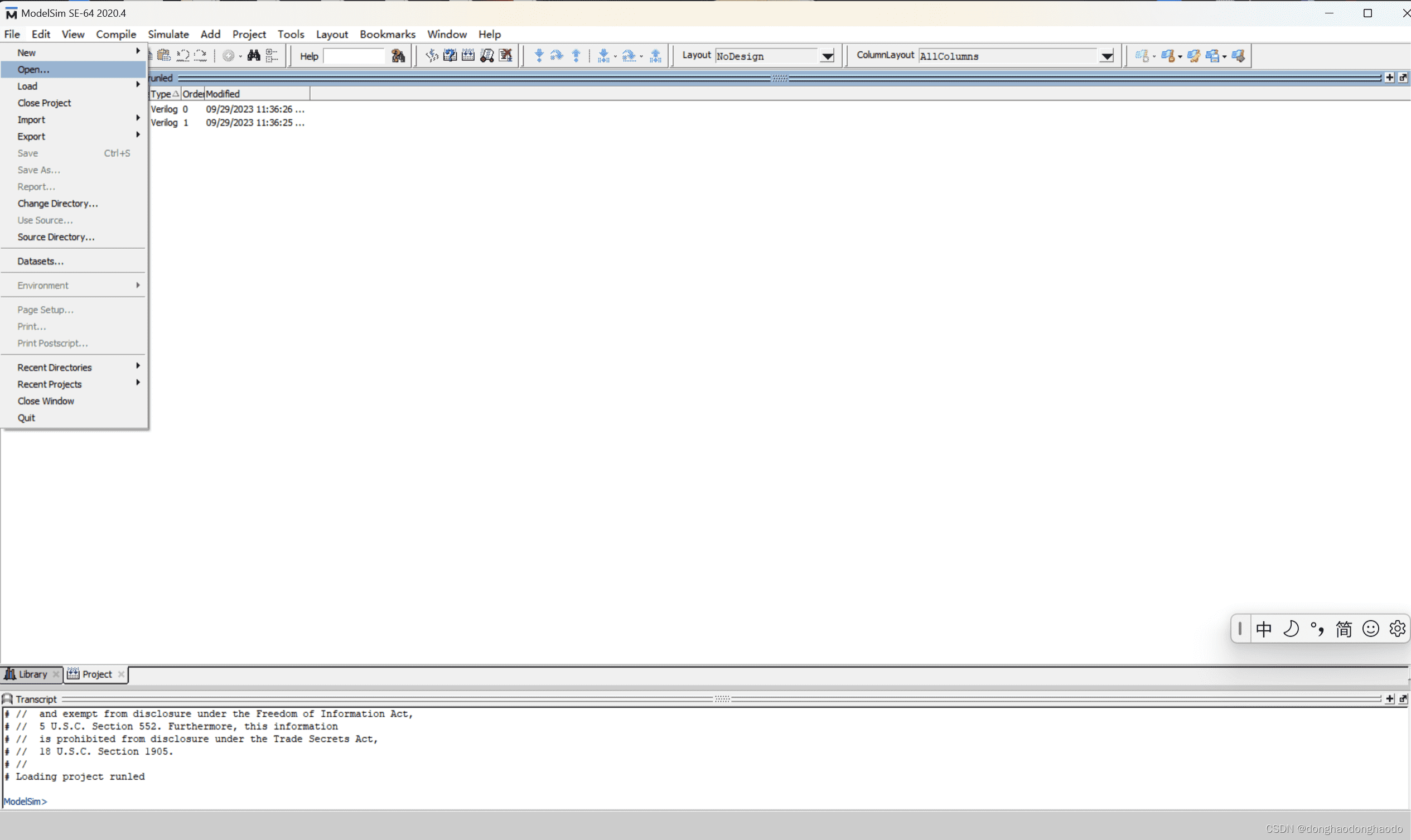

- 打开已经建立过的工程

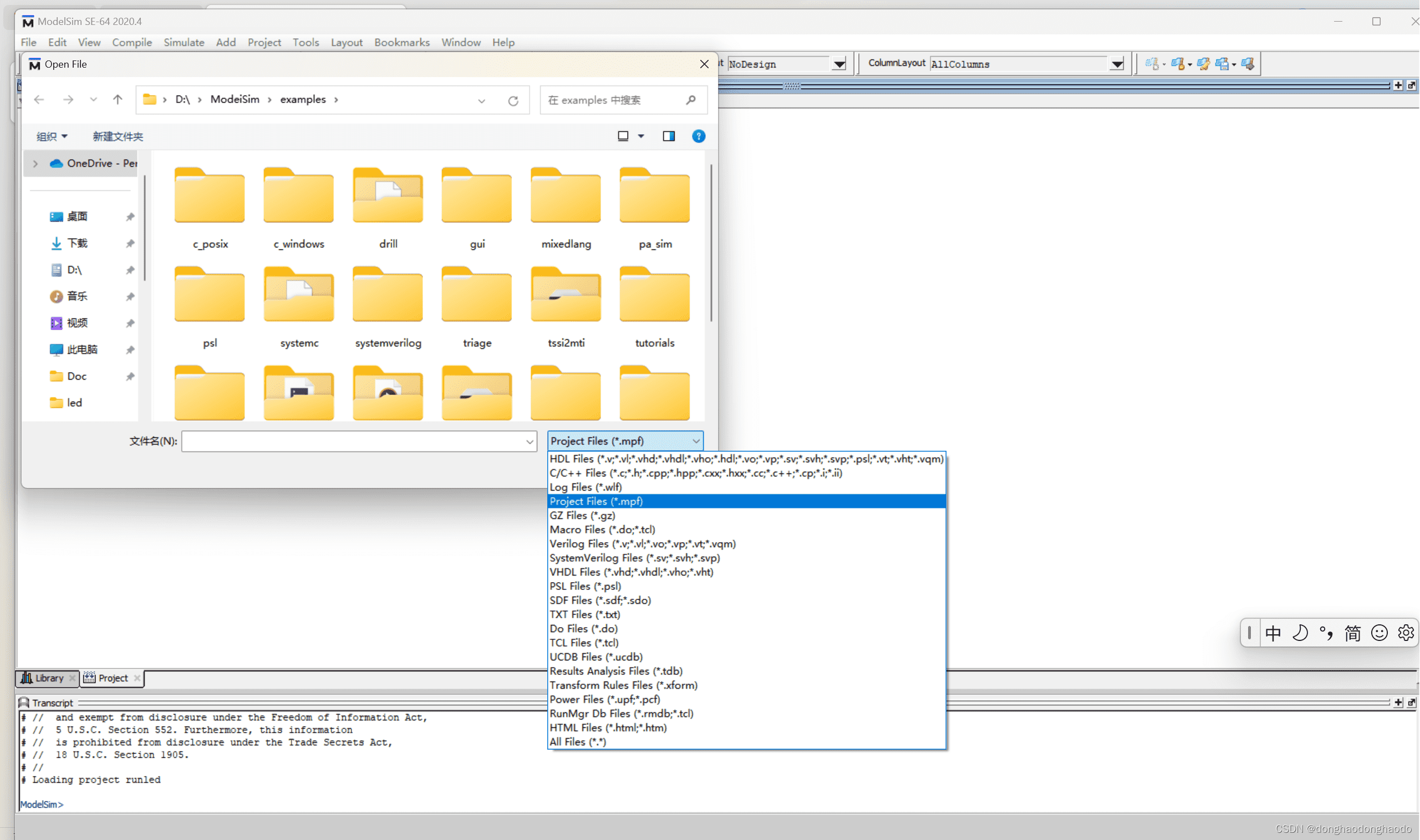

File->Open

在弹出的界面中选择.mpf格式:

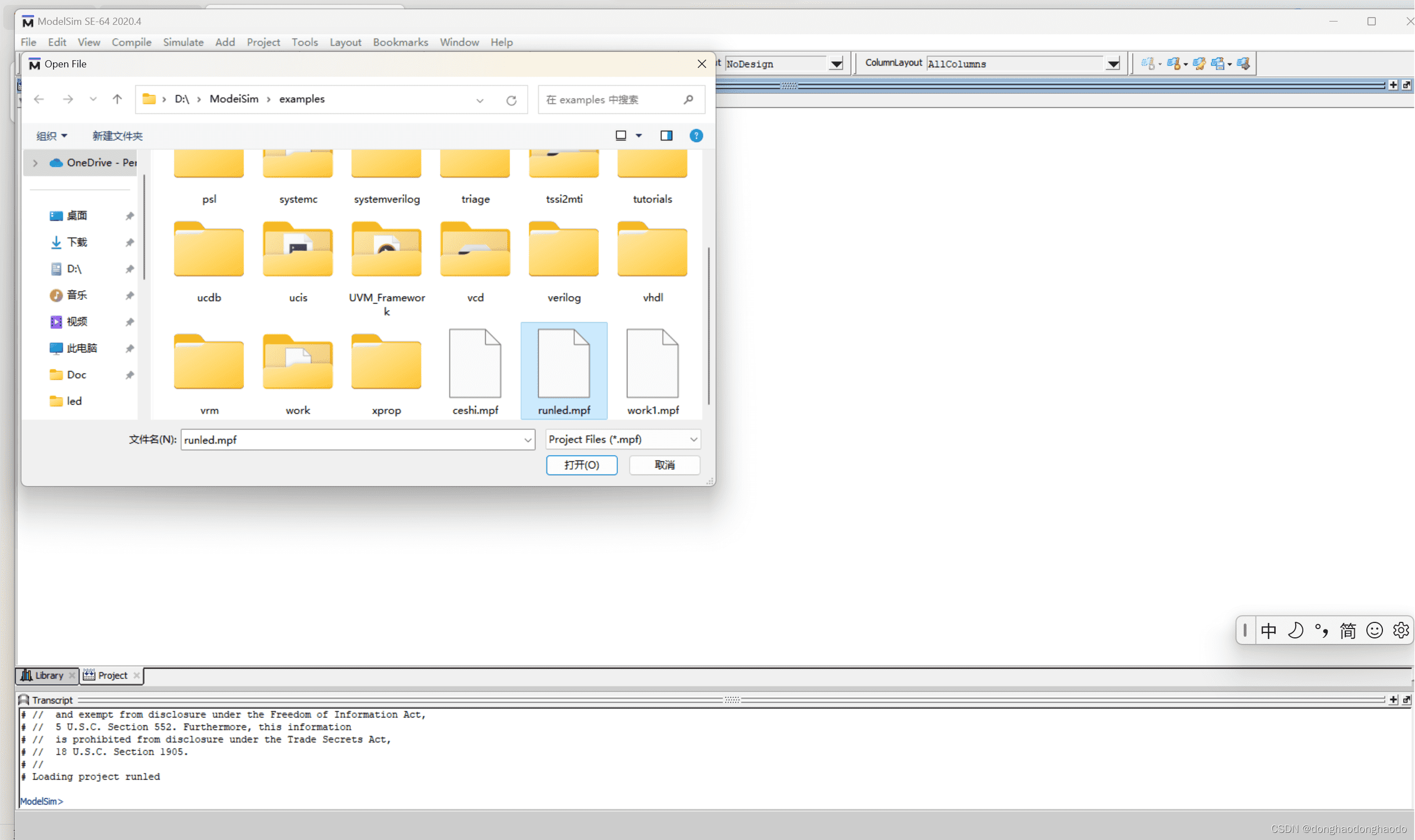

再选择我们之前建立的文件:

打开即可。

733

733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?