Verilog功能模块HDL设计完成后,并不代表设计工作的结束,还需要对设计进行进一步的仿真验证。掌握验证的方法,即如何调试自己的程序非常重要。在RTL逻辑设计中,要学会根据硬件逻辑来写测试程序即写Testbench。Verilog测试平台是一个例化的待测(MUT)模块,重要的是给它施加激励并观测其输出。逻辑块与其对应的测试平台共同组成仿真模型,应用这个模型就可以测试该模块能否符合自己的设计要求。

编写TESTBENCH的目的就是为了测试使用HDL设计的电路,对其进行仿真验证、测试设计电路的功能、性能与设计的 预期是否相符。通常,编写测试文件的过程如下:

● 产生模拟激励(波形)

● 将产生的激励加入到被测试模块中并观察其响应;

● 将输出响应与期望值比较。

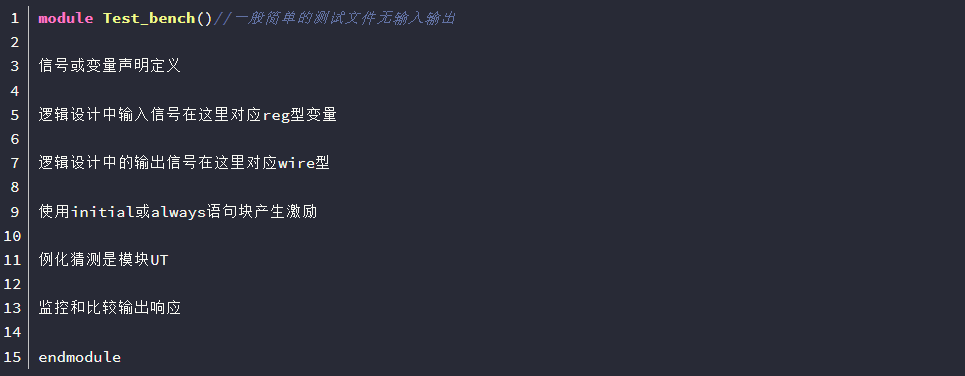

1. 完整的TESTBENCH文件结构

2. 时钟激励产生

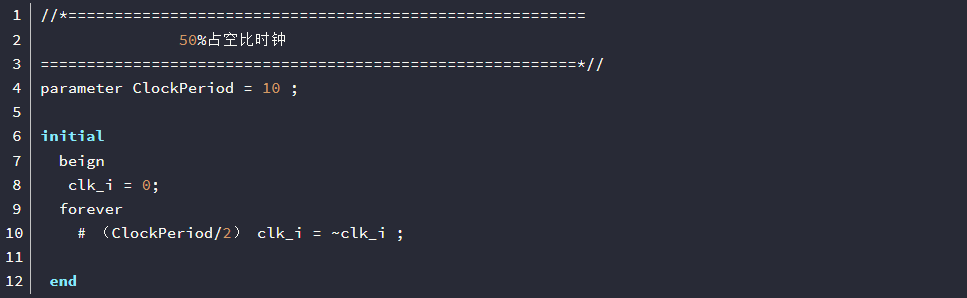

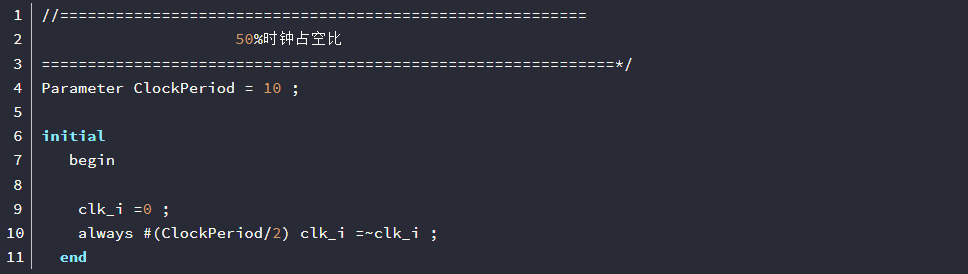

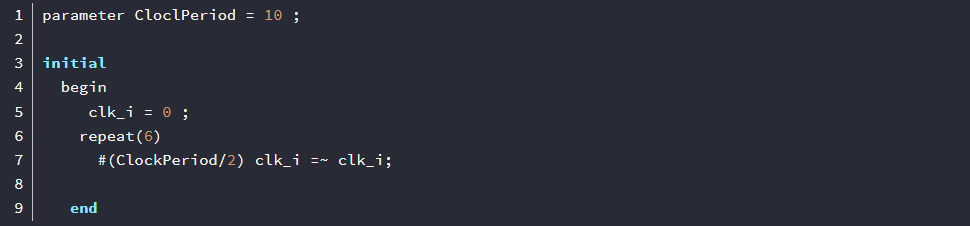

下面列举一些常用的生成时钟激励的方法:

方法一: forever

方法2: always块

方法3:产生固定数量的时钟脉冲

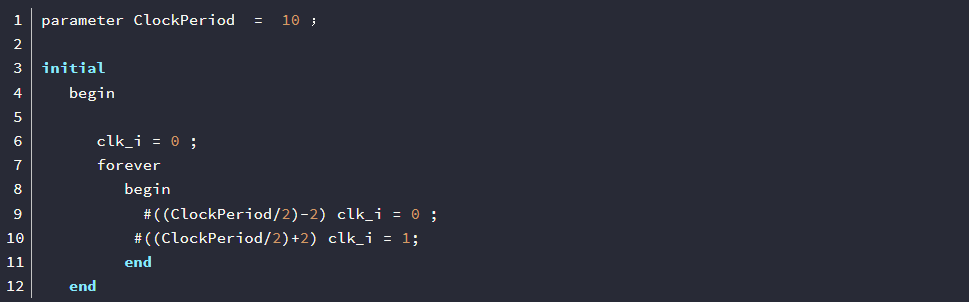

方法4:产生占空比非 50%的时钟

3. 复位信号设计

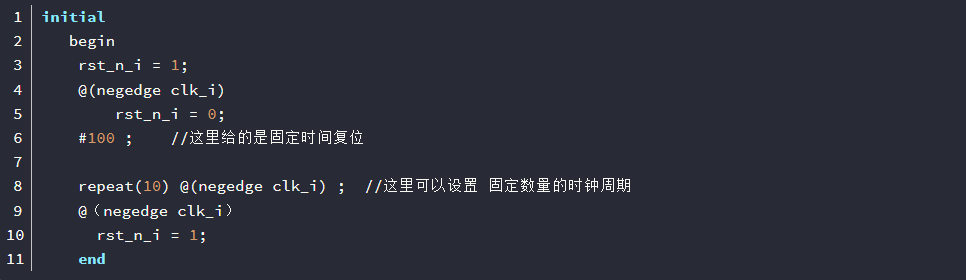

方法1:异步复位

方法2:同步复位

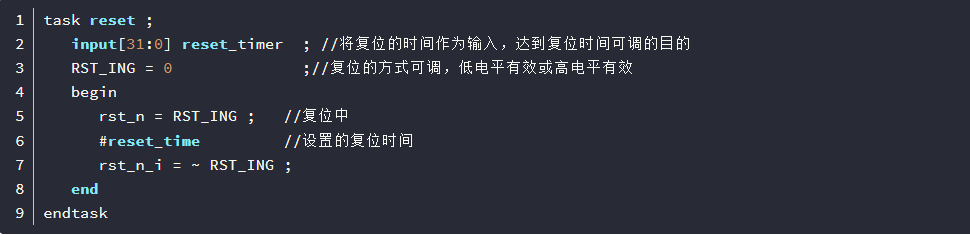

方法3:对复位进行任务封装

4. 双向信号设计

双向信号的描述方式并不唯一,常用的方法如下:

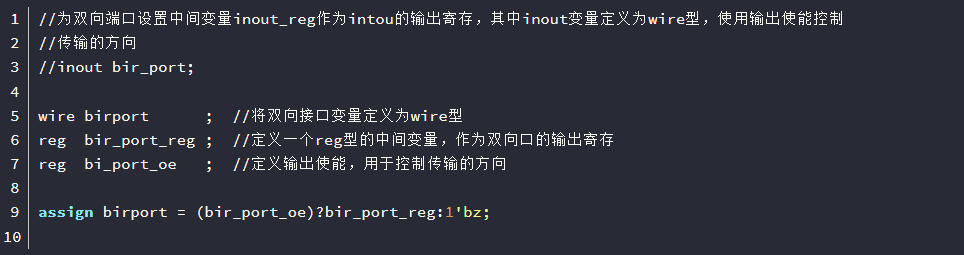

描述方式1: inout在testbench中定义为wire型变量

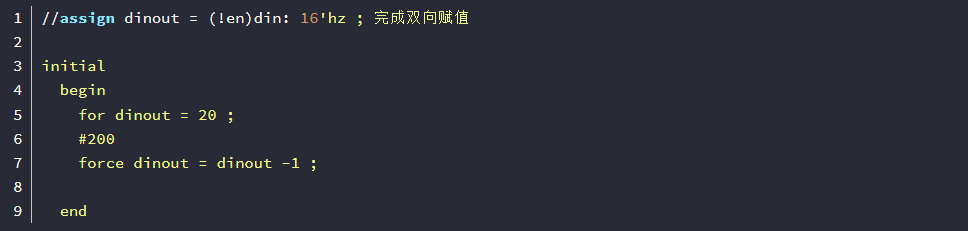

描述方式2:强制force

当双向端口作为输出端口时,不需要对其进行初始化,而只需开通三态门;当双向接口作为输入时,只需要对其初始化,并关闭三态门,初始化赋值需要使用wire数据,通过force命令来对双向端口进行输入赋值

5. 特殊信号设计

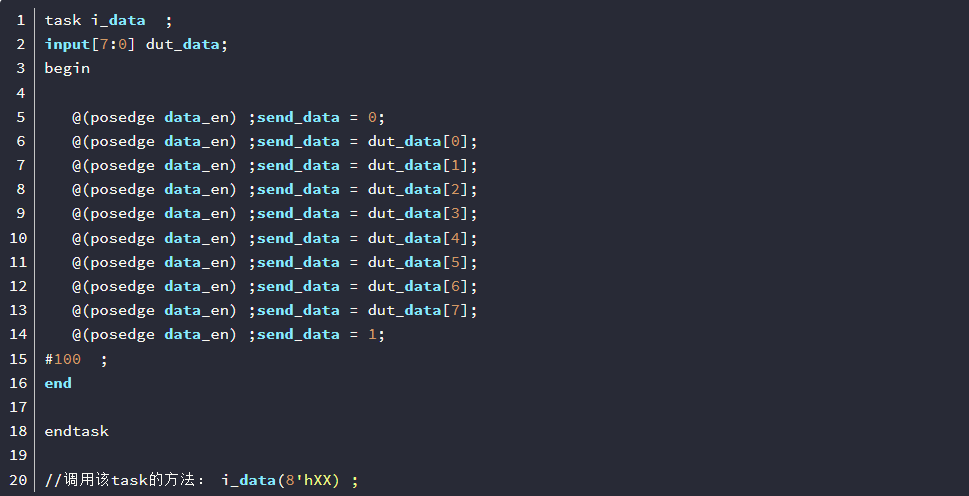

1.输入信号任务的封装

方便产生激励数据。

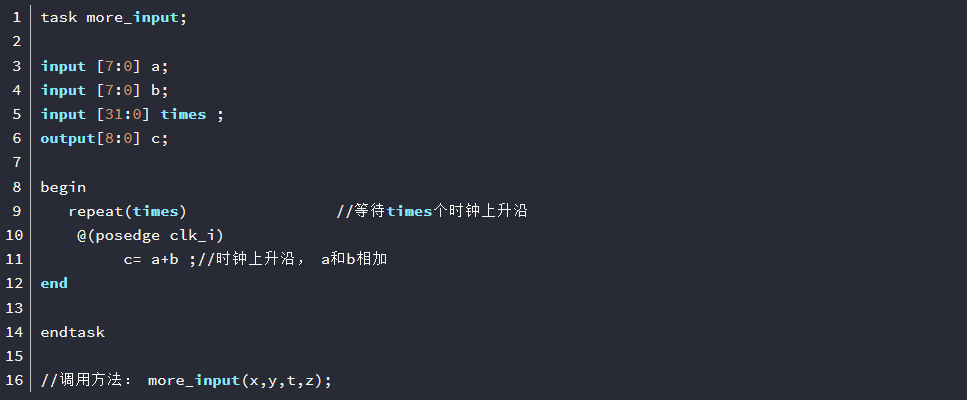

2. 多输入信号任务封装

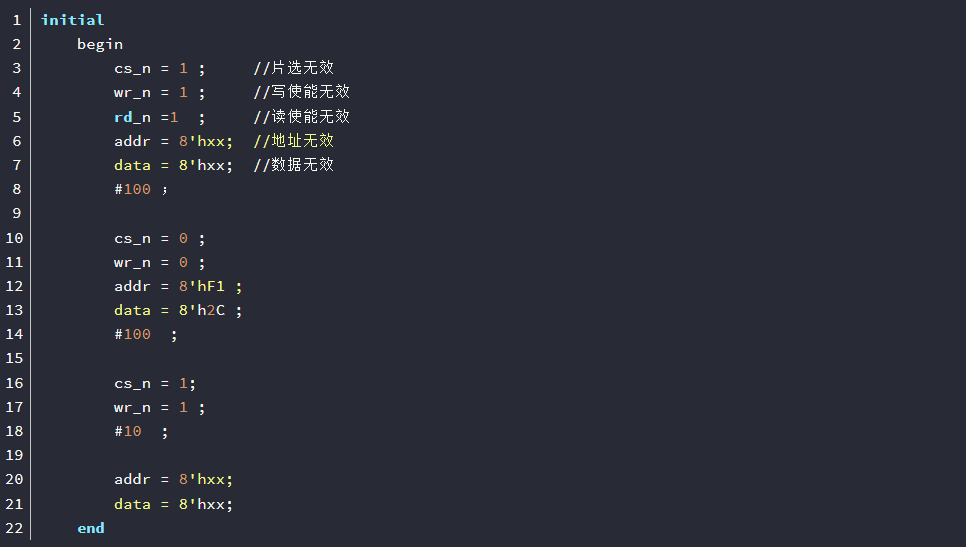

3. 输入信号产生,一次SRAM写信号产生

Testbench中的 @ 和 wait

//wait都是使用电平触发

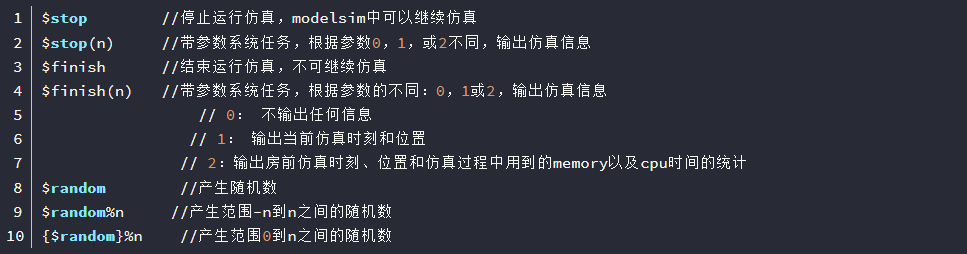

6. 仿真控制语句以及系统任务描述

仿真控制语句以及系统能够任务描述:

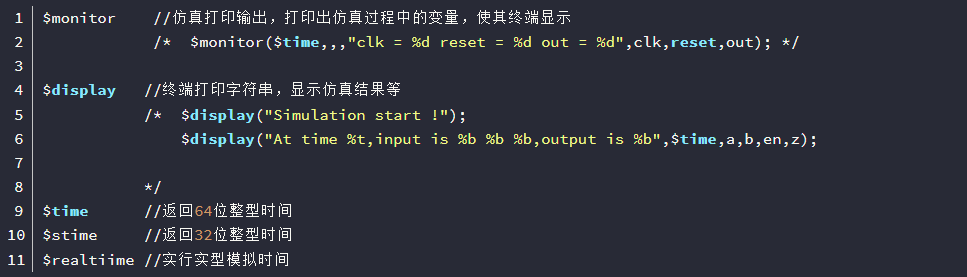

仿真终端显示描述

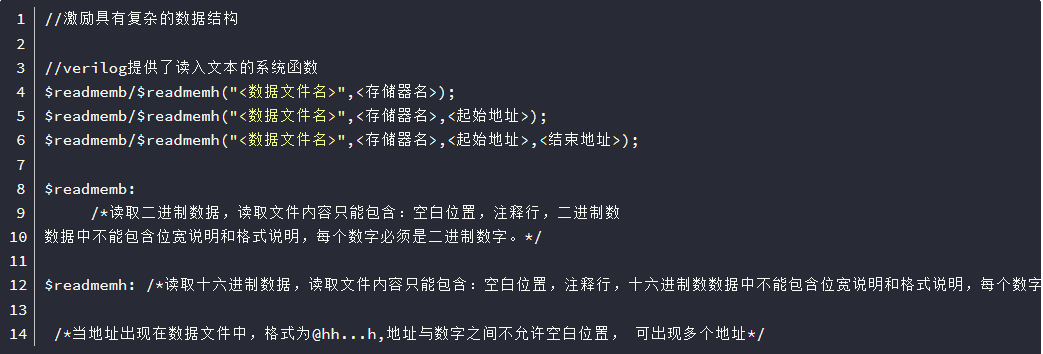

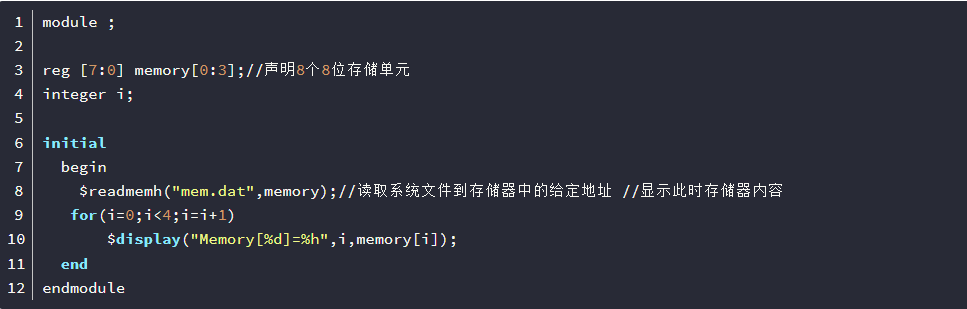

文本输入方式:$readmemb /$readmemh

mem.dat的文件内容格式:

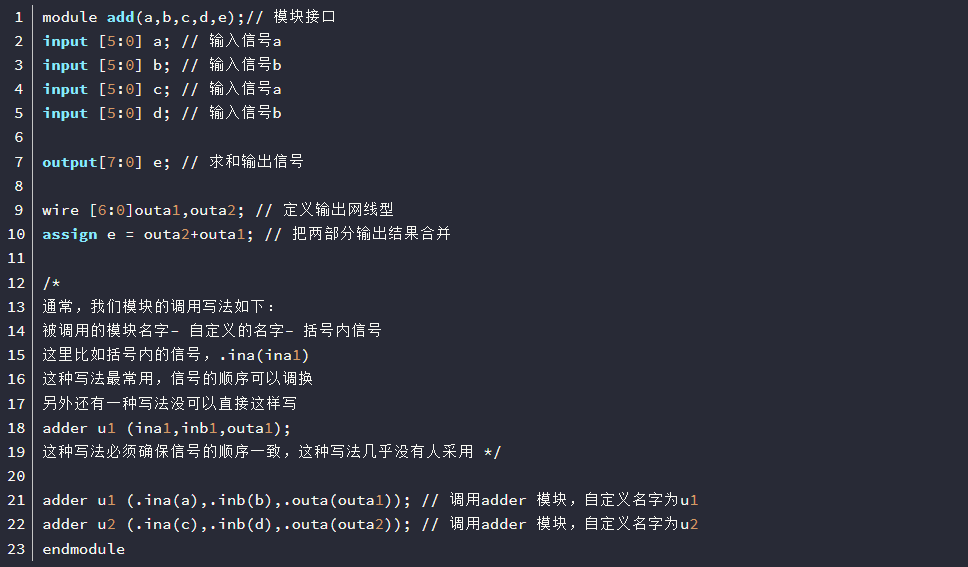

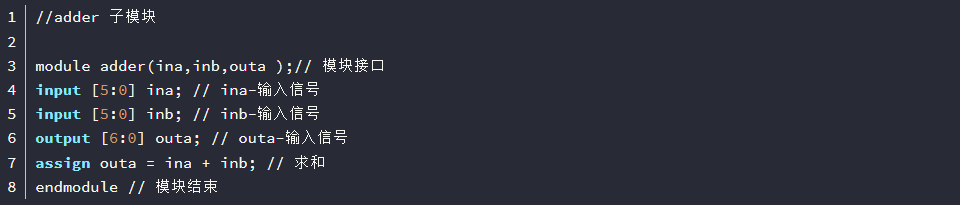

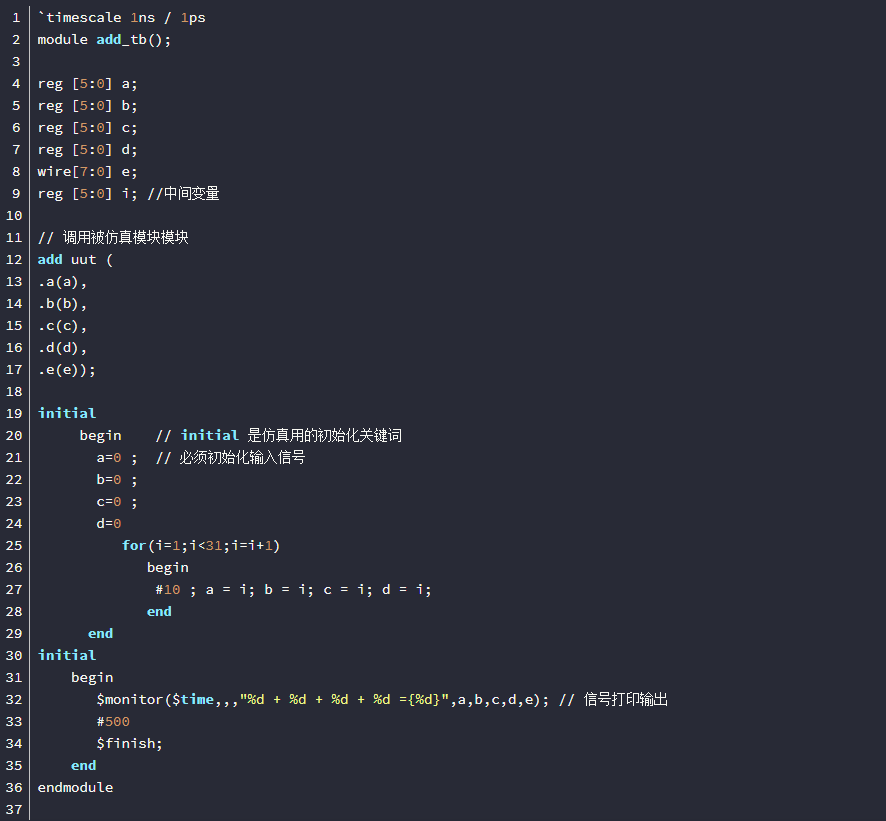

7. 加法器的仿真测试文件编写

上面只例举了常用的 testbench 写法,在工程应用中基本能够满足我们需求,至于其他更为复杂的 testbench写法,大家可参考其他书籍或资料。

这里提出以下几点建议供大家参考:

● 封装有用且常用的 testbench,testbench 中可以使用 task 或 function 对代码进行封装,下次利用时灵活调用即可;

● 如果待测试文件中存在双向信号(inout)需要注意,需要一个 reg 变量来表示输入,一个 wire 变量表示输出;

● 单个 initial 语句不要太复杂,可分开写成多个 initial 语句,便于阅读和修改;

● Testbench 说到底是依赖 PC 软件平台,必须与自身设计的硬件功能相搭配。

下面具体看一段程序:

仿真文件:

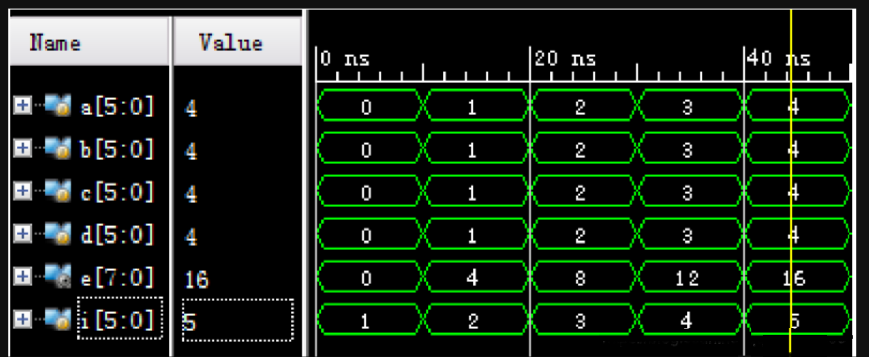

仿真波形:

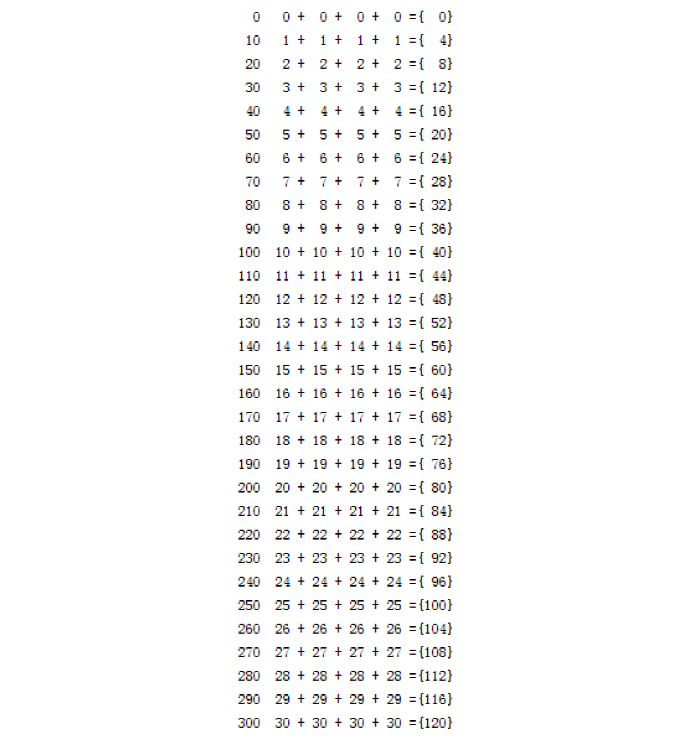

终端显示:

2767

2767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?