Sigrity XtractIM

1. 介绍

Cadence Sigrity XtractIM提供了一个专门针对IC封装应用程序完整的模型提取环境。该工具可以IBIS或SPICE电路网表格式生成IC封装的电气模型。这些简明的寄生模型可以是每引脚/网络RLC列表、耦合矩阵或Pi/T SPICE子电路。使用XtractIM创建的模型,可以快速评估封装的电气特性,并通过包括驱动器、接收器和其他互连来执行系统级信号和功率完整性仿真。XtractIM比其他方法快上一个数量级,还可生成精度更高、宽带更多封装模型。

2. 产品优势

- 可对整个封装或仅对所选网络提取模型

- 创建球栅阵列(BGA)、系统级封装(SiP)和引线框架封装模型

- 支持具有引线键合和倒装芯片管芯连接的设计

- 生成标准IBIS模型(带或不带耦合)

- 生成具有不对称PI或T电路的RLGC模型

- 生成具有可验证全波精度的紧凑型宽带型号

- 以表格和网表,或2D曲线和3D分布的形式检查RLC模型值

- 通过时域电路仿真确保宽带模型兼容性

- 生成HTML格式的电气性能评估报告

3. 产品特征

3.1 全波精度

与准静态RLGC封装提取工具相比,XtractIM是基于从全波混合解算器获得的S参数提供RLGC寄生参数。数值解算器包括所有物理效应,如网络、过孔、引线键合、焊球/焊点和任意形状的平面。解算器还考虑到所有耦合机制,其中包括了网络到网络、网络到平面、平面到平面、以及键合到键合。大容量解算器使XtractIM工具能够从单次仿真中生成整个封装模型,从而通过包含所有返回路径效应提高准确性。全波解算器提供了能够提取正确表现非对称物理结构的电路网表,以获得更高的模型精度和更大的带宽。

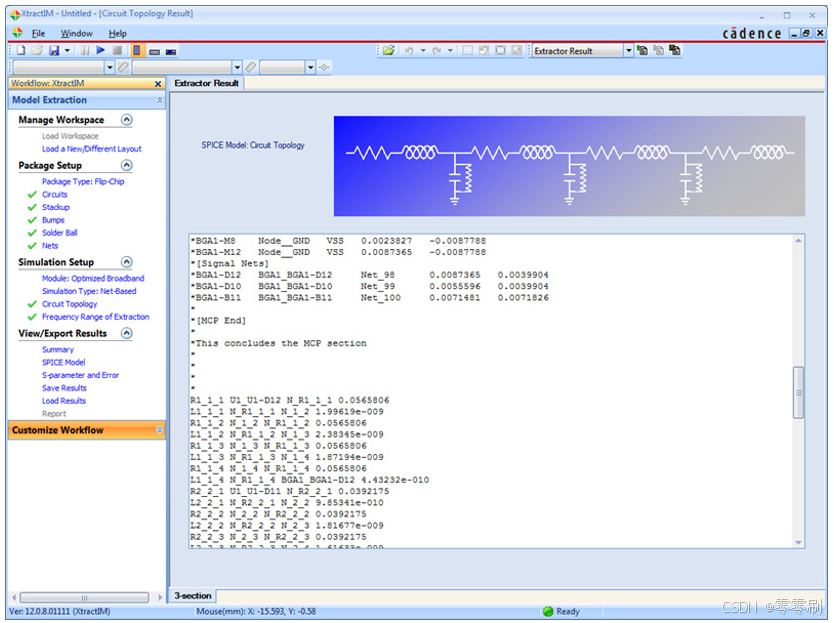

图 1 紧凑型宽带SPICE模型

3.2 全面的封装支持

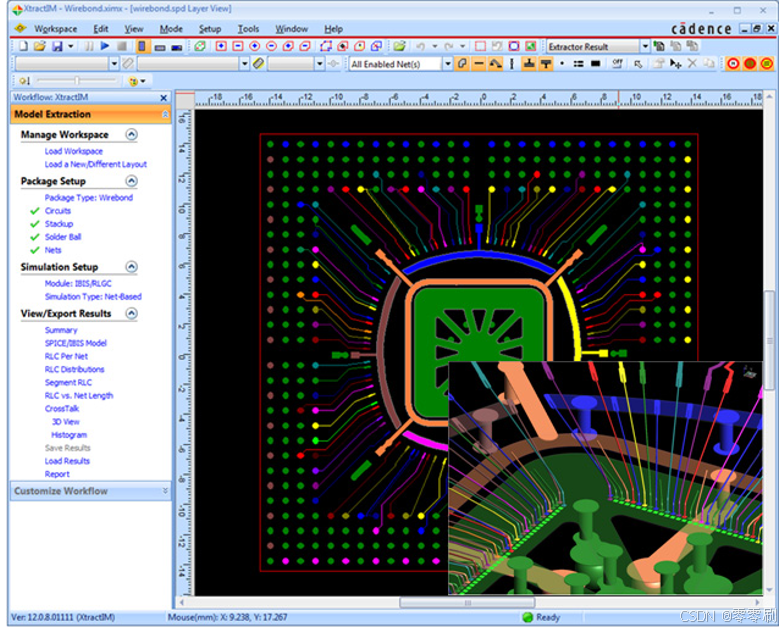

XtractIM支持多种IC封装类型,包括BGA和引线框架。该工具还支持用于单芯片和SiP的引线键合和倒装芯片管芯连接方式的实现。多芯片设计可包括堆叠、并排和叠加的方法。可以对整个封装或选定的网络提取模型。XtractIM模型可以包含离散器件(如封装上去耦电容器),从而更准确地反映封装供电系统以及电源、接地和信号网之间的耦合。这对于同步开关输出(SSO)/同步开关噪声(SSN)分析尤其重要。

图 2 直观的检查表工作流程和3D浏览对引线键合封装的提取进行引导

3.3 宽带频率支持

XtractIM是唯一可提供宽带多级优化模型的专用封装提取解决方案。这些模型在指定的频率范围内提供了可验证的准确性,并填补了IBIS/RLGC和全波S参数之间的差距。凭借其紧凑的尺寸(通常为S参数或零极点模型的2%),可从高效的时域仿真中受益。这些宽带模型的电路拓扑无疑保证了无源性、因果性和适当的直流行为。通过对RLC元件值的XtractIM优化来拟合宽带全波结果的方法明显比依赖于为多级电路分配单独的R、L、C静态值进行估算的方法更准确。

3.4 易于掌握的工作流程

XtractIM具有一套易于使用的工作流程,其可以协助设置诸如堆叠检查、C4凸块和焊球创建、信号和电源/接地网络选择、以及定义其他提取参数。该引导能够确保提取模型能够精确反映的目标。可以从分步流程的菜单中选择RLGC或宽带模型选项。XtractIM对用于查看结果和分析所有网络间RLC分布提供了多种选择。为适应特定应用目的可以以多种格式导出提取模型。

4. 集成方面

- 可用于Windows和Linux

- 具有面向Cadence、Mentor Graphics、Zuken和AutoCAD的IC封装布局数据库接口

- 具有引线框设计自定义选项的DXF导入实用程序

- 具备用于电路模型连接的输出模型连接协议(MCP)和芯片封装协议(CPP)

本文章是博主花费大量的时间精力进行梳理和总结而成,希望能帮助更多的小伙伴~ 🙏🙏🙏

后续内容将持续更新,敬请期待(*^▽^*)

欢迎大家评论,点赞,收藏→→→

230

230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?