VIVADO建立工程

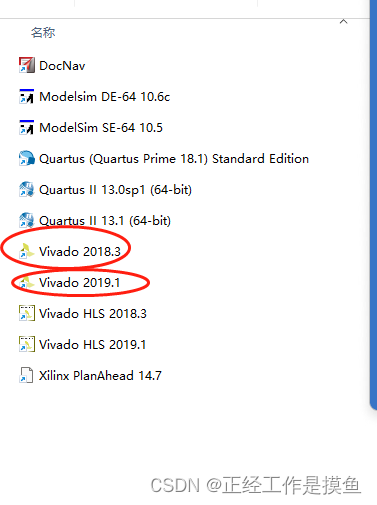

1.打开VIVADO

双击 Vivado图标即可启动 Vivado 软件。软件版本按自己习惯来

注意:低版本VIVADO建立的工程可以用相同版本或者更高版本的VIVADO打开(VIVADO高版本打开时有IP的需要),无法用低版本VIVADO打开

2.打开之后如下图所示

创建工程:创建一个全新工程

创建工程:创建一个全新工程

打开工程:打开之前创建的工程

打开例程:打开xilinx官方板卡例程

管理IP:创建和打开IP工程

打开硬件:打开硬件管理器,如果直接有bit流文件,则可以直接打开烧录

2.vivado建立工程流程

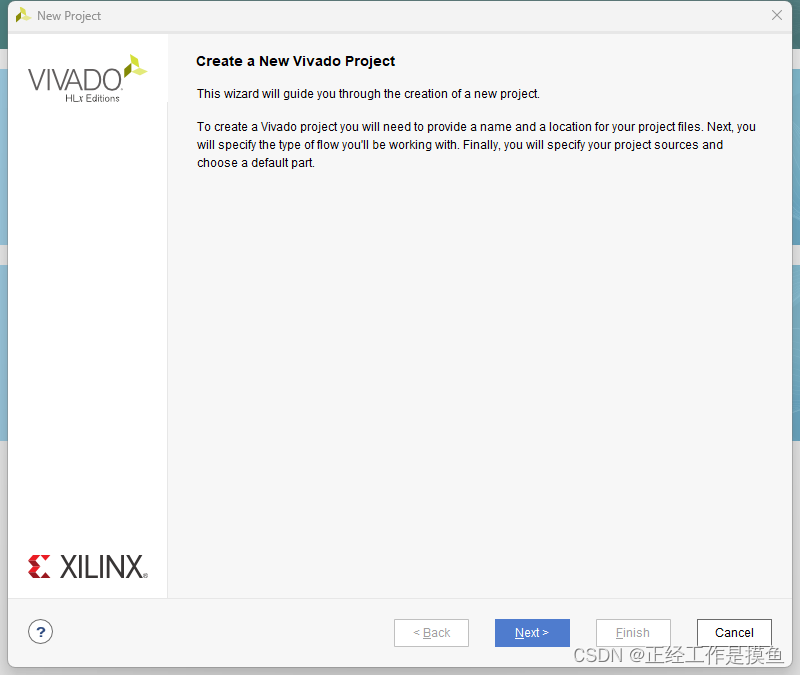

1.点击上面图片的创建工程,即可打开创建工程向导

下面只介绍vivado使用流程一些最常见的步骤,暂时不对细节做过多讲解

点击Next

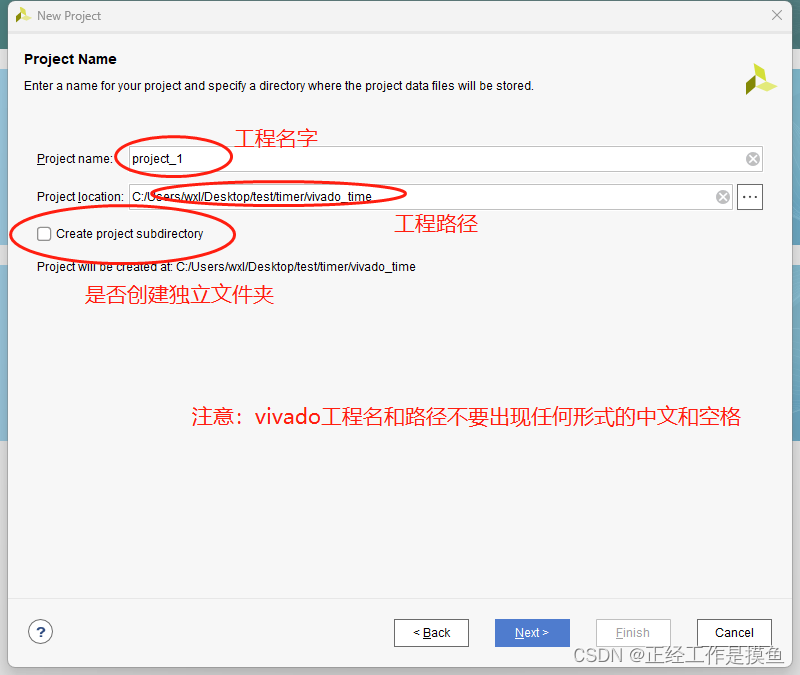

2.输入工程名和路径

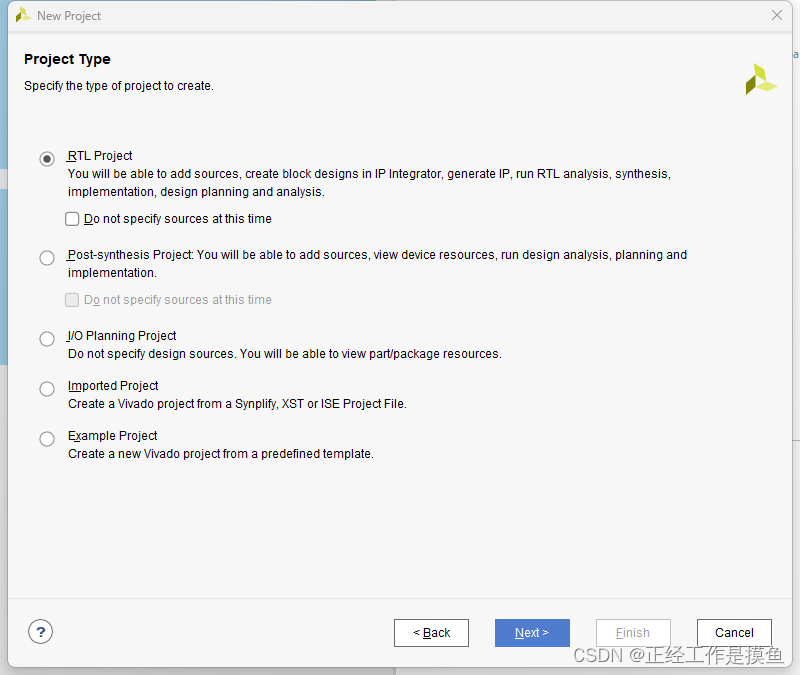

3.创建RTL工程,默认

4,添加源文件设计文件,可以在后面在添加

暂不添加,后面再加

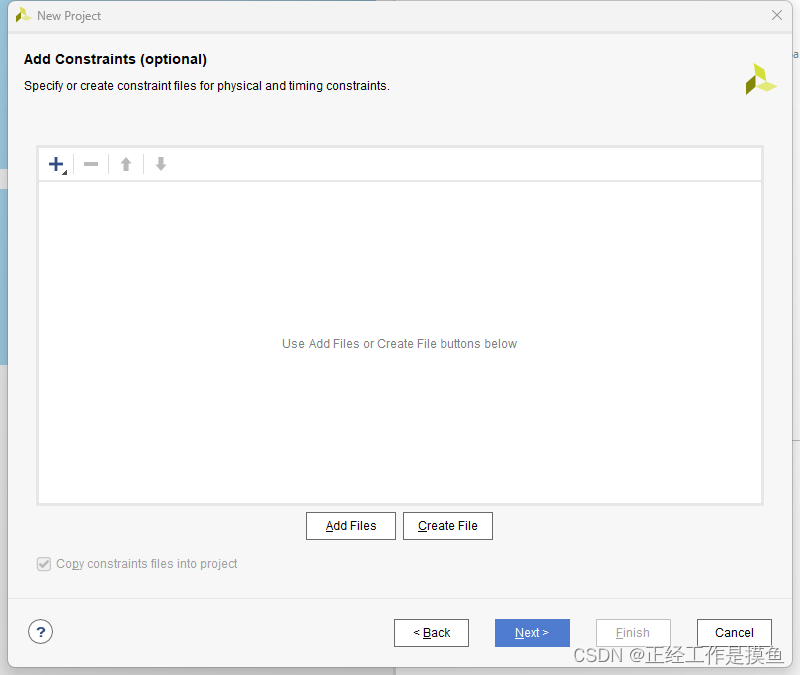

5,添加约束文件,也是暂不添加

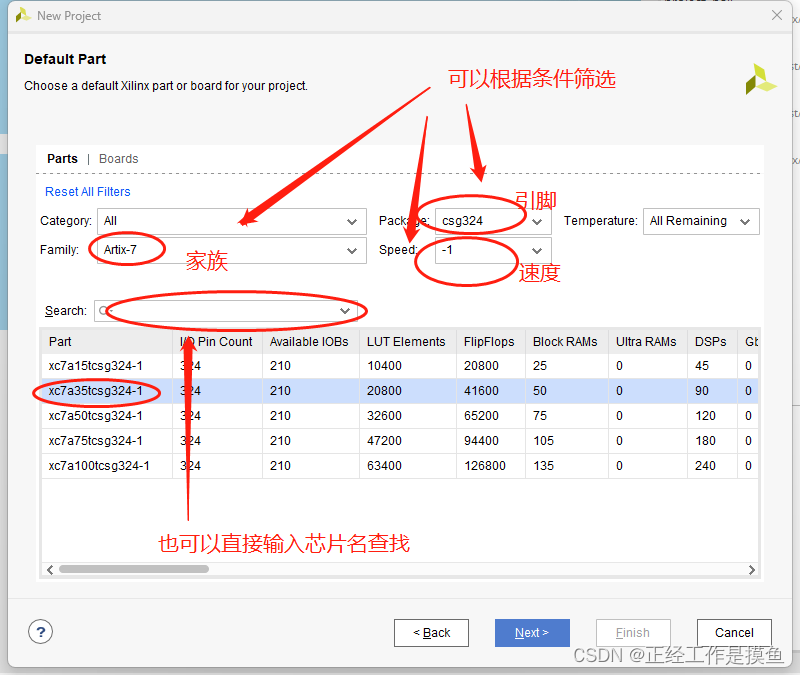

6.选择FPGA器件

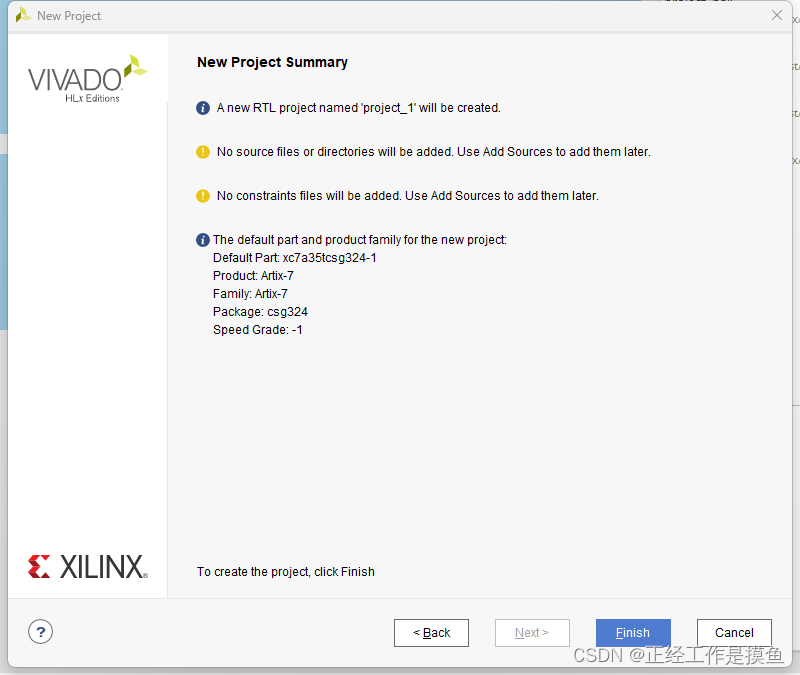

7.点击完成

VIVADO开发流程

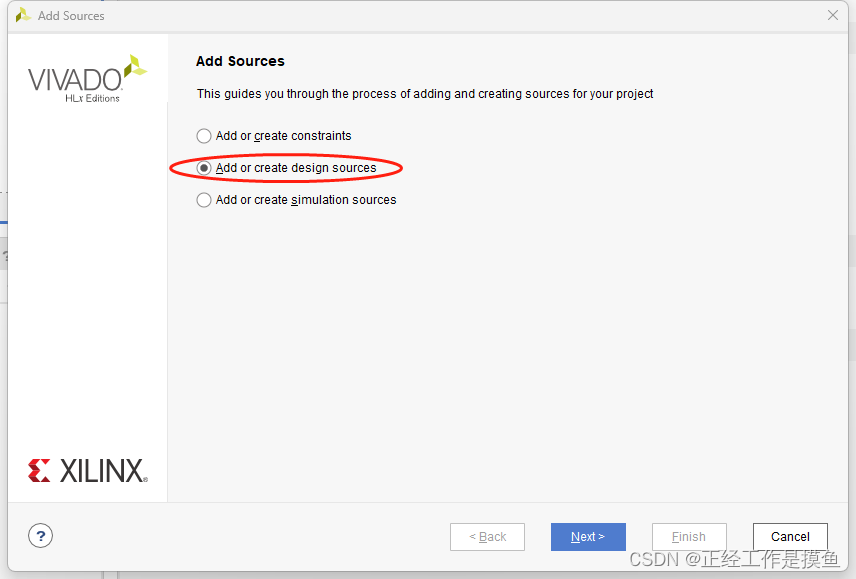

添加设计文件

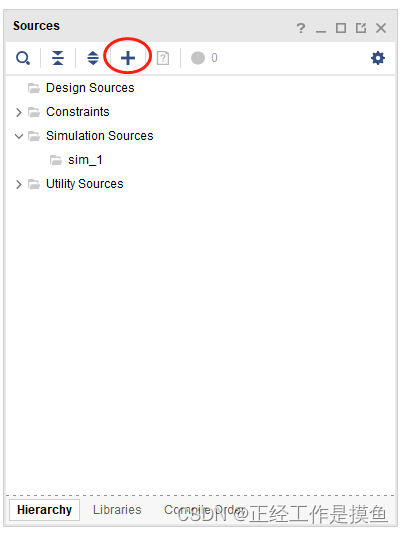

1.添加设计文件,点击source窗口的“+”号

2.选择设计文件

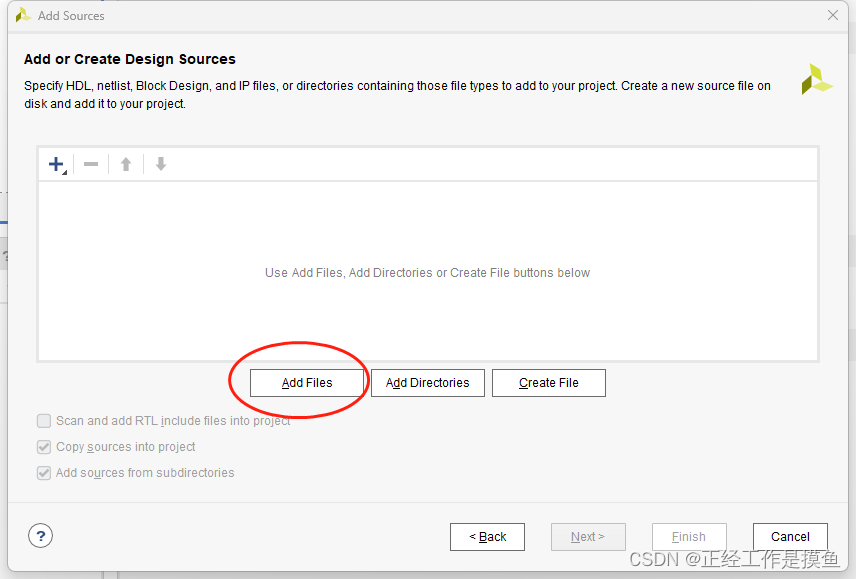

3.可以创建文件,也可以添加已有的文件,在这里直接添加

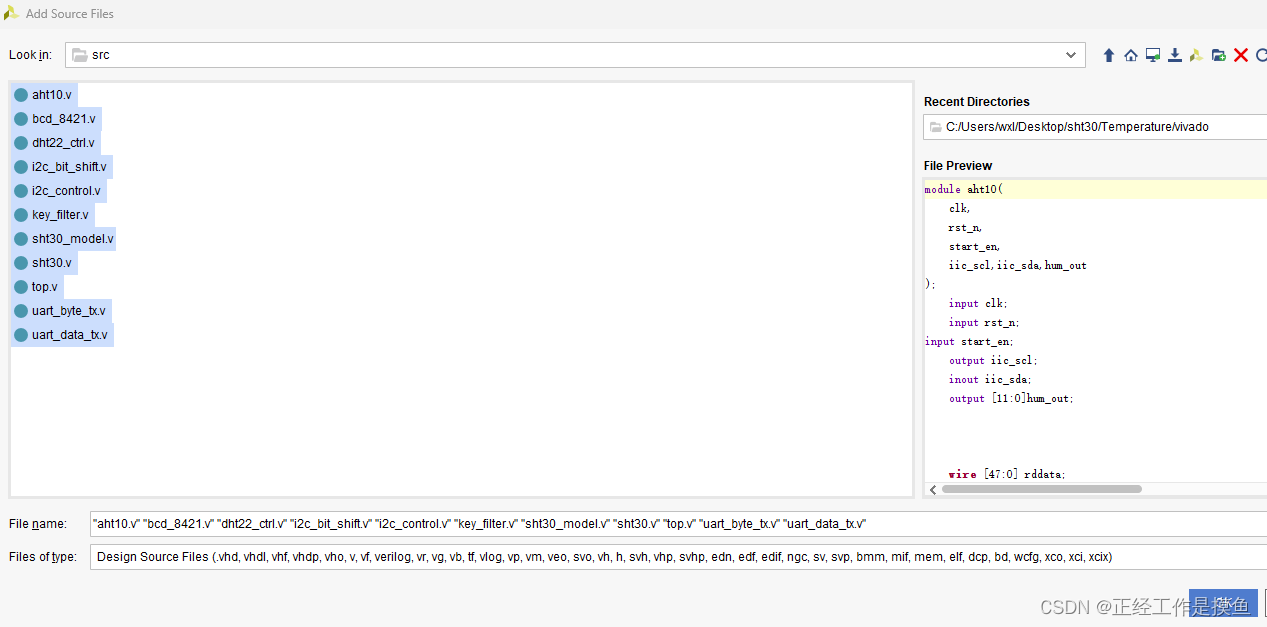

4.选择需要添加的文件,注意不要把测试文件加进去。点击完成

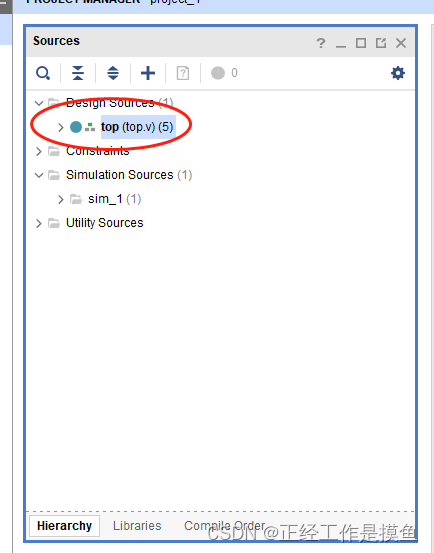

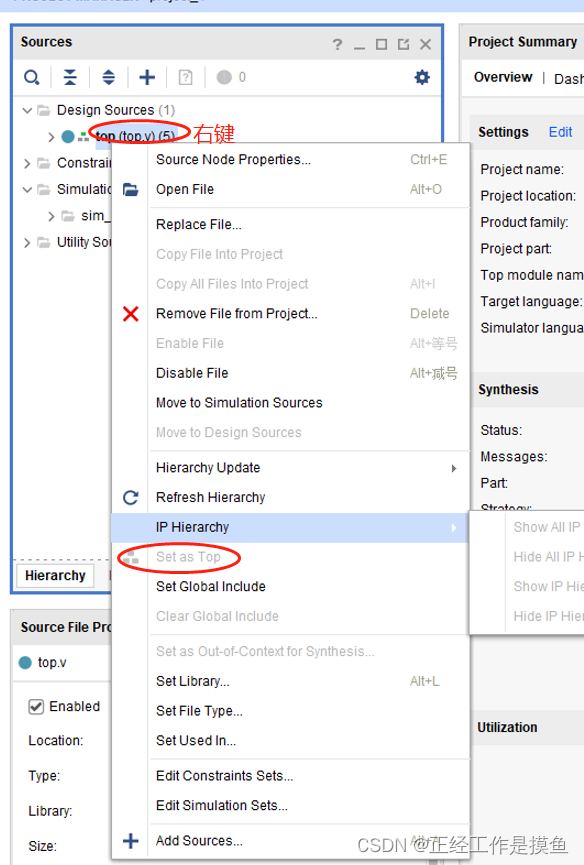

5.一般来说。vivado可以自动识别顶层文件,如果与设计不符,可以手动修改

添加IP核

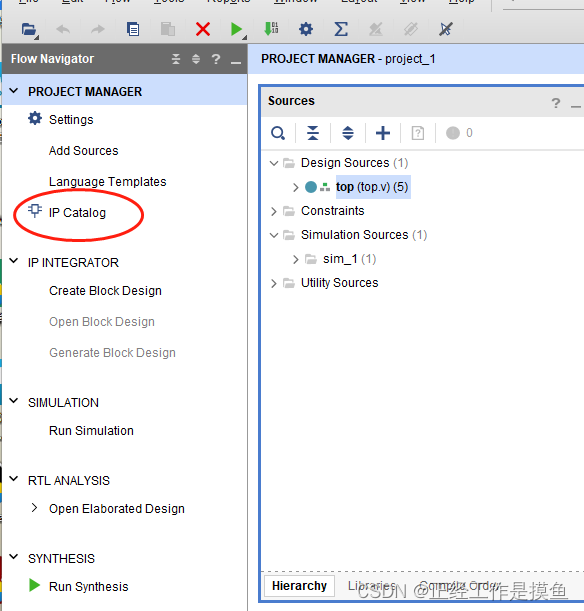

6.如果需要添加IP核,点击IP Catalog

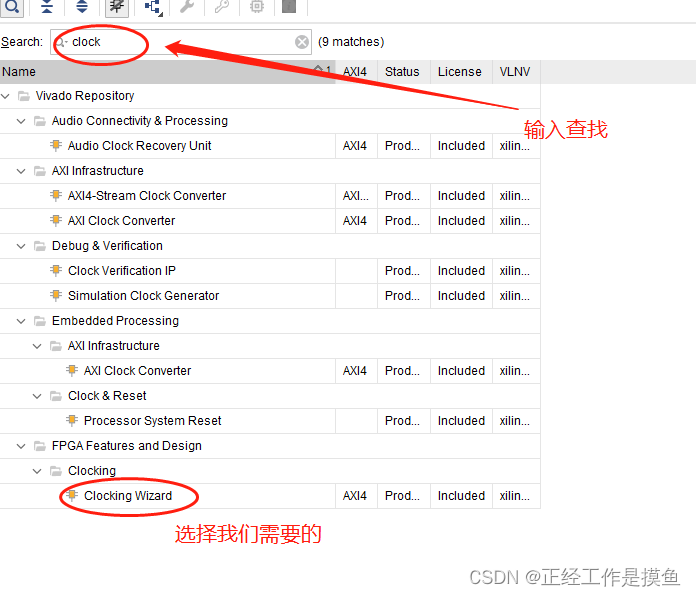

7.再弹出的窗口输入寻找的IP,选中

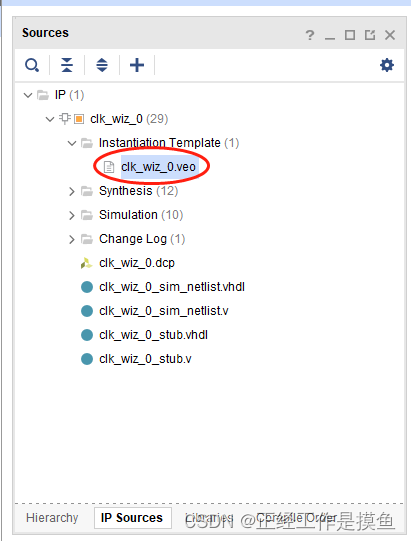

8.IP生成完后,点击,在需要的ip下打开.veo文件

9.复制例化模板

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

// Status and control signals

.resetn(resetn), // input resetn

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk_in1)); // input clk_in1

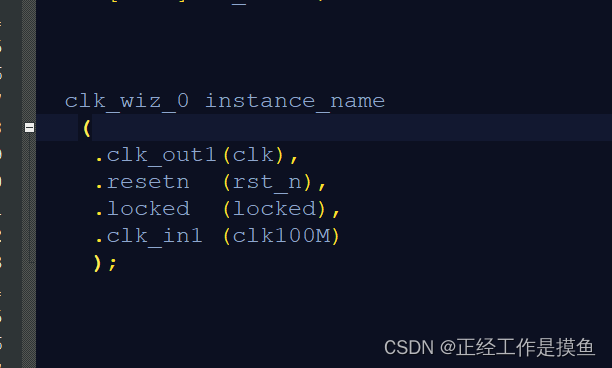

10.放到代码里使用

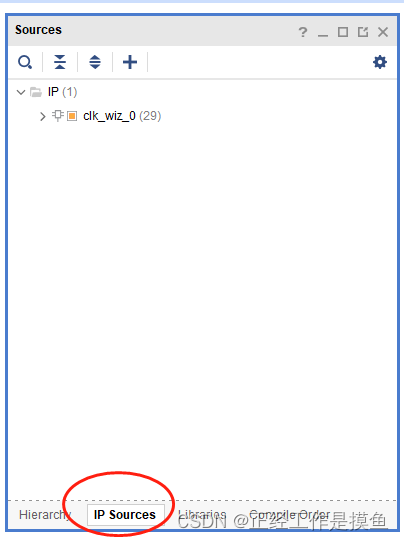

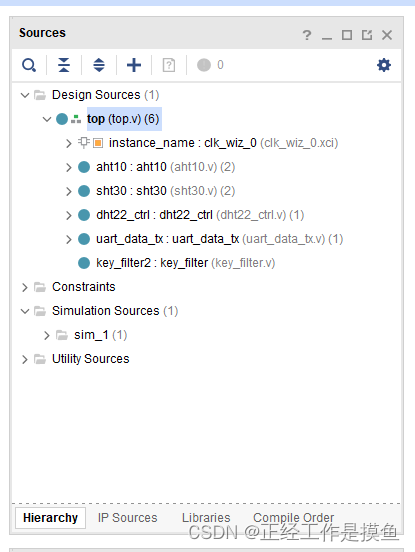

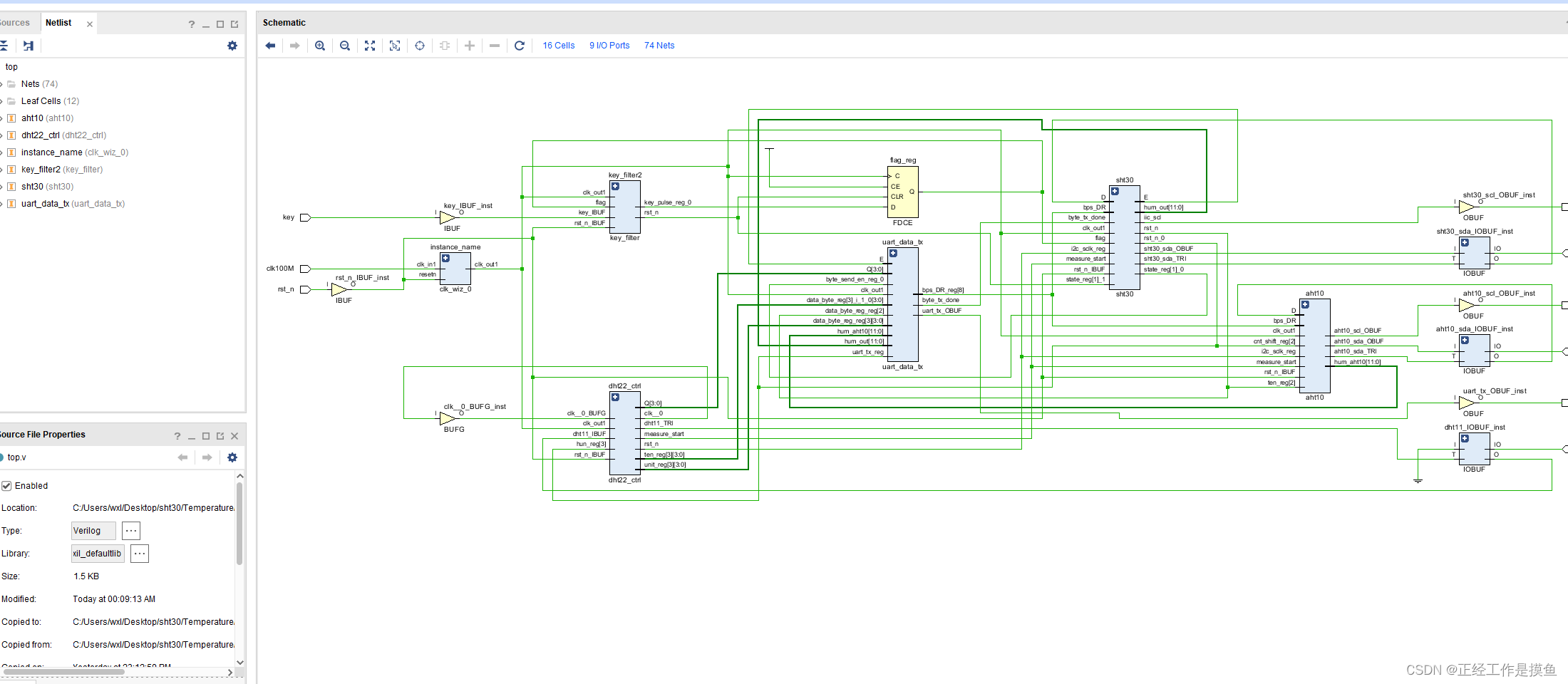

11.可以看到顶层文件包含了ip核

分析综合

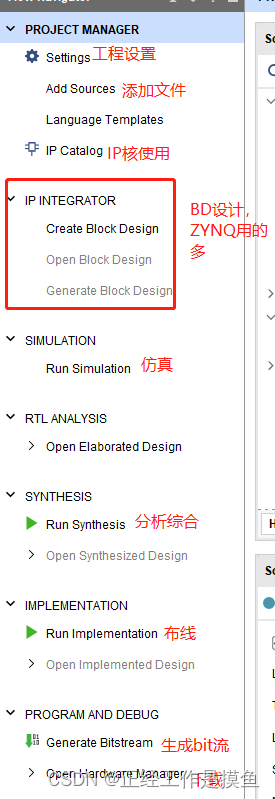

12.接下来分析综合,正好介绍下,左边按键作用

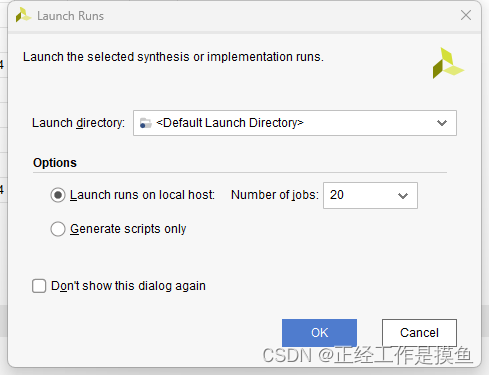

点击RUN Synthesis

点击OK,等待一会

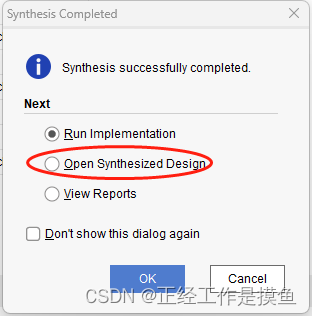

选择第二项,打开设计(不要默认,还要绑定引脚)

绑定引脚

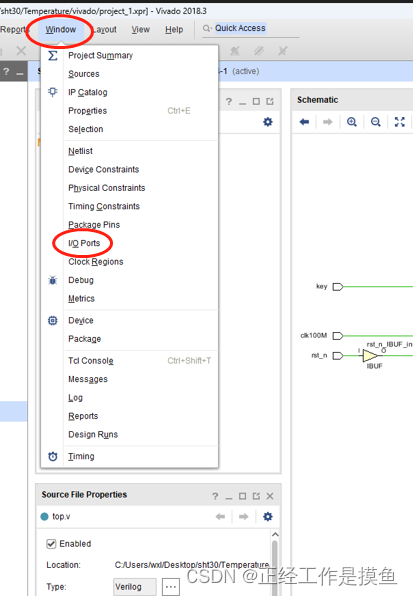

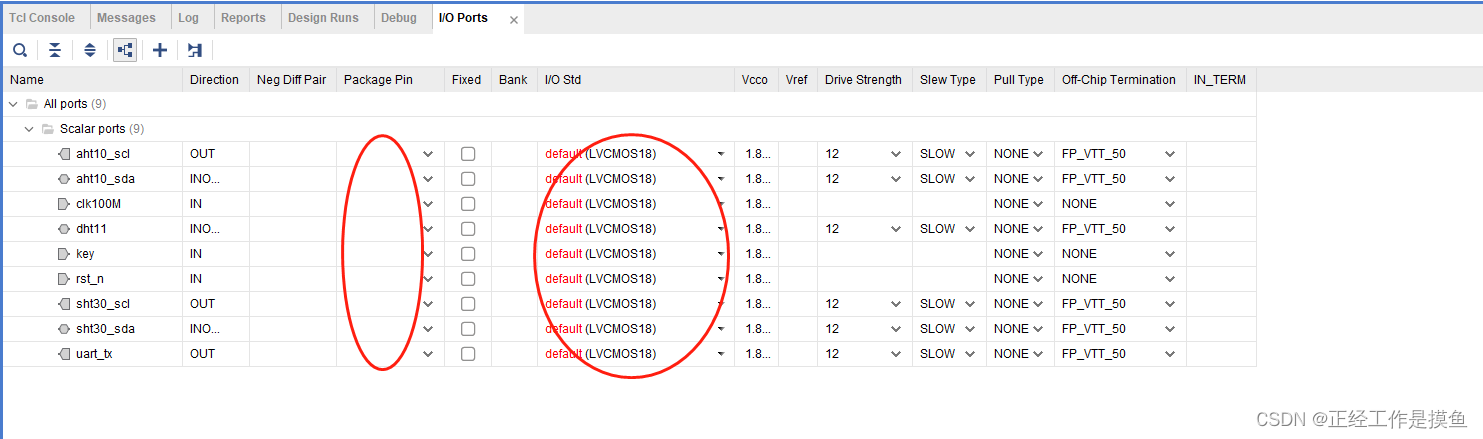

13.引脚绑定,选择Window-I/O ports

14,输入对应的引脚标号,电平标准,一般引脚约束只需要这两个

引脚标号,电平标准看原理图或者开发板用户手册

在一些需要片内上拉应用的地方,可以在Pull Type选择上拉类型

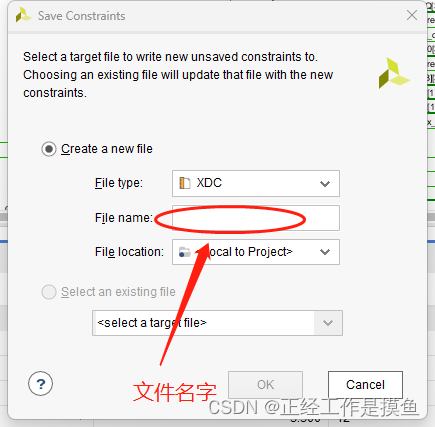

设置完记得保存,

注意:也可以直接添加引脚约束文件,方法是在添加设计文件的界面,选择约束文件,选好后可以直接添加

生成bit流

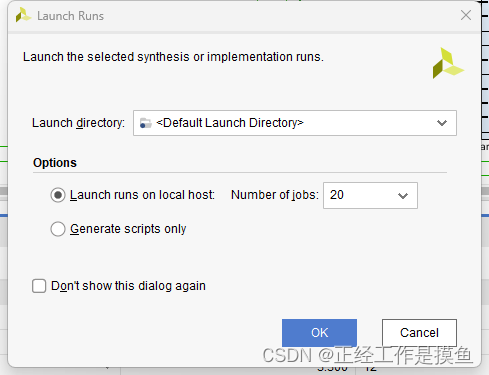

15.直接生成bit文件

上面的步骤他会自动跑

点击OK',

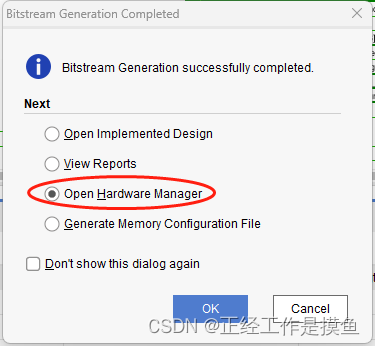

漫长等待,终于跑完,

生成 bit 流完成后弹出打开硬件管理器窗口

下载

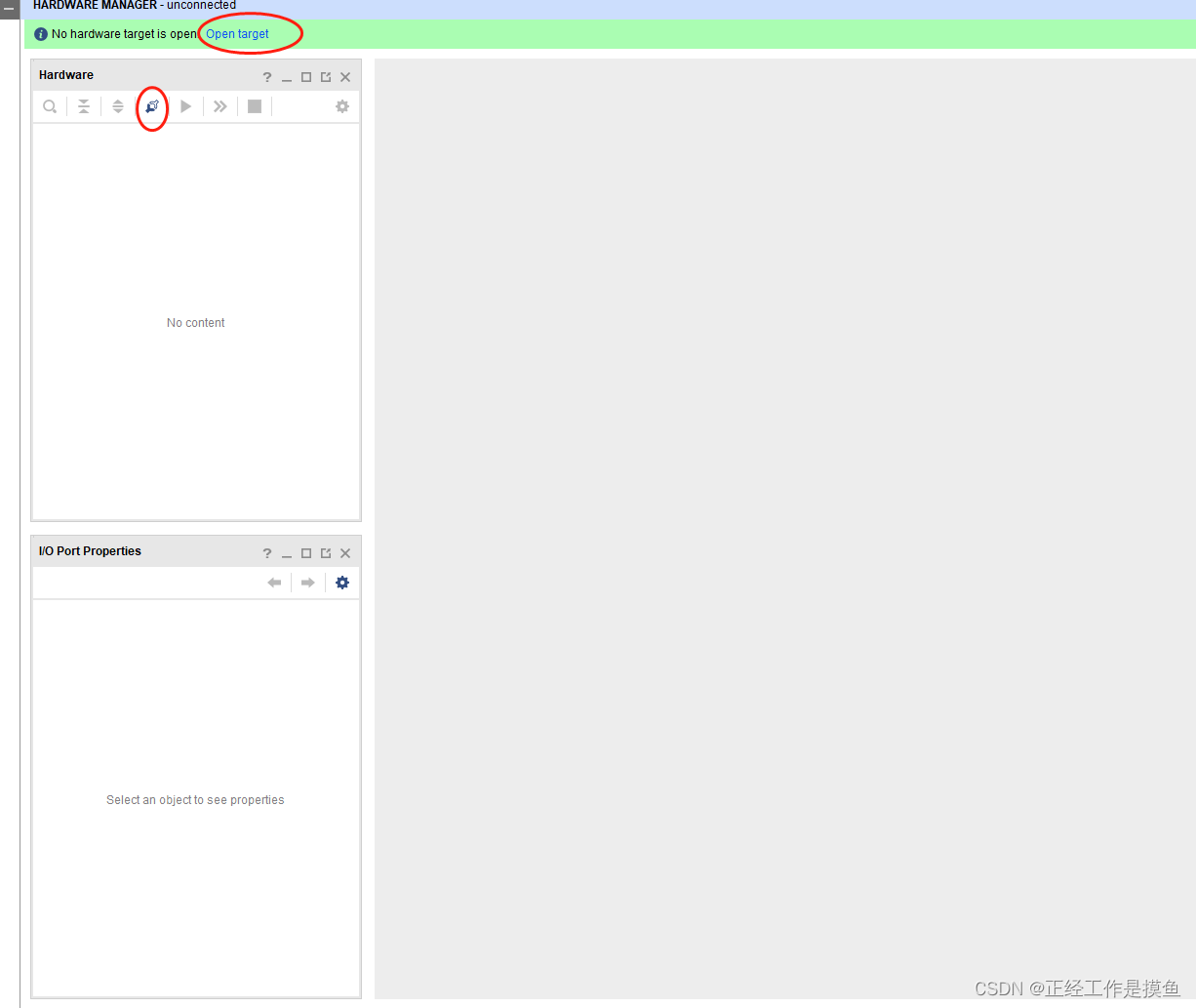

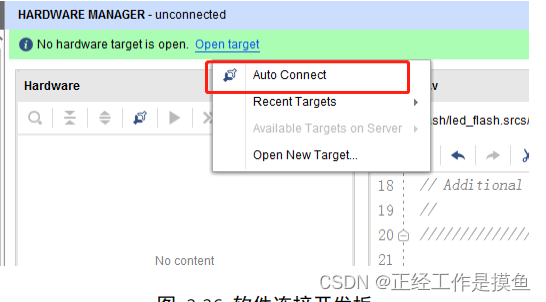

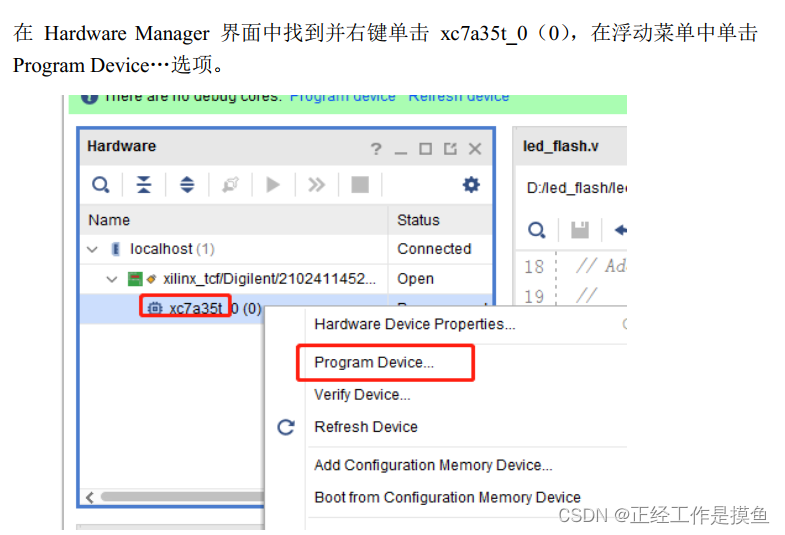

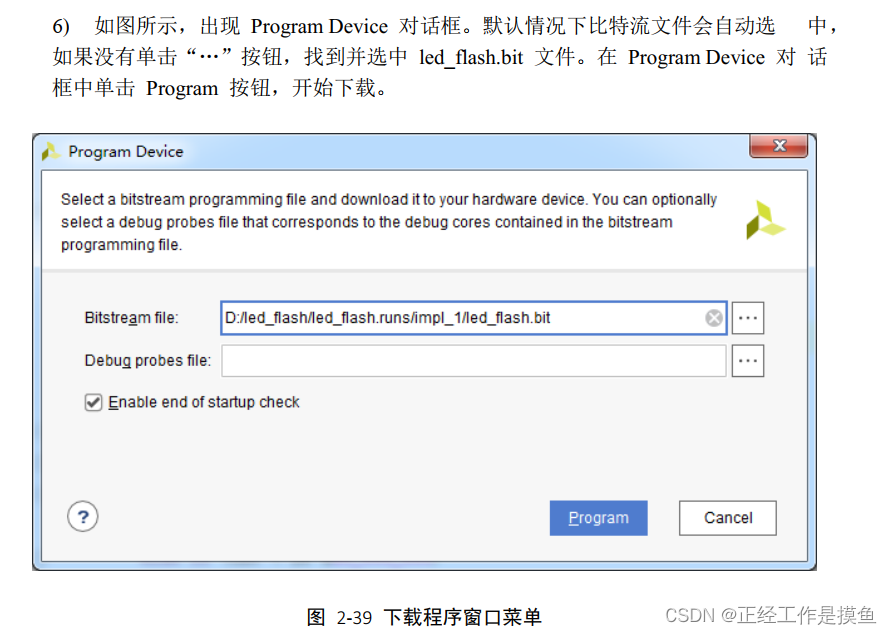

16.下载程序,上面正常会出来下面界面

Open Hardware Manager 变为 Hardware Manager;如果没有,则单

Open Hardware Manager 打开 Hardware Manager。 Vivado 右上侧出现 Hardware

Manager 界面,

点击圈中的地方查找硬件

17.最后一步,观察现象

6498

6498

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?