未经本人允许,禁止任何形式转载!!!!

“条条大路通罗马”,FPGA也一样,实现同一功能的逻辑代码也可以不同的,当然消耗的FPGA芯片逻辑资源也是不同的。话不多上,上干货!

举一个简单的例子,现在我们要用FPGA实现一个“四输入中,同一时刻只有一个高电平,且当某个高电平会点亮对应一颗LED灯”功能,我们现在用两种方法实现。

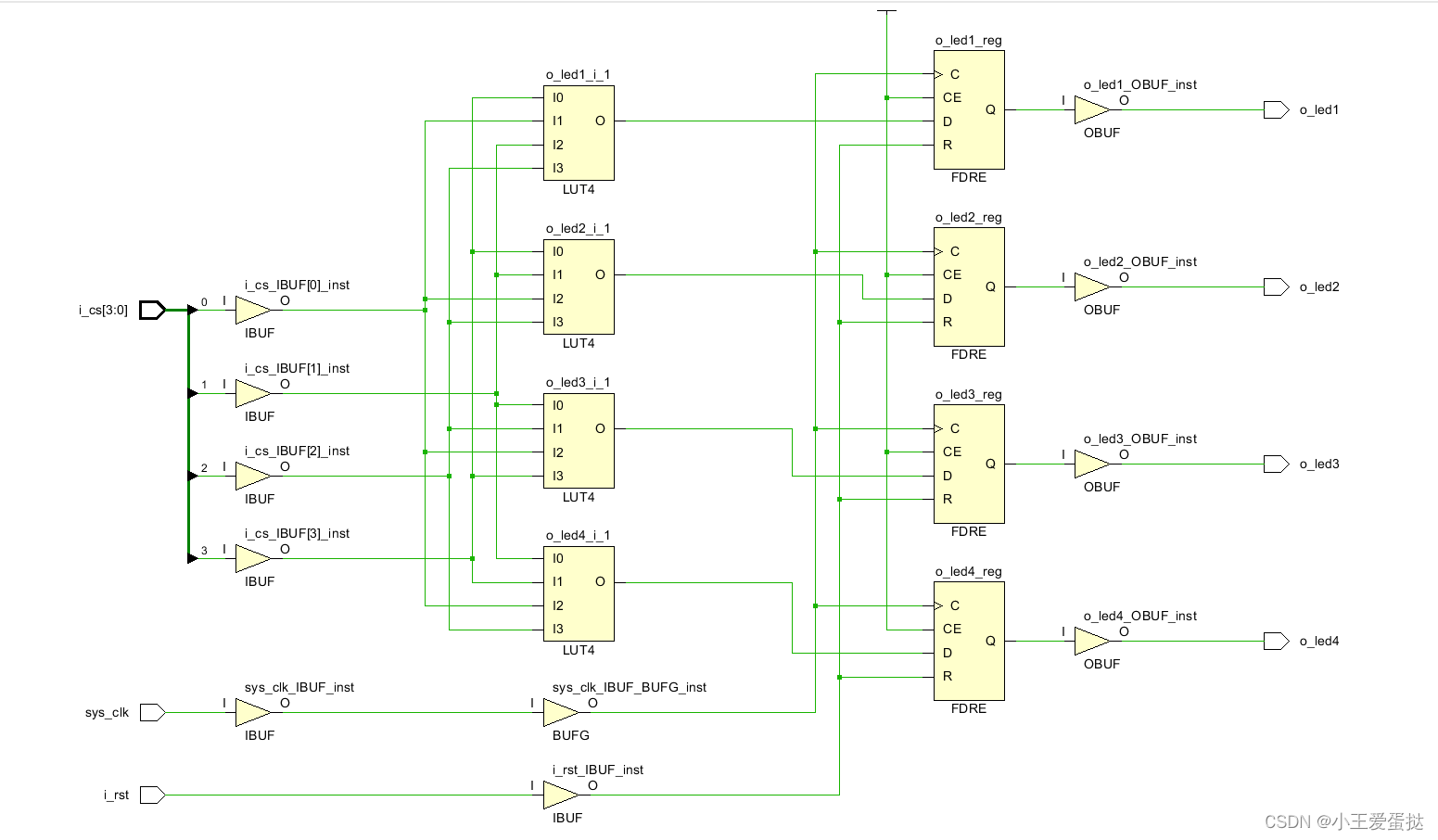

方法一:用case语句实现,FPGA源码见附件一,逻辑综合后,电路如图1-1所示,由图可看出,该逻辑电路是一个多路选择器,即后级电路的输出只依赖于输入信号(o_led1,o_led2,0_led3,o_led4的优先级是一致的),逻辑电路简单明了,对电路时序也比较友好!!!

图1-1

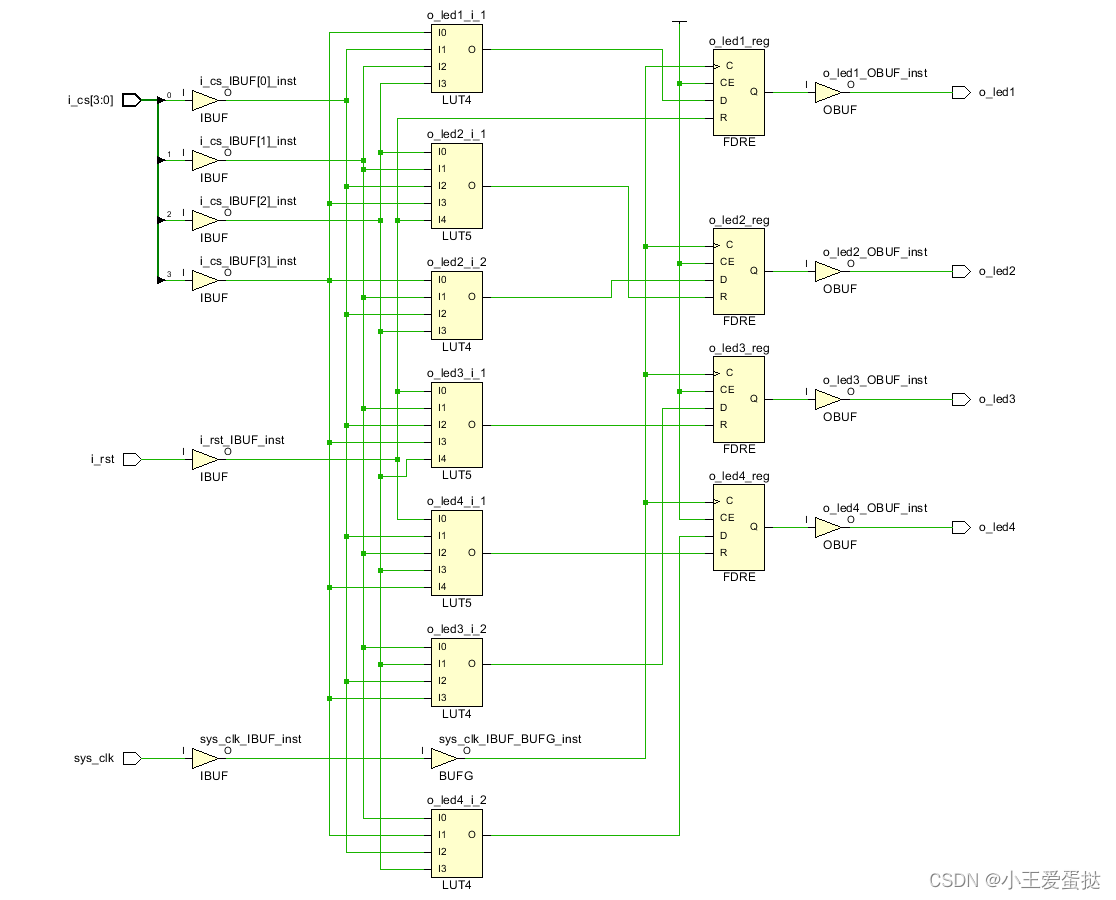

方法二:用if...else语句实现,FPGA源码见附件二,逻辑综合后,电路如图1-2所示,由图可看出,该逻辑电路是一个优先选择器电路,即后级电路的输出不仅依赖于输入信号,也依赖于前级电路(o_led1的优先级最高,以此类推,o_led4的优先级最低),消耗的逻辑资源相对于case语句多消耗了3个LUT资源(其中还有2个5输入的LUT资源),逻辑电路也相对复杂,对电路时序也不太友好!!!

图1-2

因此,FPGA的逻辑代码的编写在保证功能正确的前提下,也应多从电路的角度来考虑逻辑代码如何编写可以更少的消耗FPGA逻辑资源,尤其是在做大型FPGA项目时(FPGA芯片资源往往很紧张,电路时序要求也比较严格),这点至关重要!!!

未经本人允许,禁止任何形式转载!!!!

附件一

module fpga_case(

input sys_clk,

input [3:0] i_cs,

input i_rst,

output reg o_led1,

output reg o_led2,

output reg o_led3,

output reg o_led4

);

always @(posedge sys_clk)begin

if(i_rst)begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

else begin

case(i_cs)

4'b0001:begin

o_led1 <= 'd1;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

4'b0010:begin

o_led1 <= 'd0;

o_led2 <= 'd1;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

4'b0100:begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd1;

o_led4 <= 'd0;

end

4'b1000:begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd1;

end

default:begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

endcase

end

end

endmodule附件二

module fpga_if_else(

input sys_clk,

input [3:0] i_cs,

input i_rst,

output reg o_led1,

output reg o_led2,

output reg o_led3,

output reg o_led4

);

always @(posedge sys_clk)begin

if(i_rst)begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

else if(i_cs == 4'b0001)begin

o_led1 <= 'd1;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

else if(i_cs == 4'b0010)begin

o_led1 <= 'd0;

o_led2 <= 'd1;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

else if(i_cs == 4'b0100)begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd1;

o_led4 <= 'd0;

end

else if(i_cs == 4'b1000)begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd1;

end

else begin

o_led1 <= 'd0;

o_led2 <= 'd0;

o_led3 <= 'd0;

o_led4 <= 'd0;

end

end

endmodule

6819

6819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?