目录

一、HLS是什么?与VHDL/Verilog编程技术有什么关系?

1.HLS简介

HLS(High-Level Synthesis),HLS是高层次综合的简称,至于层次的理解。一般分为系统级、算法级、RTL级、门级,开关级。

一般认为RTL级及以下设计是可用的,“层次”即从什么角度去描述想要实现的功能。譬如,a xor b采用门级描述就是a,b是一个异或门的输入;而采用高一点层次描述就是a+b。显然,越低层次的描述越困难

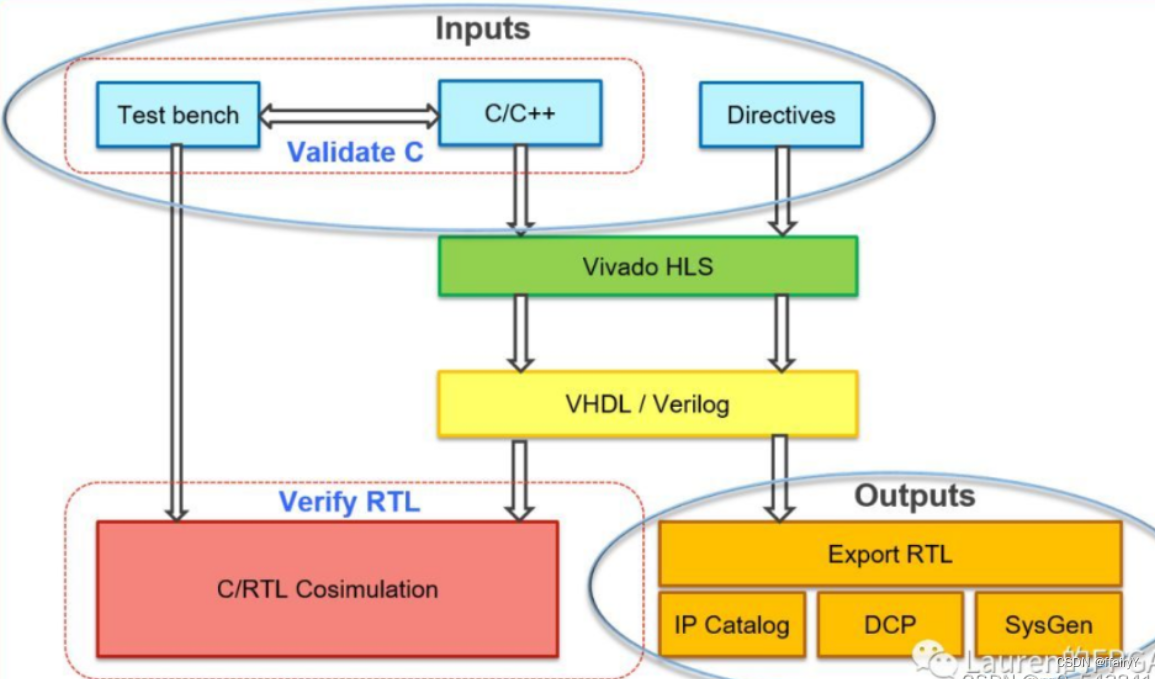

HLS就是从高层次描述,之后综合成可用的网表文件的技术。这里的“高”指采用C、C++等编写程序,而不是传统的HDL语言。然而,实际上Vivado套件中是预先采用Vivado HLS这个软件将C程序转换成为Verilog HDL或者VHDL代码,之后进行下一步操作的,并不是直接综合C代码。

对比:传统的 FPGA 开发,首先写 HDL 代码,然后做行为仿真,最后做综合、时序分析等,最后生成可执行文件下载到 FPGA 使用,开发周期比较漫长。使用 HLS,用高级语言开发可以提高效率。因为在软件中调试比硬件快很多,在软件中可以很容易的实现指定的功能,而且做 RTL仿真比软件需要的时间多上千倍。

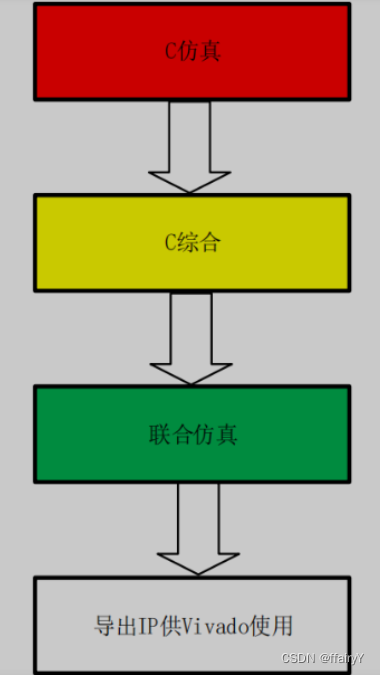

2.开发流程

可以看到Vivado HLS设计输入包括三部分:C算法描述文件、C算法仿真文件和Directives文件。最终输出结果以IP、DCP或SysGen模型的形式存在。

3.HLS与VHDL/Verilog编程技术有什么关系?

RTL(寄存器传输级别,基于 VHDL/Verilog 语言)逐步发展,但 VLSI 系统的复杂性呈指数级增长,使 RTL 设计和验证过程成为生产力的瓶颈。HLS(高级综合)通过提高抽象级别, 可以减少最初的设计工作量,设计人员可以集中精力描述系统的行为,而不必花费时间来实现微体系结构的细节,且验证被加速、设计空间探索(DSE)更快、定位新平台非常简单、软件工程师可以访问 HLS 等这些好处加在一起,减少了设计和验证时间,降低了开发成本,并降低了进行硬件项目的门槛,因此缩短了产品上市时间,并且在异构系统上使用硬件加速已成为更具吸引力的选择。但是在结果质量(QoR)上,HLS 工具还落后于 RTL。

二、HLS有哪些关键技术问题?目前存在什么技术局限性?

1.技术问题

1.与Verilog相比,能做到的优化十分有限

2.技术局限性

1.HLS实现简单逻辑较为臃肿:

对于一些简单的逻辑,HLS实现结果较为臃肿。一些简单的逻辑,用HDL实现只需要数十行代码,而HLS的实现结果却相当复杂。

2.HLS对开发人员要求较高:

HLS对开发人员的要求比较高。HLS使用的语言显然不是标准C/C++语言,是扩展类C/C++语言。

HLS更适合于已经有现成的、高质量的C算法代码,这时候急需在FPGA上去映射成硬件,非常高效,但是对于有经验的verilog手写设计者,HLS综合工具有时候用得非常麻烦。设计者明知道一个方案是可行的,但是就想不到如何让HLS把C代码变成自己设想的电路。

三、使用 HLS 完成 led 灯闪烁

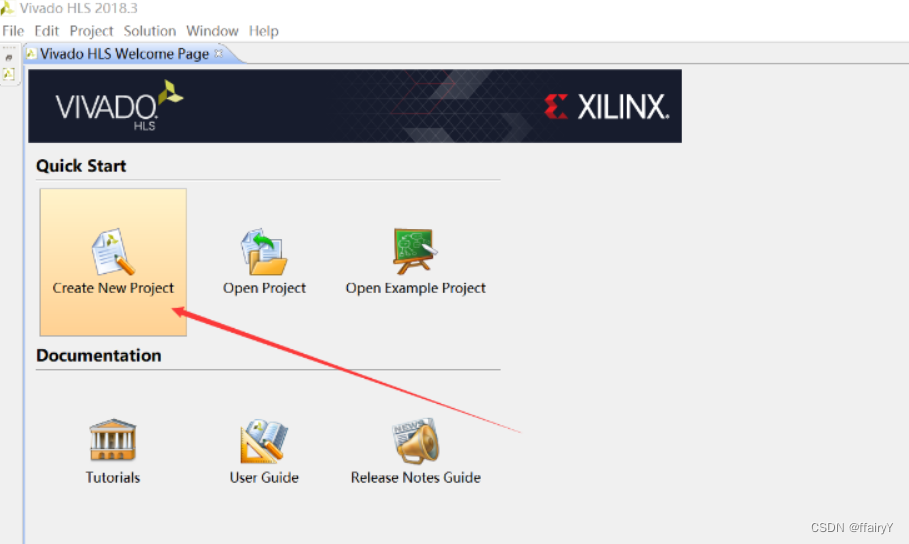

1、新建工程

打开Vivado HLS并新建一个工程:

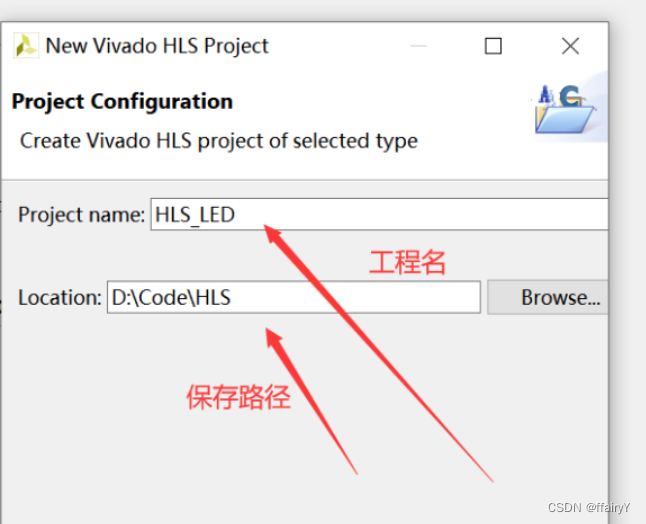

设置工程名及路径:

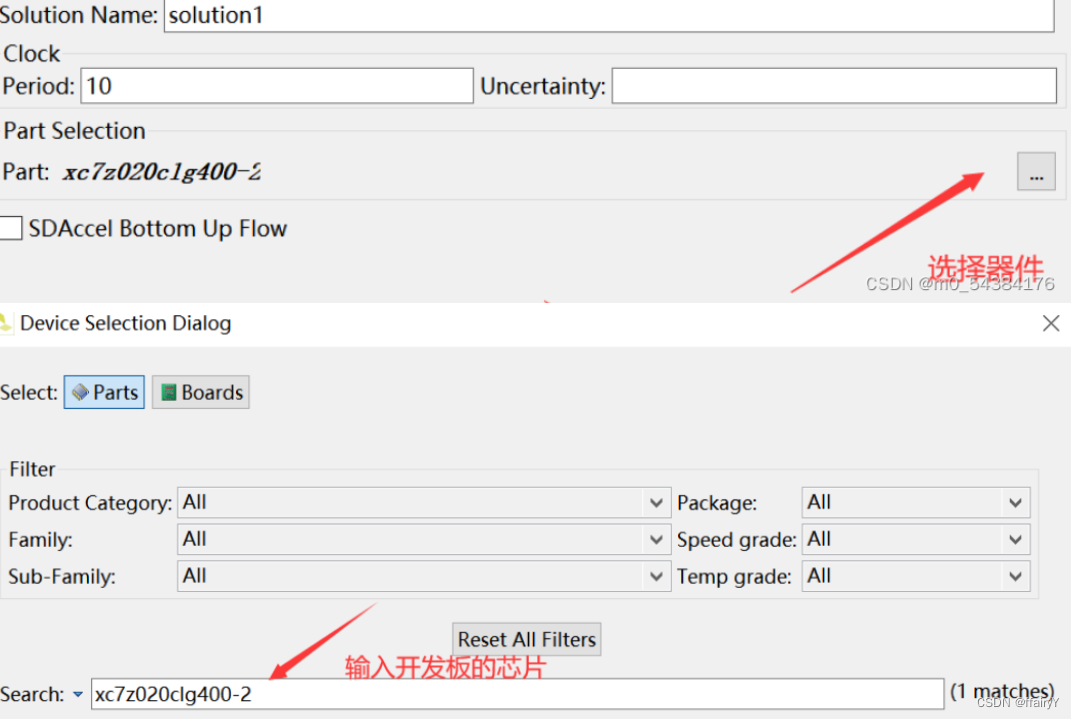

选择器件:

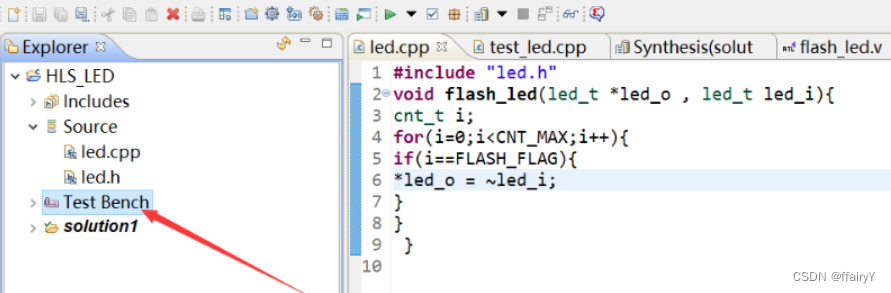

2、添加C文件

添加源文件:

右键 Source,点击 New file,在弹出的窗口中,选中我们存放源码的目录后。新建一个 led.cpp 文件和led.h头文件。

头文件代码:

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#define CNT_MAX 100000000

//#define CNT_MAX 100

#define FLASH_FLAG CNT_MAX-2

typedef int led_t;

typedef int cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

源文件代码:

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

添加C仿真文件:

右键 Test Bench,选择添加新建文件,在弹出窗口新建一个 test_led.cpp。

C仿真代码:

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

3、进行C仿真与综合

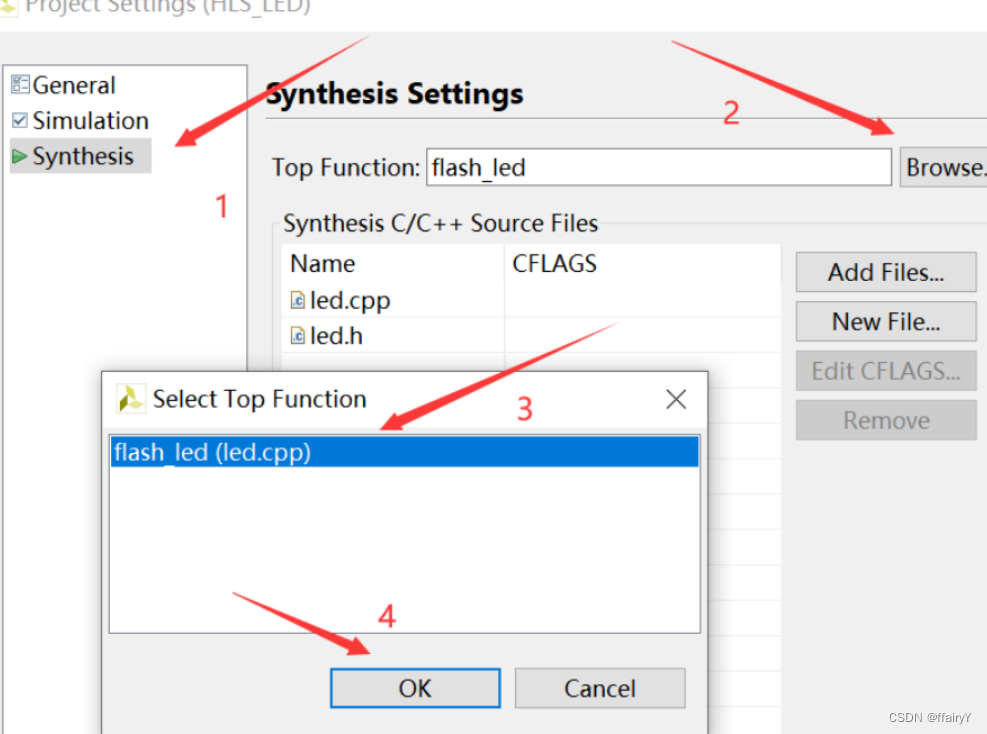

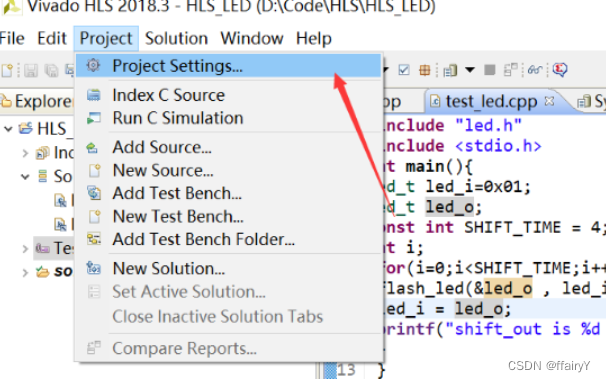

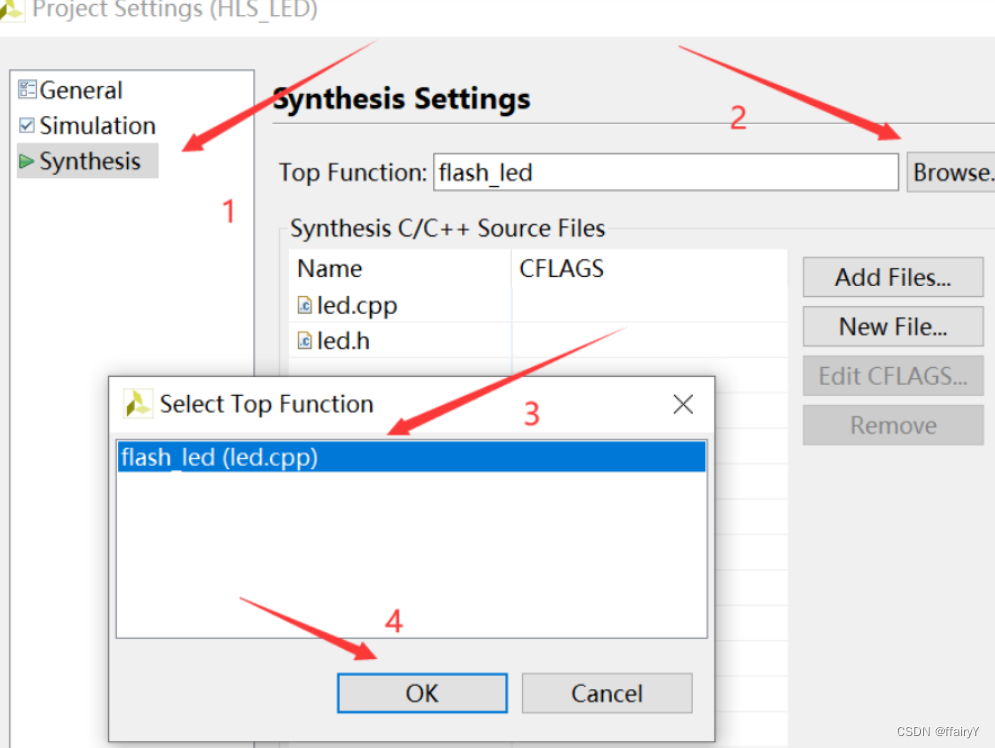

设置顶层文件:

点击 project >选择project seethings>选择 synthesis>browser>选择 flash_led 作为顶层函数

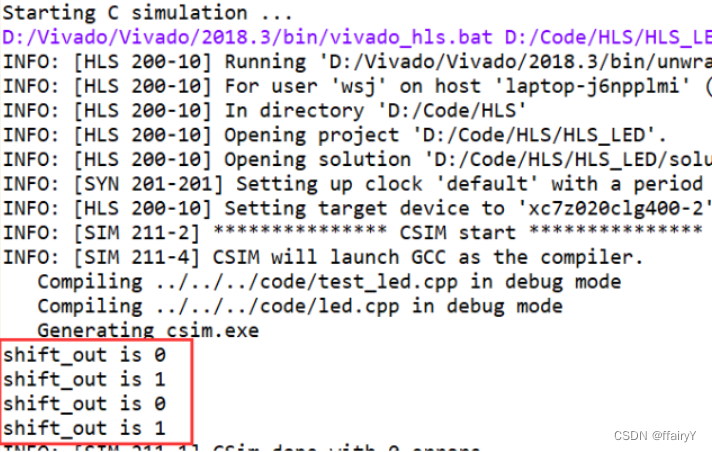

然后点击 project >Run C simulation进行仿真,仿真结果:

我们可以看到输出的结果时 01 交替变化,证明 C 仿真的结果正确。

点击 Solution>Run C Synthesis >Active Solution进行C综合:

4、联合仿真

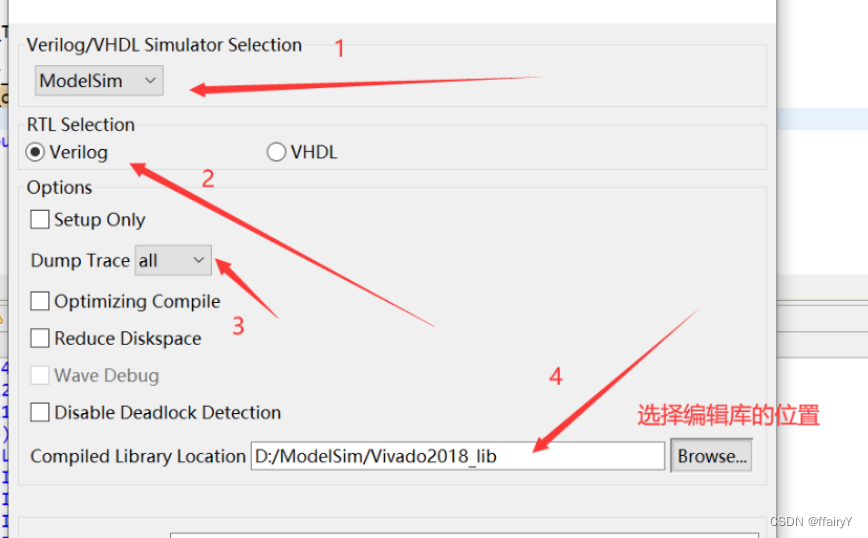

我们可以通过C/RTL联合仿真来验证映射出来的RTL电路是否正确。需要注意的是Vivado HLS会利用我们的C Testbench 自动生成Verilog Testbench,同时,联合仿真结束过后,我们可以通过使用 Vivado 或者 Modelsim 来查看仿真波形。

点击 Solution > Run C/RTL Cosimulation进行联合仿真:

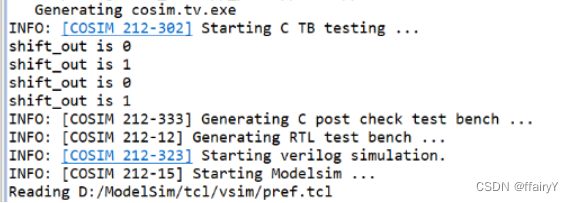

仿真结果:

仿真得到的结果与在 C 仿真时得到的结果一致。

5.Modelsim查看信号

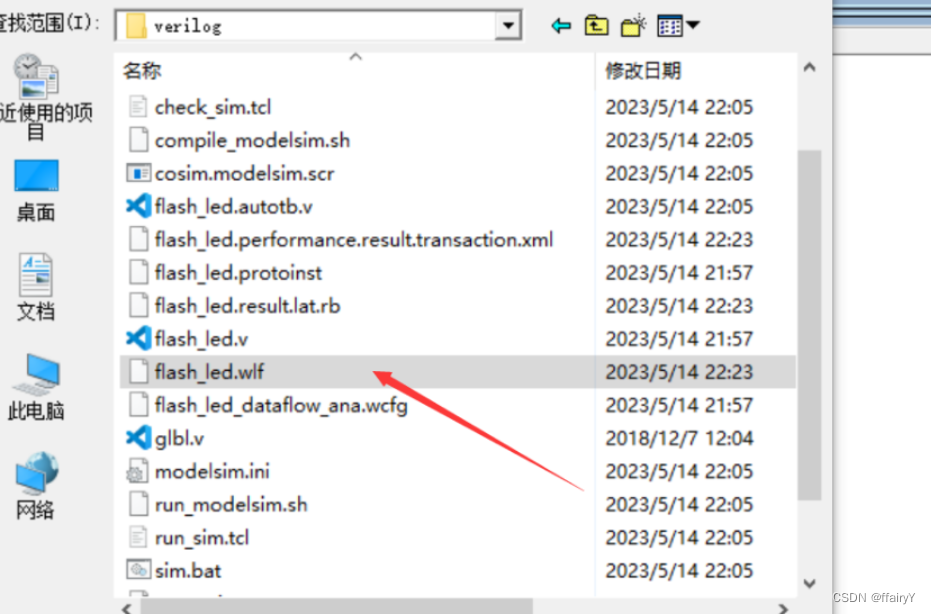

Modelsim打开wlf文件观察波形:

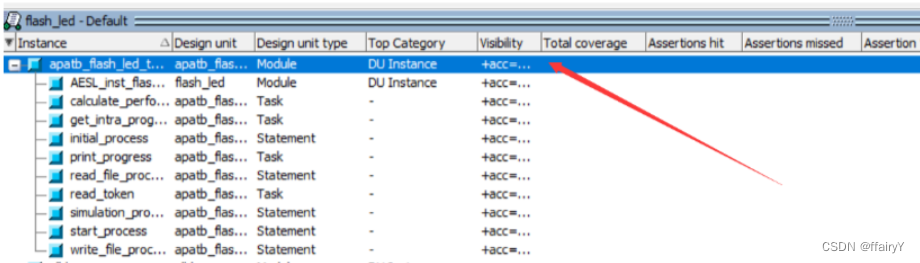

右击选择add wave将定成模块的信号添加到波形窗口:

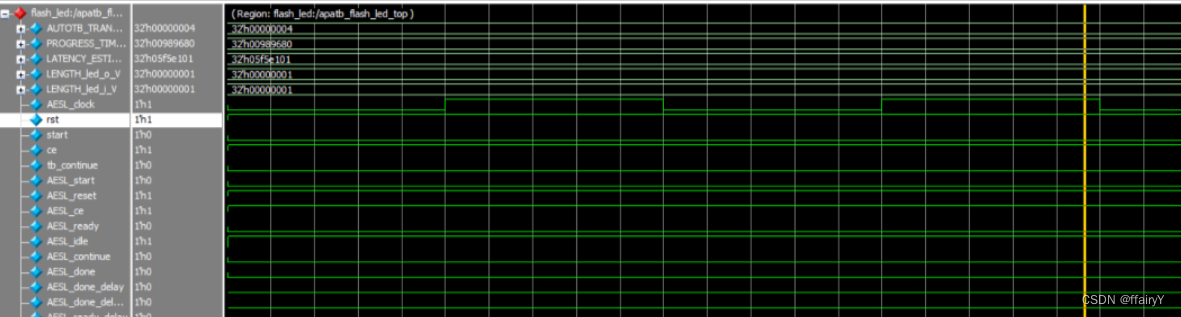

波形图:

总结

此次实验使用了不同于Verilog的语言来实现LED的仿真测试,但是并没有进行上板测试,不过已经大致了解了HLS的基本使用方法,拓展了我对于这方面的理论知识。

7387

7387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?