前言

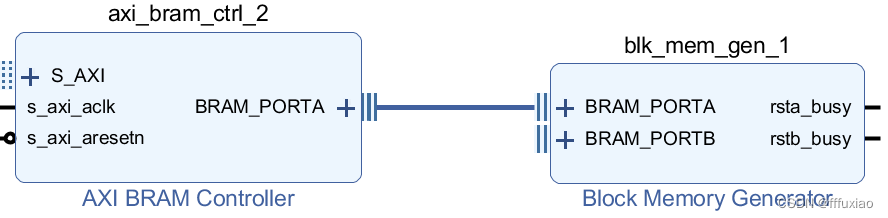

当我们的项目想实现microblaze和rtl进行数据交互时,可以使用双口ram。portB连接我们的RTL逻辑部分,portA可以在block design中使用axi_bram_ctrl ip核进行连接。

一、基础配置(Basic Setting)

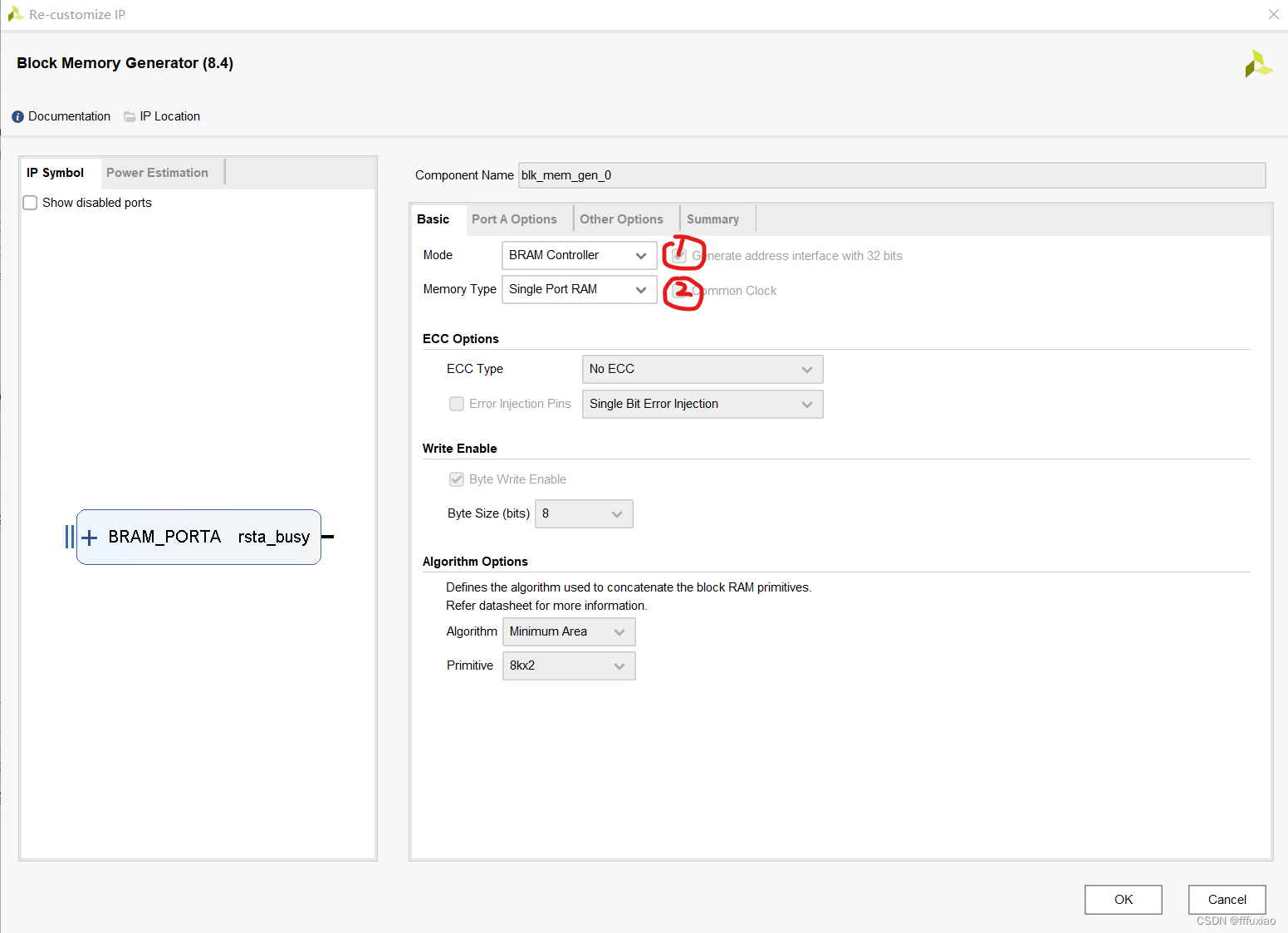

主要的设置选项包括两个:模式(Mode)和存储器类型(Memory Type)。

①Mode:用来设置IP模式,默认为BRAM Controller,当你打算使用axi_bram_ctrl或者lmb_bram_if_ctrl两个官方的ip核来对BRAM进行控制时,Mode设置为BRAM Controller。但需要注意,该模式下,除了配置BRAM的类型外,所有的参数不可自行设置。

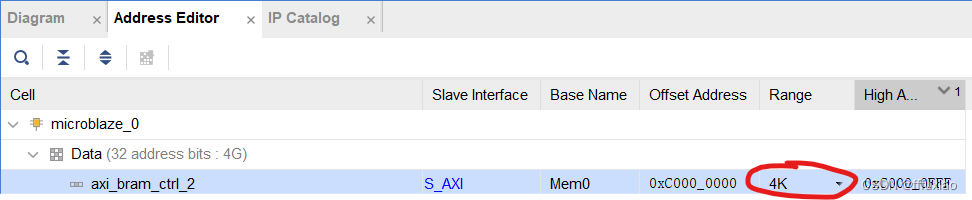

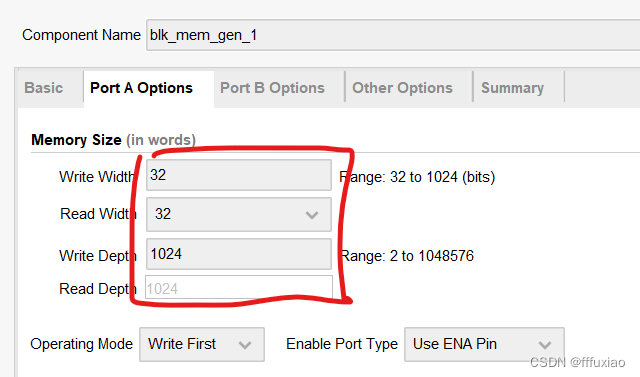

当你选用BRAM Controller模式后,用户在该IP配置页面仅仅可以配置BRAM为单端口RAM、真双端口RAM、单端口ROM等。我们常规的参数如:端口数据位宽(write/read width),以及存储深度(write/read depth),均无法自己配置。这是用户在block design->address editor中对ip核进行地址大小分配时就自动生成了。

例如:我在这里给一个bram分配了4K的地址空间,则其容量可以视为:4*1024*8bit,那么与该axi_bram_ctrl相连接的bram(blk_mem_gen1)的数据宽度(width)和深度(depth)被自动分配成了1024*32bit,总容量与用户分配的地址空间一致。

②Meomory type:配置BRAM为单端口RAM、真双端口RAM、单端口ROM及真双端口ROM。

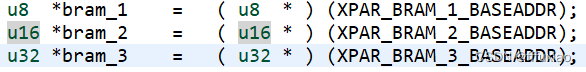

二、实际使用

RTL对bram的访问和常规使用一致,在sdk中对bram进行读写需注意一个指针长度问题。sdk访问bram时,最小的读写数据为8bit(每个地址存储一个字节的数据)。当你指针定义为u8时,则可以一个地址进行读写,定义为u16时,则两个地址进行读写,u32则四个地址进行读写。

当我们将指针定义为u16时:*(bram_0+1)= 0xFFFF。实际访问的地址是2=1*2。

当我们将指针定义为u32时:*(bram_0+1)= 0xFFFF。实际访问的地址是4=1*4。

三、官方文档

想详细研究的可查看官方文档,附上链接。https://docs.amd.com/v/u/en-US/pg058-blk-mem-gen

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?