文章目录

1、前言

2、相关参考链接

3、

前言

由于本人的水平有限,写的博文中难免有些疏漏,欢迎大家批评指正。

相关参考链接

最开始开始学习VIVADO的这个IP核参考了下面的这些链接。这个博客写的挺详细的,大家可以看看。

ZYNQ—BRAM全双工PS_PL数据交互(开源)_zynq ps pl 数据传输-CSDN博客

问题描述

0、下面这个问题是我在参考上面的链接进行实验的时候,遇到的问题,然后在我买的一个开发板问答群里文档问题,我就直接复制过来了。

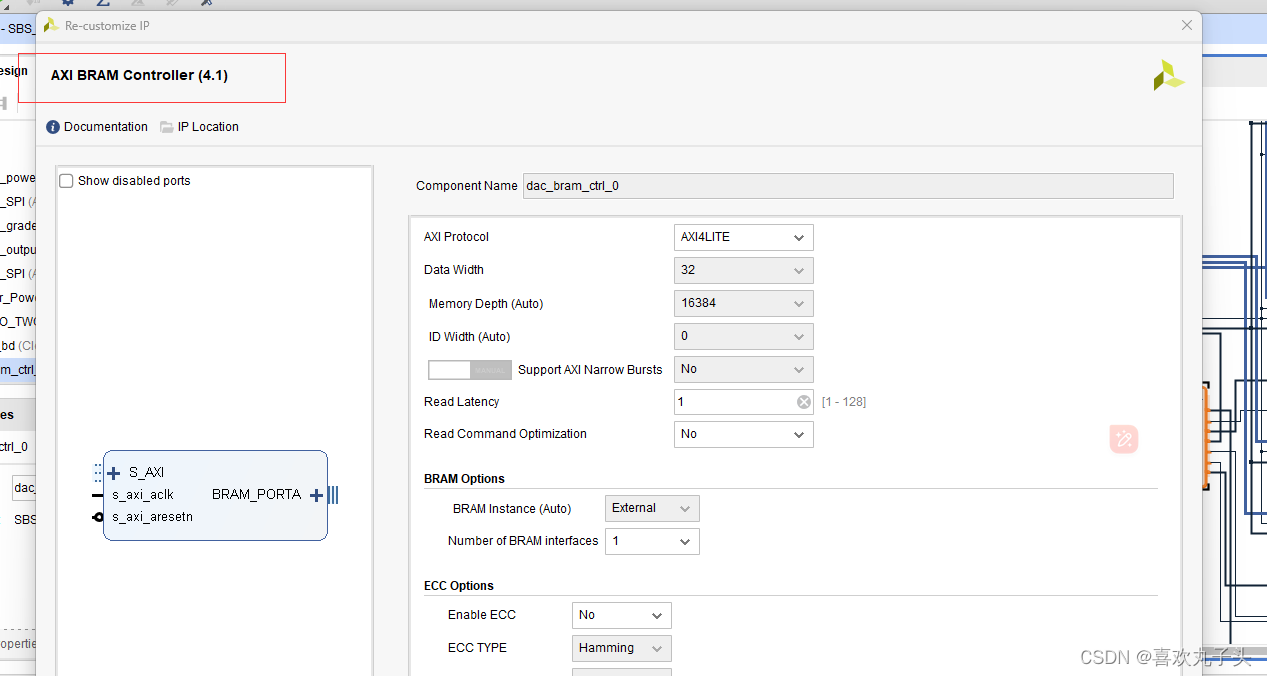

1、请教各位大佬一个问题,就是我在使用“AXI BRAM controller(4.1)”这个ip核来实现,PS将数据发送到PL的BRAM中去,然后PL从BRAM中读出数据的功能

2、然后我在网上找了一个相关的例程,就使用“XBram_WriteReg”这个函数就能将数据传输到PL的BRAM中去。

3、然后一运行就跳到了一个while死循环中去了。然后在网上搜索了一下,说是因为数据操作问题。

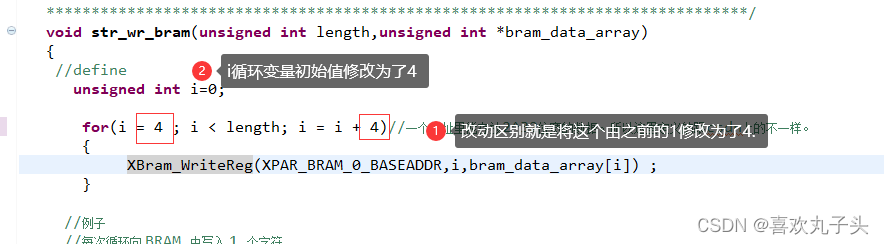

4、我就将代码修改为在网上找的例程一样的形式了,然后运行就不会调到死循环中去了。下面图片中是修改形式。

5、但我用ila在PL端抓取传输过来的接口信号,虽然数据和地址都有变化了,但往BRAM中的写地址变化是 4 8 12这种形式,相当于就是BRAM中有的地方的数据就没有写入进去,我想实现每个地址都有数据写入。就比如地址变化是0 1 2 4这样的。

解决方式

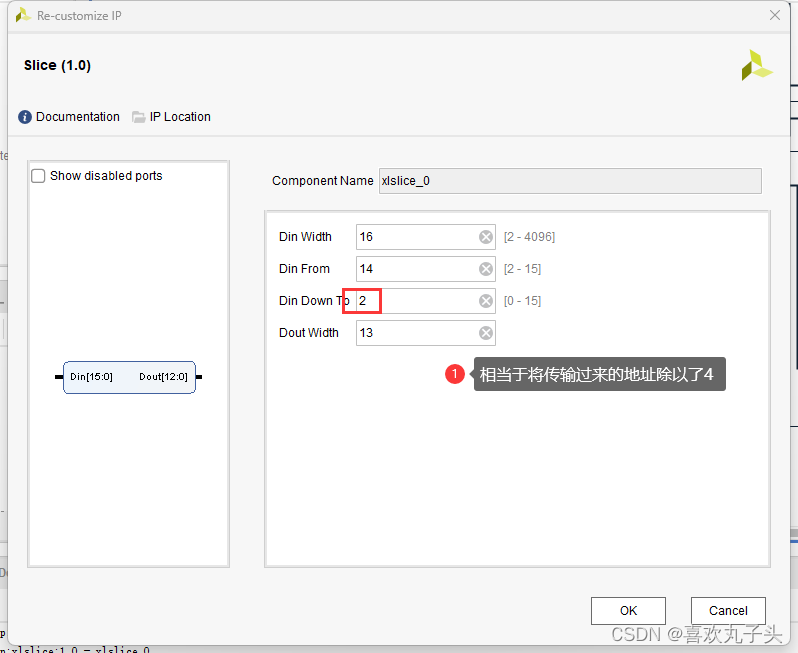

1、最后我在网上下载了一份,别人写的相关的"AXI BRAM controller(4.1)"相关的工程,然后一看代码,发现描述地址的时候,对地址进行了除以4的操作,这样就很好的解决了读到的地址,为什么不是0、1、2、3这种形式。

2、心得

真的,这个问题,当时让我困惑了很久,不知道怎么解决,在网上搜相关信息,都没有解释怎样让地址由4、8、12、16这种形式变为0、1、2、3这种形式。然后又想不到可以让地址除以4的这种方式。所以就有了这篇博客。

写在后面

不忘初心:写博客的主要目的就是记录自己容易忘记的东西,和自己在工作、学习中踩的坑。

因为自己在学习或工作中,遇到某个问题,在网上找资料,但资料很多,感觉很多人描述的都是偏理论多一点,实际怎样解决没有怎样详细介绍,对于我这种具体要点什么位置,都需要有教程的那种人来说,非常难受。所以遇到问题,在网上找到解决方式,总结一下,方便后续自己观看。

1039

1039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?