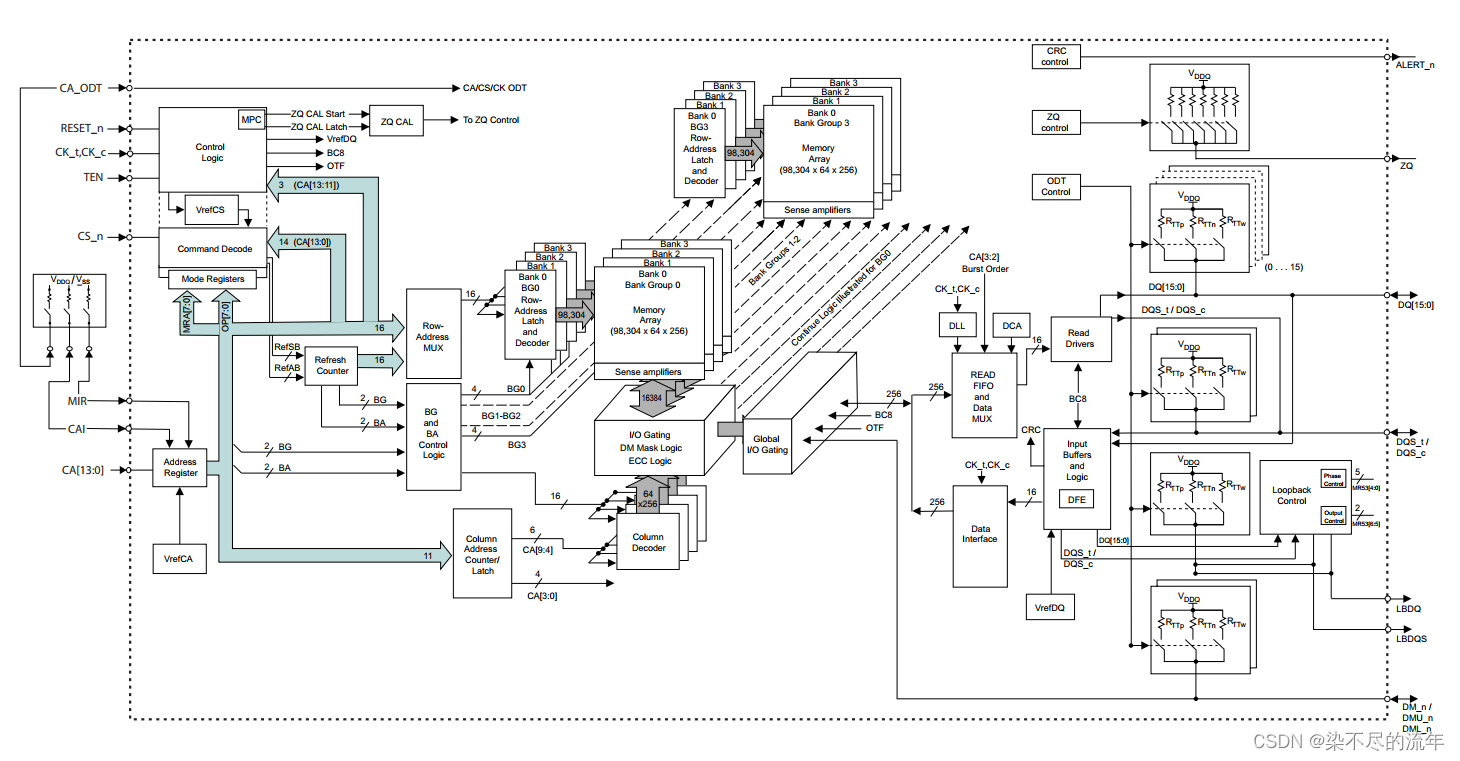

DDR5 SDRAM(双倍数据率五代同步动态随机存取存储器)的功能框图详细展现了其内部结构和各个关键模块,这些模块协同工作以实现高速数据传输和存储管理。以下是主要组成部分的详细介绍:

- Controller Logic (控制器逻辑)

这是DDR5内存系统的大脑,负责接收来自CPU或SoC的指令,解码这些指令,并生成适当的控制信号以执行读写操作、初始化、刷新等任务。控制器逻辑还负责管理与内存模块之间的数据传输,包括时序控制、错误处理、电源管理等高级功能的协调。

- Multi-purpose command (MPC)

DDR5 SDRAM和LPDDR5都采用了高级的命令集来支持更高效的内存管理和操作,多功能命令(MPC)是一个重要的新特性,它用于发出与接口初始化、训练和周期性校准相关的命令。MPC通过将片选(CS_n)置位并在时钟(CK)上升沿设置合适的命令地址(CA[4:0])来启动,具体命令定义根据JEDEC标准(如JESD79-5

DDR5 SDRAM的控制器逻辑、MPC、VrefCS、VrefCA、命令解码、模式寄存器、刷新计数器、行地址多路复用器、Bank Group控制逻辑等组件协同工作,实现高速数据传输和存储管理。MPC简化了初始化和训练流程,VrefCS和VrefCA确保信号完整性,模式寄存器扩展了配置选项,刷新计数器控制DRAM刷新,Bank Group提高并发性,列译码器定位存储单元,而Phase Control保证高速数据传输的稳定性。

DDR5 SDRAM的控制器逻辑、MPC、VrefCS、VrefCA、命令解码、模式寄存器、刷新计数器、行地址多路复用器、Bank Group控制逻辑等组件协同工作,实现高速数据传输和存储管理。MPC简化了初始化和训练流程,VrefCS和VrefCA确保信号完整性,模式寄存器扩展了配置选项,刷新计数器控制DRAM刷新,Bank Group提高并发性,列译码器定位存储单元,而Phase Control保证高速数据传输的稳定性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

927

927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?