FPGA学习

Quatus软件Verilog调用PLL ip核步骤

前言

PLL(Phase Locked Loop,即锁相环)是最常用的IP核之一,其性能强大,可以对输入到FPGA的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟,实际上,即使不想改变输入到 FPGA 时钟的任何参数,也常常会使用 PLL,因为经过 PLL 后的时钟在抖动(Jitter)方面的性能更好一些。Altera中的PLL是模拟锁相环,和数字锁相环不同的是模拟锁相环的优点是输出的稳定度高、相位连续可调、延时连续可调;缺点是当温度过高或者电磁辐射过强时会失锁(普通环境下不考虑该问题)。

一、 PLL核的工作流程

1、首先需要参考时钟(ref_clk)通过鉴频(FD)鉴相器(PD)和需要比较的时钟频率进行比较,我们以频率调整为例,如果参考时钟频率等于需要比较的时钟频率则鉴频鉴相器输出为0,如果参考时钟频率大于需要比较的时钟频率则鉴频鉴相器输出一个变大的成正比的值,如果参考时钟频率小于需要比较的时钟频率则鉴频鉴 相器输出一个变小的正比的值。

2、鉴频鉴相器的输出连接到环路滤波器(LF)上,用于控制噪声的带宽,滤掉高频噪声,使之稳定在一个值,起到将带有噪声的波形变平滑的作用。如果鉴频鉴相器之前的波形抖动比较大,经过环路滤波器后抖动就会变小,趋近于信号的平均值。

3、经过环路滤波器的输出连接到压控振荡器(VCO)上,环路滤波器输出的电压可以控制VCO输出频率的大小,环路滤波器输出的电压越大VCO输出的频率越高,然后将这个频率信号连接到鉴频鉴相器作为需要比较的频率。

如果ref_clk参考时钟输入的频率和需要比较的时钟频率不相等,该系统最终实现的就是让它们逐渐相等并稳定下来。如果ref_clk参考时钟的频率是50MHz,经过整个闭环反馈系统后,锁相环对外输出的时钟频率pll_out也是50MHz。

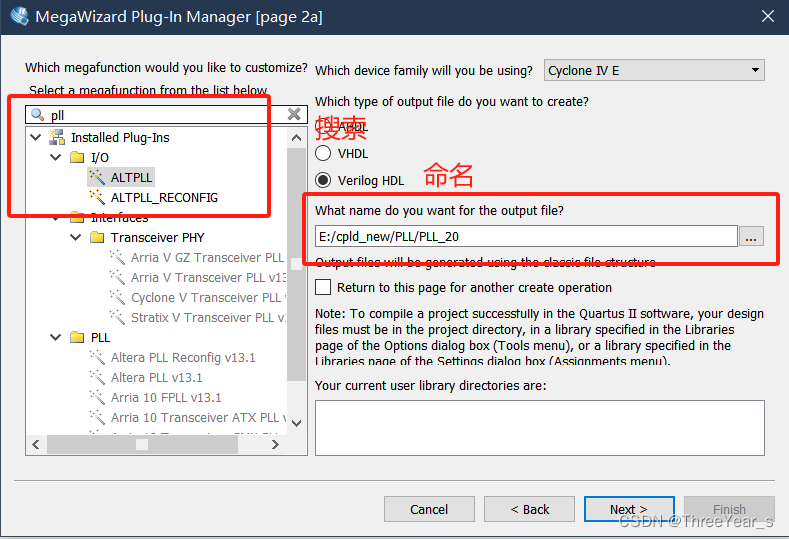

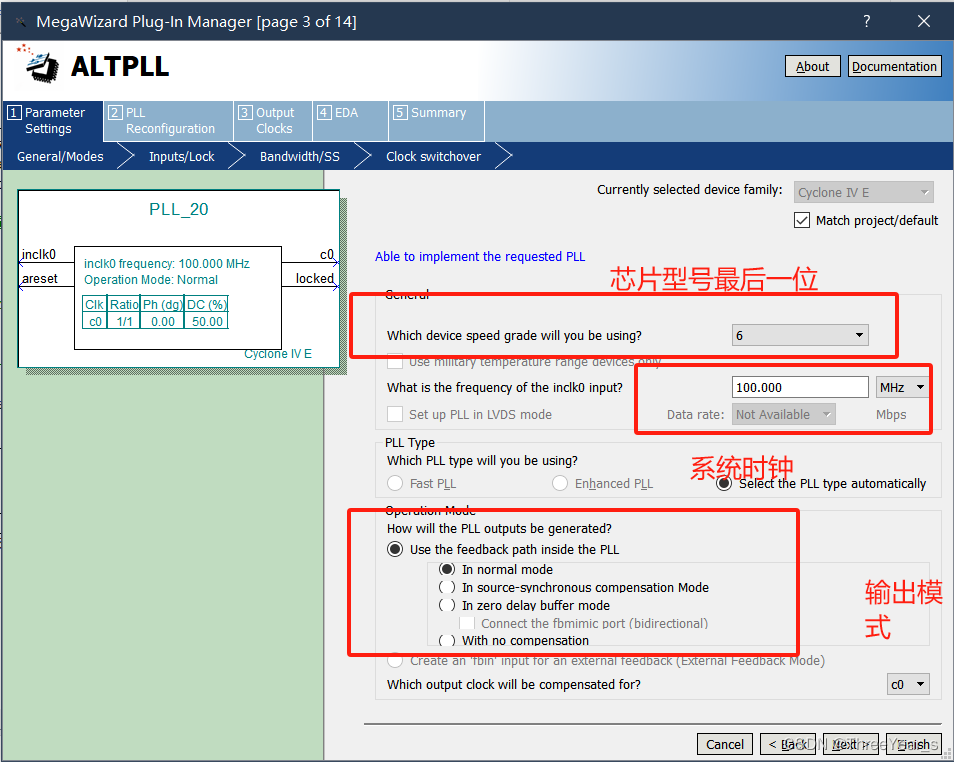

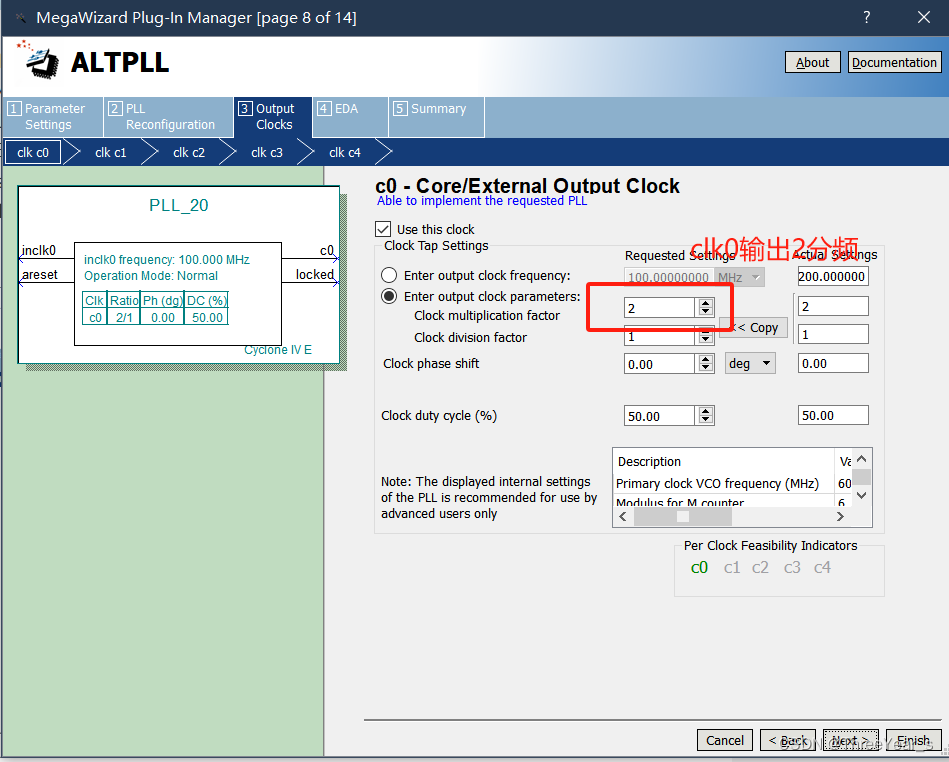

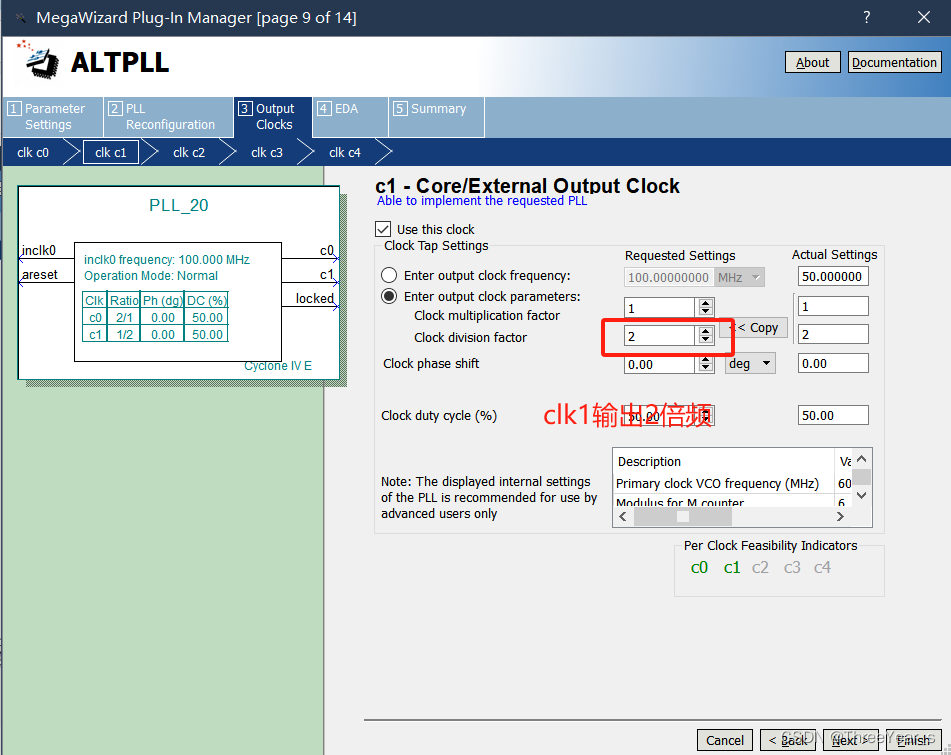

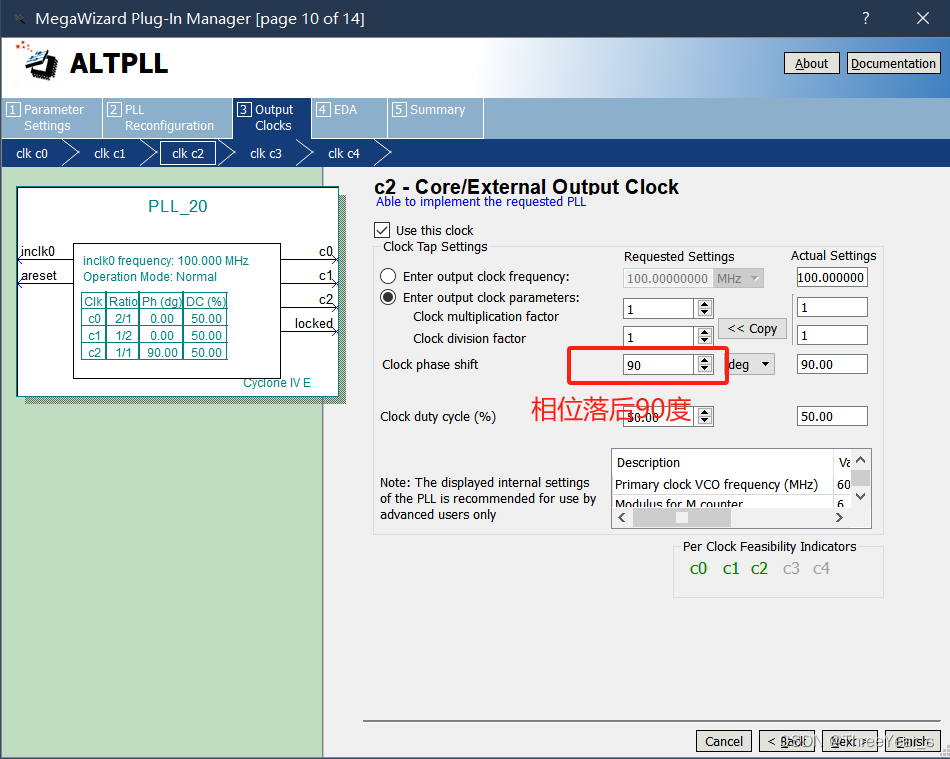

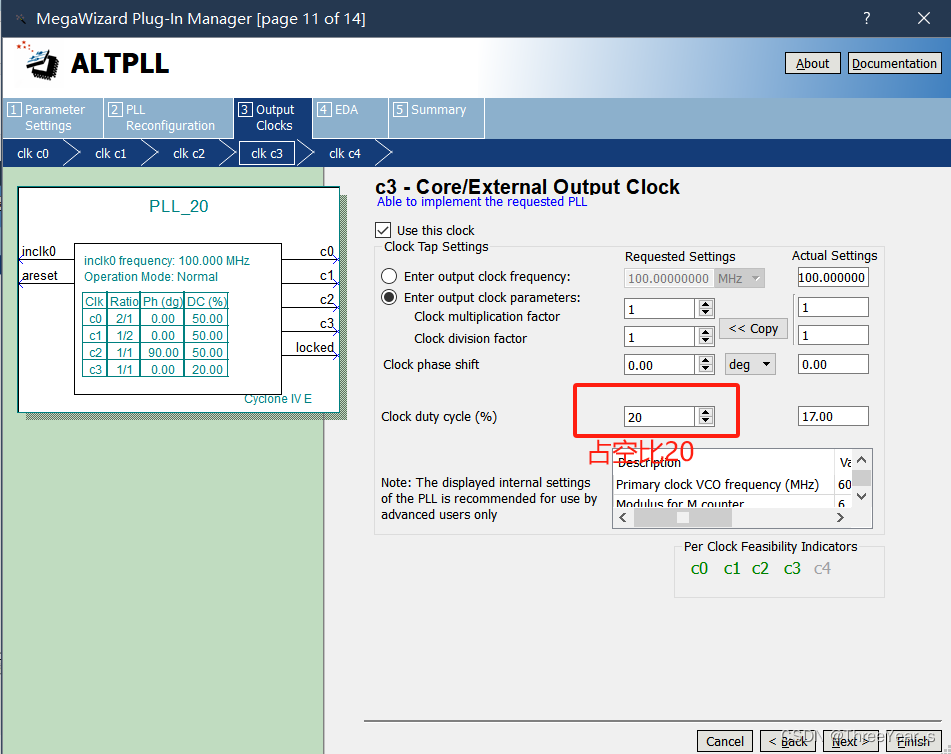

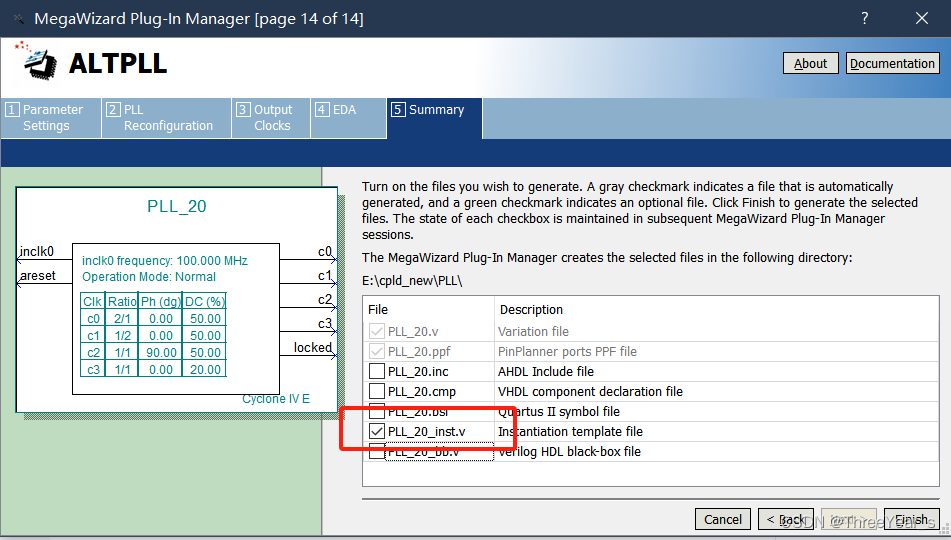

二、PLLip核配置流程

中间流程没有截图的部分全都是高级功能,暂不使用,默认即可

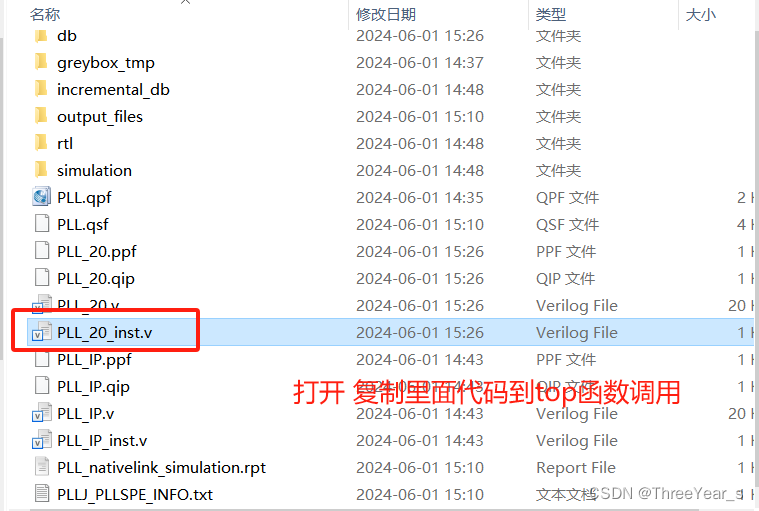

然后完成

PLL_20 PLL_20_inst (

PLL_20 PLL_20_inst (

.areset ( areset_sig ),

.inclk0 ( inclk0_sig ),

.c0 ( c0_sig ),

.c1 ( c1_sig ),

.c2 ( c2_sig ),

.c3 ( c3_sig ),

.locked ( locked_sig )

);

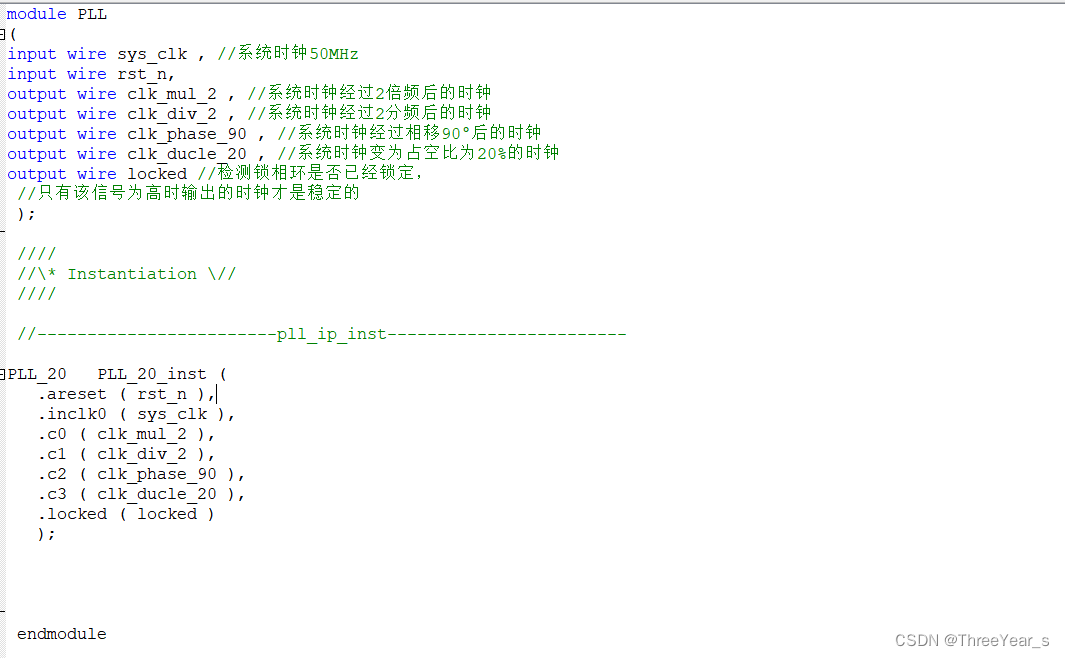

把括号里面的变量导进去

module PLL

(

input wire sys_clk , //系统时钟50MHz

input wire rst_n,

output wire clk_mul_2 , //系统时钟经过2倍频后的时钟

output wire clk_div_2 , //系统时钟经过2分频后的时钟

output wire clk_phase_90 , //系统时钟经过相移90°后的时钟

output wire clk_ducle_20 , //系统时钟变为占空比为20%的时钟

output wire locked //检测锁相环是否已经锁定,

//只有该信号为高时输出的时钟才是稳定的

);

//\* Instantiation \//

//------------------------pll_ip_inst------------------------

PLL_20 PLL_20_inst (

.areset ( rst_n ),

.inclk0 ( sys_clk ),

.c0 ( clk_mul_2 ),

.c1 ( clk_div_2 ),

.c2 ( clk_phase_90 ),

.c3 ( clk_ducle_20 ),

.locked ( locked )

);

endmodule

写tb文件开始仿真

// Copyright (C) 1991-2013 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "06/01/2024 14:50:33"

// Verilog Test Bench template for design : PLL

//

// Simulation tool : ModelSim-Altera (Verilog)

//

`timescale 1 ns/ 1 ps

module PLL_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg rst_n;

reg sys_clk;

// wires

wire clk_div_2;

wire clk_ducle_20;

wire clk_mul_2;

wire clk_phase_90;

wire locked;

// assign statements (if any)

PLL i1 (

// port map - connection between master ports and signals/registers

.clk_div_2(clk_div_2),

.clk_ducle_20(clk_ducle_20),

.clk_mul_2(clk_mul_2),

.clk_phase_90(clk_phase_90),

.locked(locked),

.rst_n(rst_n),

.sys_clk(sys_clk)

);

initial

begin

sys_clk <= 1'b1;

rst_n <= 1'b0;

end

always #10 sys_clk=~sys_clk;

endmodule

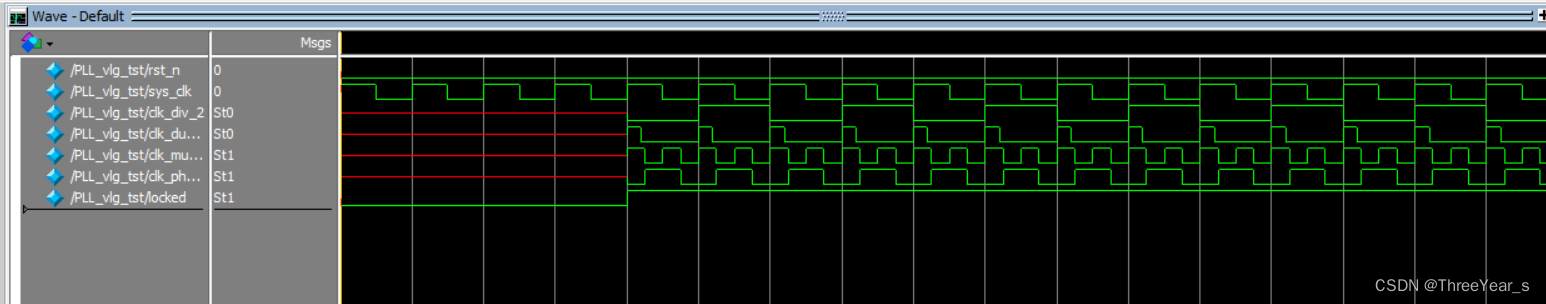

仿真结果正确,分别是2分频,2倍频,相位差90度,占空比20%

总结

我如果有分身就好了,那样的话就可以分开去爱你了~

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?