vivado配置

Verilog调用代码

module ram(

input wire sys_clk,

input wire wr_en,

input wire [7:0] addr,

input wire [7:0] data_in,

output wire [7:0] data_out

);

s_ram_8x256 inst1 (

.clka(sys_clk), // input wire clka

.wea(wr_en), // input wire [0 : 0] wea

.addra(addr), // input wire [7 : 0] addra

.dina(data_in), // input wire [7 : 0] dina

.douta(data_out) // output wire [7 : 0] douta

);

endmodule

仿真测试代码

`timescale 1ns / 1ns

module tb_ram();

reg sys_clk;

reg sys_rst_n;

reg wr_en;

reg [7:0]addr;

wire [7:0]data_in;

reg wr_flag;

wire [7:0]data_out;

initial

begin

sys_clk=1'b1;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end

always #10 sys_clk=~sys_clk;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n===1'b0)

wr_flag<=1'b0;

else if(addr==8'd255)

wr_flag<=1'b1;

else

wr_flag<=wr_flag;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n===1'b0)

wr_en<=1'b0;

else if(wr_flag==1'b1)

wr_en<=1'b0;

else

wr_en<=1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n===1'b0)

addr<=8'd0;

else if(addr==8'd255)

addr<=8'd0;

else

addr<=addr+1'b1;

assign data_in=(wr_en)?addr:8'd0;

ram ram_inst

(

.sys_clk (sys_clk),

.wr_en (wr_en),

.addr (addr),

.data_in (data_in),

.data_out (data_out)

);

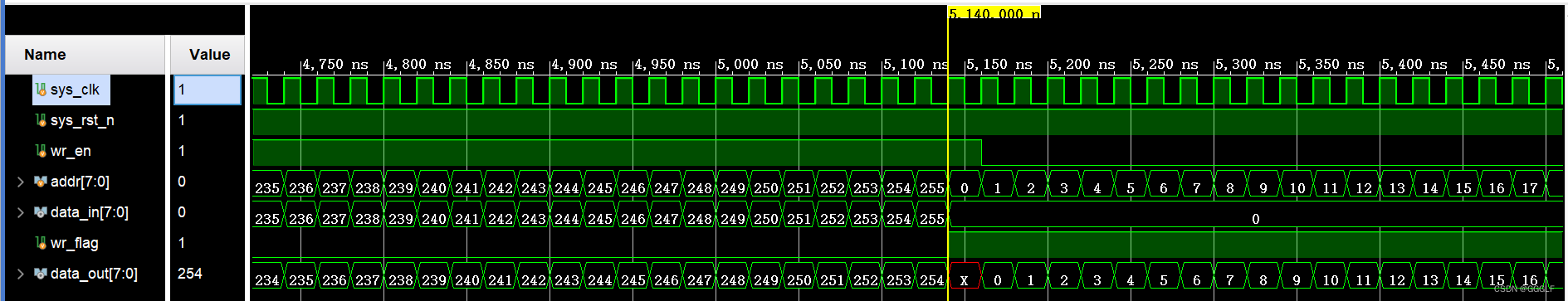

endmodulevivado仿真波形图

1923

1923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?