参考arm_cortexm3_processor_trm以及其他网络上的资料整理

文章目录

前言

NVIC全称是Nested Vectored Interrupt Controller (嵌套矢量中断控制器)。NVIC的特点是低延迟,支持中断嵌套,低功耗模式等技术。

一、NVIC功能描述

NVIC最多支持240个中断,每个中断最多支持256个可以动态更改的优先级。NVIC和处理器支持低功耗模式,以及休眠唤醒。NVIC同时也支持电平中断和脉冲中断。

1.NVIC中断

NVIC最多支持240个中断,每个中断最多支持256个优先级。可以在运行过程中动态地更改中断的优先级。需要注意的是NVIC是管理外部中断的,内部异常0~15由SCB管理。

NVIC和处理器核心接口是紧耦合的,以实现低延迟的中断处理和高效地处理延迟到达的中断。

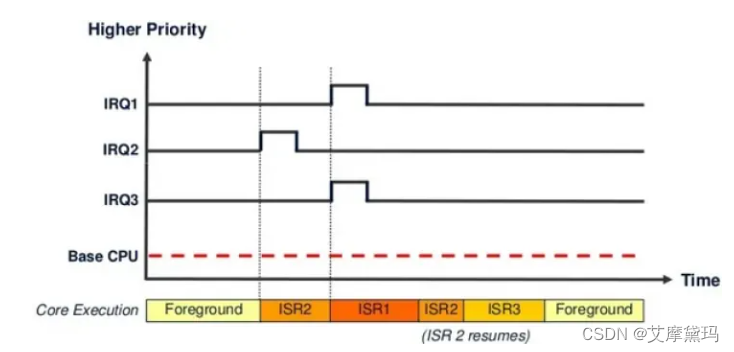

NVIC支持中断嵌套,中断尾链等。中断嵌套即在一个具有较低优先级的中断中处理另一个具有较高优先级的中断。例如,如果发生低优先级中断并正在执行时,发生了更高优先级的中断,ARM CPU 将暂停低优先级中断并开始执行高优先级中断,并且在高优先级中断服务程序执行完成后继续执行低优先级的中断服务程序,如图所示:

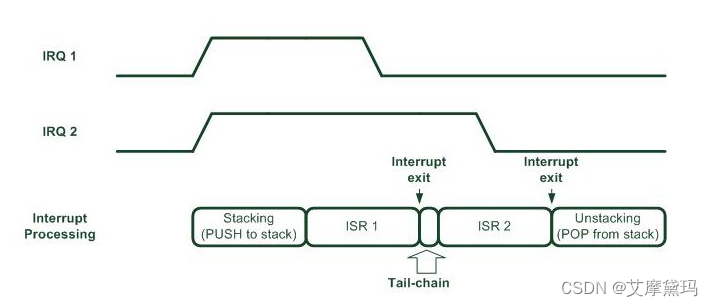

中断尾链即当触发中断(异常)时,主程序代码上下文被保存到堆栈,处理器分支到相应的中断向量以开始执行 ISR 处理程序。在 ISR 结束时将弹出保存在堆栈中的上下文,以便处理器可以恢复主程序代码指令。但是,当高优先级的ISR( Interrupt Service

Routine 中断服务例程)抢占低优先级ISR时,处理器会跳过上下文保存和恢复,直接处理第二个ISR,没有任何额外的开销。

NVIC寄存器支持从特权模式访问;支持字节、半字和字访问,数据存放使用小端模式little-endian。

2.低功耗模式

处理器和NVIC可以进入一个低功耗的睡眠模式,让唤醒中断控制器(WIC)根据中断屏蔽信息和收到的外部中断信号来决定是否唤醒处理器。

3.电平与脉冲中断

对于电平中断,如果在从中断程序返回之前该信号没有清除,则该中断将再次进入。电平中断主要用于FIFO和其他缓冲外设,这些外设会直到缓冲区为空时才会清除电平。

对于脉冲中断,如果在ISR执行期间重新插入脉冲中断,这样中断可以同时处于等待(pending)状态和活动(active)状态,ISR会运行两次。如果在中断在等待(pending)状态时另一个脉冲到达,则中断仍然处于等待(pending),ISR只运行一次。脉冲中断必须在Cortex-M3的FCLK的上升边缘进行采样,不支持异步采样。

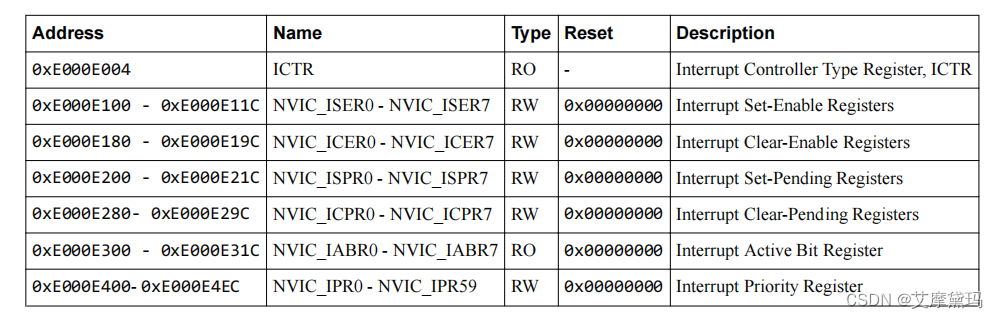

二、NVIC配置寄存器(programmers model)

1.寄存器总览

2.寄存器说明

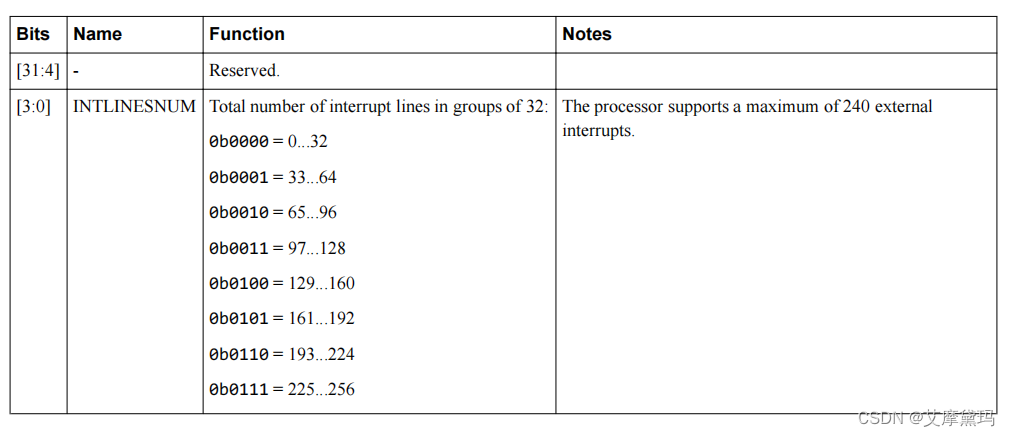

2.1 ICTR

支持的中断个数

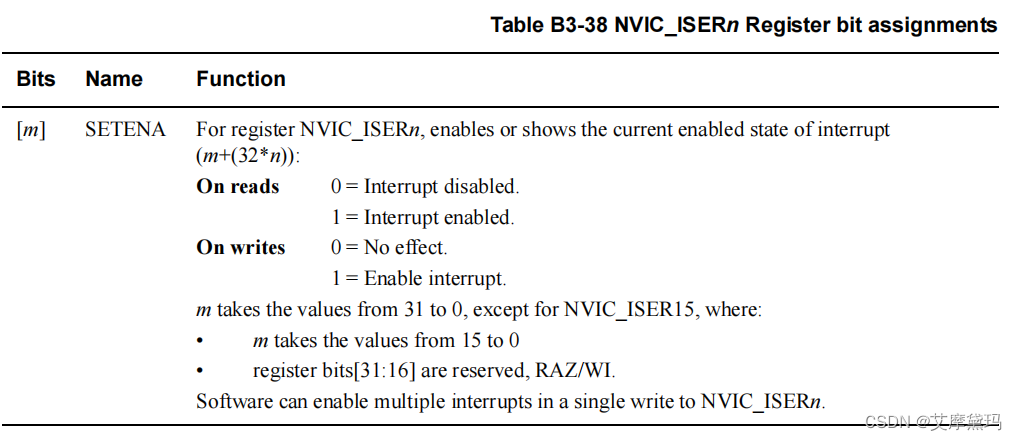

2.2 ISERn

中断使能寄存器 NVIC_ISERn[31:0] are the set-enable bits for interrupts (31+(32*n)) - (32*n).

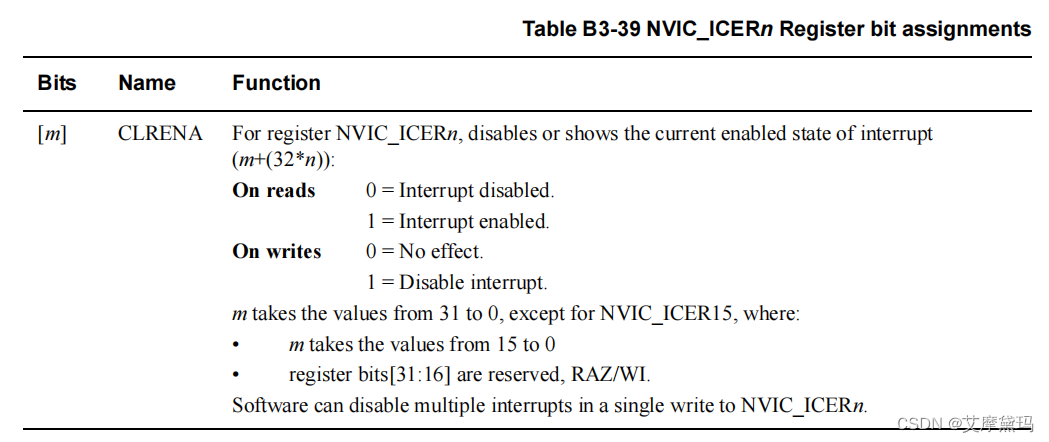

2.3 ICERn

中断清除寄存器 NVIC_ICERn[31:0] are the clear-enable bits for interrupts (31+(32*n)) - (32*n).

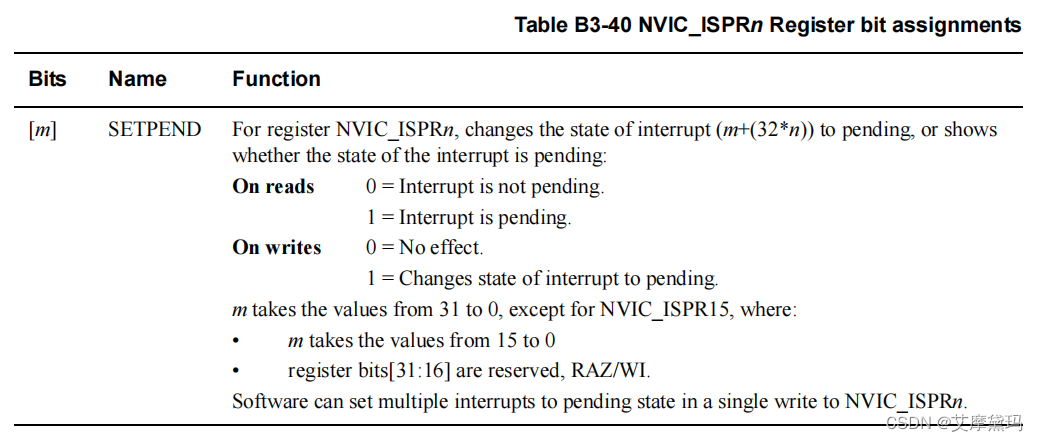

2.4 ISPRn

中断等待状态使能寄存器 NVIC_ISPRn[31:0] are the set-pending bits for interrupts (31+(32*n)) - (32*n).

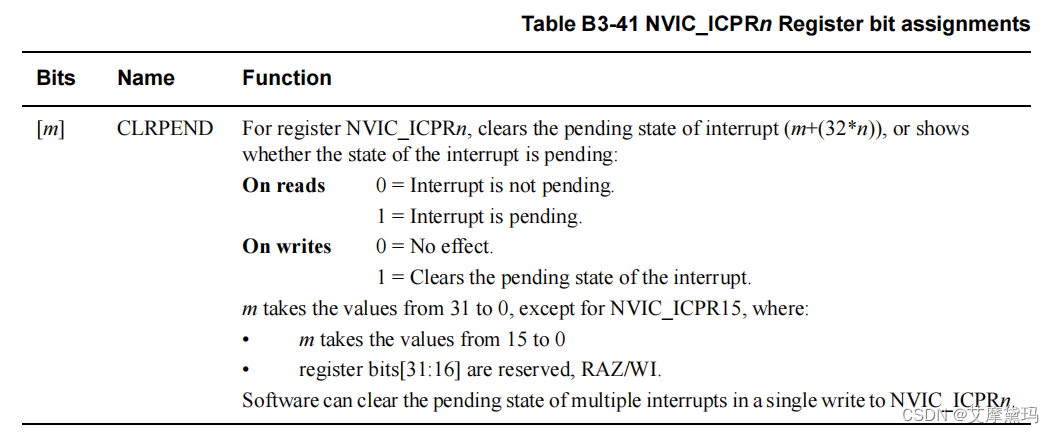

2.5 ICPRn

中断等待状态清除寄存器 NVIC_ICPRn[31:0] are the clear-pending bits for interrupts (31+(32*n)) - (32*n).

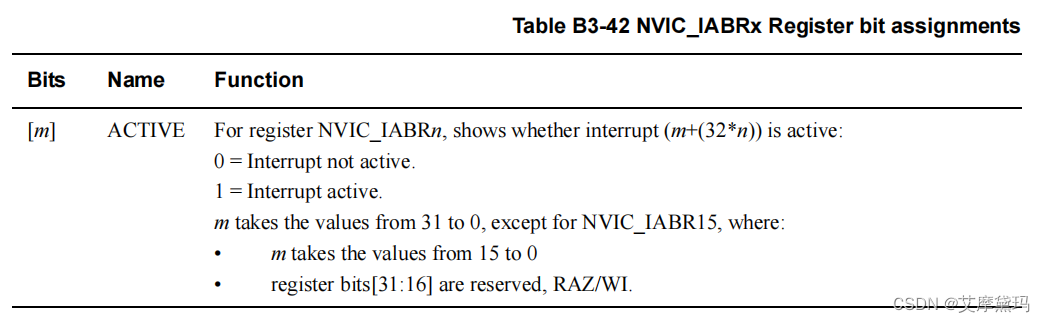

2.6 IABRn

NVIC_IABRn[31:0] are the active bits for interrupts (31+(32*n)) - (32*n).

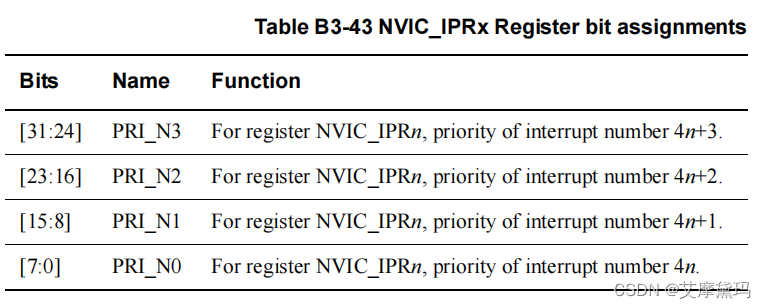

2.7 IPRn

中断优先级设置寄存器 Sets or reads interrupt priorities.

总结

本文仅仅简单介绍了NVIC的基本概念和功能。

NVIC是ARMCortex-M3处理器中的嵌套矢量中断控制器,支持240个中断和动态优先级设置。它具备低功耗特性,可进入睡眠模式,并处理电平和脉冲中断。中断嵌套允许在执行低优先级中断时响应高优先级中断,而低功耗模式下,唤醒由中断控制器根据中断信号决定。

NVIC是ARMCortex-M3处理器中的嵌套矢量中断控制器,支持240个中断和动态优先级设置。它具备低功耗特性,可进入睡眠模式,并处理电平和脉冲中断。中断嵌套允许在执行低优先级中断时响应高优先级中断,而低功耗模式下,唤醒由中断控制器根据中断信号决定。

1162

1162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?