- SIMM(Single Inline Memory Module,单列直插内存模块)

- DIMM(Dual Inline Memory Module,双列直插内存模块)

- RIMM(Rambus Inline Memory Module,内联内存模块)

DIMM(Dual Inline Memory Module,双列直插内存模块)与SIMM(single in-line memory module,单边接触内存模组)相当类似,不同的只是DIMM的金手指两端不像SIMM那样是互通的,它们各自独立传输信号,因此可以满足更多数据信号的传送需要。同样采用DIMM,SDRAM的接口与DDR内存的接口也略有不同,SDRAM DIMM为168Pin DIMM结构,金手指每面为84Pin,金手指上有两个卡口,用来避免插入插槽时,错误将内存反向插入而导致烧毁;DDR DIMM则采用184Pin DIMM结构,金手指每面有92Pin,金手指上只有一个卡口。卡口数量的不同,是二者最为明显的区别。DDR2 DIMM为240pin DIMM结构,金手指每面有120Pin,与DDR DIMM一样金手指上也只有一个卡口,但是卡口的位置与DDR DIMM稍微有一些不同,因此DDR内存是插不进DDR2 DIMM的,同理DDR2内存也是插不进DDR DIMM的,因此在一些同时具有DDR DIMM和DDR2 DIMM的主板上,不会出现将内存插错插槽的问题。

一、DIMM的分类:

1、UDIMM:

全称Unbuffered DIMM,即无缓冲双列直插内存模块,指地址和控制信号不经缓冲器,无需做任何时序调整,直接到达DIMM上的DRAM芯片。

UDIMM由于在CPU和内存之间没有任何缓存,因此同频率下延迟较小。

数据从CPU传到每个内存颗粒时,UDIMM需保证CPU到每个内存颗粒之间的传输距离相等,这样并行传输才有效,而这需要较高的制造工艺,因此UDIMM在容量和频率上都较低。定位在桌面市场

2、RDIMM:

3、LRDIMM:

全称Load Reduced DIMM,低负载双列直插内存模块。相比RDIMM,LRDIMM并未使用复杂寄存器,只是简单缓冲,缓冲降低了下层主板上的电力负载,但对内存性能几乎无影响。

此外,LRDIMM内存将RDIMM内存上的Register芯片改为iMB(isolation Memory Buffer)内存隔离缓冲芯片,直接好处就是降低了内存总线负载,进一步提升内存支持容量。

4、内存模组尺寸分类

详情请见:

https://blog.csdn.net/qq_24402247/article/details/121698474?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522171349195216800184196624%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=171349195216800184196624&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~baidu_landing_v2~default-1-121698474-null-null.142^v100^pc_search_result_base6&utm_term=rdimm%E7%BB%93%E6%9E%84&spm=1018.2226.3001.4187

二、DDR5 RDIMM

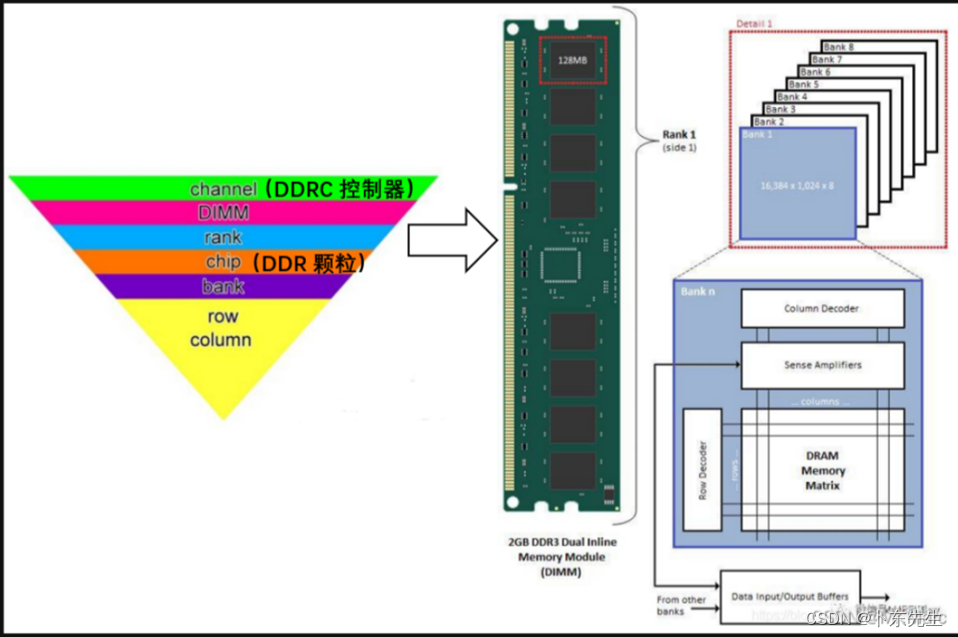

Channel:

一个主板上可能有多个插槽,用来插多根内存。这些槽位分成两组或多组,组内共享物理信号线。这样的一组数据信号线、对应几个槽位(内存条)称为一个channel(通道)。简单理解就是DDRC(DDR控制器),一个通道对应一个DDRC。CPU外核或北桥有两个内存控制器,每个控制器控制一个内存通道。内存带宽增加一倍。 (理论上)

Rank:

是一组内存芯片的集合,当芯片位宽x芯片数=64bits(内存总位宽)时,这些芯片就组成一个Rank。一般是一个芯片位宽8bit。,然后内存每面8个芯片,那么这一面就构成一个Rank (为了提高容量,有些双面内存条就有两个rank在DDR总线上可以用一根地线来区分当前要访问的是哪一组)。同一个Rank中的所有芯片协作来共同读取同一个Address(一个Rank8个芯片8bit= 64bit)这个Address的数据分散在这个Rank的不同芯片上。设计Rank的原因是这样可以使每个芯片的位宽小一些,降低复杂度Chip是内存条上的一个芯片,俗称内存颗粒。由图中是由8个bank组成了一个memory device.

Bank:

Bank是一个逻辑上的概念。一个Bank可以分散到多Chip上,一个Chip也可以包合多个Bank。Bank和Chip的关系可以参考下面的图,每次读数据时,选定一个Rank,然后同时读取每个chip上的同一bank.

Row/Column组成的Memeor Array:

Bank可以理解为一个二维数组bool Arry[Row][Column]。而Row/Column就是指示这个二维数组内的坐标。注意读取时每个Bank都读取相同的坐标。

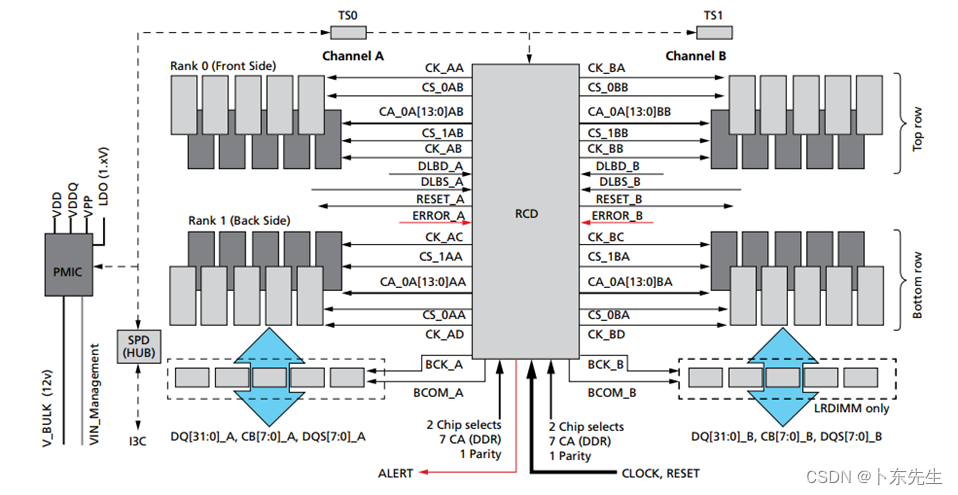

三、基于镁光的DDR5 RDIMM:

产品特点:

- 287/288 pins

- 支持ECC 错误检测和纠正

- DIMM上有SPD EEPROM,带有HUB功能,也加入了温度传感器

- 有两个分散的TS5温度传感器

- 有PMIC(Power Management Integrated Cicuit)电源管理集成电路

- 支持I2C/I3C-Basic 总线

- 有两个独立的I/O子通道已增加带宽

- 连接到RCD的DDR CA总线(Command/Address)

- 金手指连接

- 无卤(无卤要求:目前对于卤素的限值没有统一的标准,按照国际惯例卤素检测限值为 溴、氯含量分别小于 900ppm,(溴+氯)小于 1500ppm ,多氟和碘一般没有明确要求,通常客户提出的无卤要求就是不含有,要求检测结果为ND,具体限值要求需要客户根据接受程度自行提出要求。)

- Fly-by的拓扑结构

- 终端时钟、控制、CA总线

功能框图:

概述:

DDR5模块使用两组差分信号(DQS_t和DQS_c)来捕获数据,使用CK_t和CK_c来捕获命令、地址和控制信号。差分时钟和数据频闪确保这些信号具有特殊的抗噪性,并提供精确的交叉点来捕获输入信号。

拓扑结构:

DDR5模块使用比早期DDR技术更快的时钟速度,使得信号质量比以往任何时候都更重要。为了改善信号质量,时钟、控制、命令和地址总线以fly-by的拓扑结构路由,其中每个DRAM上的时钟、控制、命令和地址引脚都连接到单个电路并有终端(而不是树形结构,在树形结构中,终端在连接器附近的模块上)。fly-by拓扑固有的时钟和DQS信号之间的时间偏差可以使用DDR5的写均衡特性来解决。

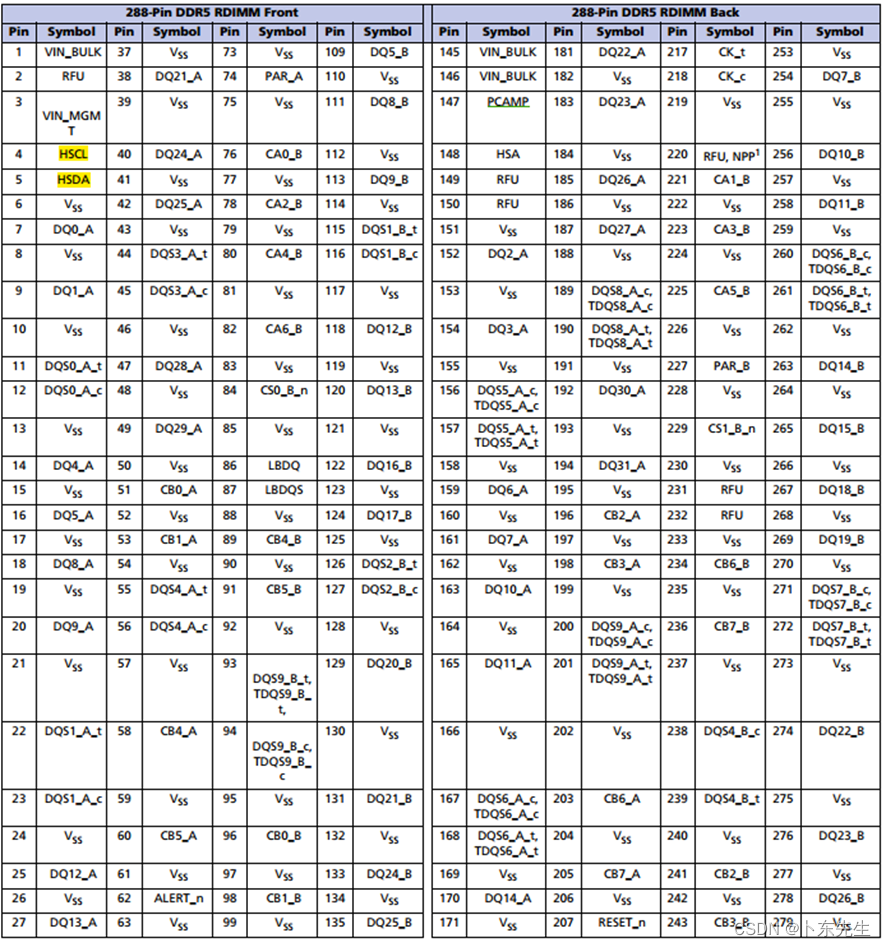

引脚分布:

HSCL:总线时钟用于选通数据到集线器设备(SPD HUB)。当漏极打开时,系统主板上需要一个上拉电阻。

HSDA:I2C / I3C-Basic数据线。当漏极打开时,系统主板上需要一个上拉电阻。

HSA:(Host Sideband Bus Device ID)地址输入到集线器或其他客户端设备,以区分I3C基本地址范围内的相同设备。连接到GND, HSA在主板上有不同的电阻值来识别DIMM插槽地址。有关更多信息,请参阅SPD集线器规范。

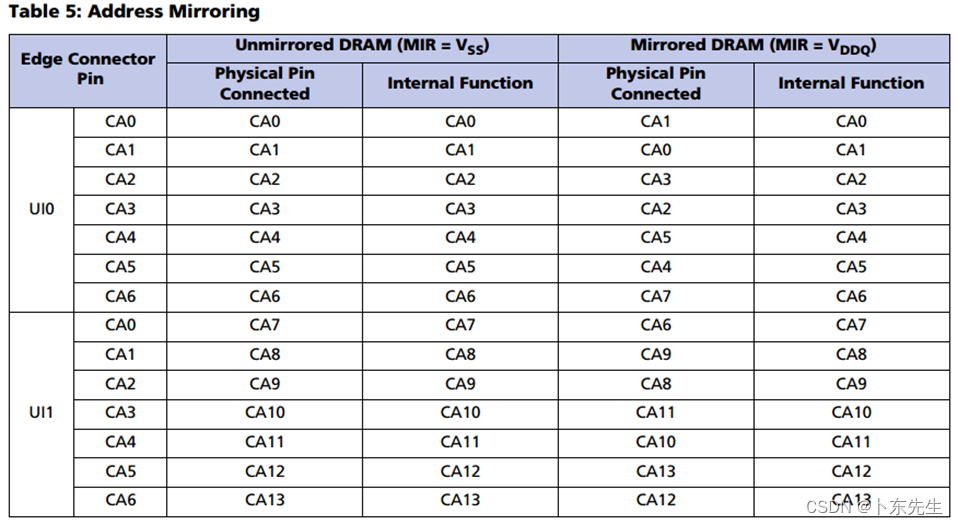

Address Mapping

DDR5 SDRAM有一个MIR输入引脚。该引脚绑扎(连接)到PCB上的VSS或VDDQ。该引脚用于通知SDRAM设备,它正在被配置为镜像模式而不是标准模式。将MIR引脚绑在VDDQ上,SDRAM内部将偶数CA与下一个更高的奇数CA交换。通常情况下,如果不需要CA镜像,则必须将MIR引脚绑在VSS上。

在Registered DDR5模块上,RCD将把输入的主机接口7位DDR(双数据速率)CA总线(边缘连接器CA[6:0])扩展到DRAM接口上的14位。下表说明了边缘连接器引脚如何映射到DRAM物理CA引脚和内部CA功能,通过DDR输入到RCD (UI0 vs. UI1)。

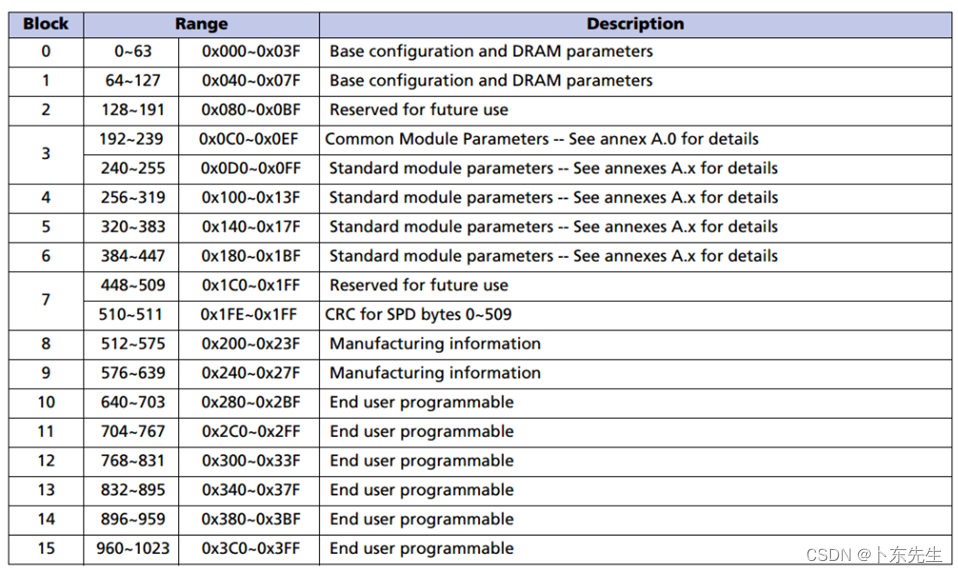

SPD HUB

DDR5 SDRAM模块包含一个具有集线器功能的SPD EEPROM (SPD5 hub),集成了温度传感器(TS)。SPD数据存储在一个符合JEDEC JC-42.4标准的1024字节EEPROM中,该EEPROM被分为16个块,每个块64字节,每个块可通过软件命令选择写保护。如下表所示:

SPD集成的温度传感器:

集成的热传感器(TS)持续监测PCB模块的温度并更新温度数据寄存器。

主机可随时从总线读取温度数据,为主机提供模块温度的实时数据。多个可编程和只读温度寄存器可用于创建基于系统要求的自定义温度传感解决方案。有关配置和读取集成热传感器的详细信息,请参阅DDR5 SPD5 Hub规范。

RCD:

Registered DDR5 SDRAM模块是由寄存器和锁相环(PLL)组成的注设备。设备符合JEDEC DDR5 RCD规范。请参阅JESD82-511 (DDR5RCD01)和JESD82-512 (DDR5RCD02)规范了解更多细节。

控制字

DDR5 RDIMM和LRDIMM上使用的RCD设备包含称为控制字的配置寄存器,主机使用这些寄存器根据模块设计确定的标准配置RCD。控制字可以由主控制器通过DRAM命令/地址总线通过模式寄存器写入(mode register write ---MRW)或i3c -基本/I2C边带总线接口进行编程。RCD边带总线接口与模块温度传感器、SPD集线器和PMIC位于同一边带总线接口上。

奇偶校验

RCD包含一个奇偶校验功能。缺省情况下,当设备设置为I3C-basic模式时,奇偶校验功能自动开启。开启该功能后,主机可以关闭该功能。RCD从存储器控制器在DPAR输入处接收奇偶校验位,并将其与在合格命令/地址输入上接收的数据进行比较;它在其开漏ALERT_n引脚上指示是否发生了奇偶校验错误。如果启用奇偶校验,RCD将在没有奇偶校验错误时将命令转发到SDRAM。如果禁用奇偶校验错误功能,无论是否发生奇偶校验错误,RCD都会将采样命令转发到SDRAM。在控制字WRITE操作期间也检查奇偶校验,除非奇偶校验被禁用。在1UI和2UI命令的两个子通道上分别检查奇偶校验。一个子通道上的奇偶校验错误不会影响另一个子通道的操作。

Rank Address

美光模块上每个子通道(CS0_n和CS1_n)的两个芯片选择输入用于选择特定等级的DRAM。每个子通道有两个芯片选择输入(CS0x_n和CS1x_n)。

Power Management Integrated Circuit Operation(PMIC)

TS5

TS5(第五代温度传感器)设备具有通过双线总线控制和读取的热感测能力。TS5设备使用1.8V标称电源(VDDSPD)和1.0V标称电源(VDDIO)。TS5设备旨在在1.0V的电压下, I2C模式高达12.5 MHz,或在1.0V至3.3 V(等级依赖)I2C总线上工作高达1 MHz。TS5设备用于连接I2C或i3c基本总线,这些总线在共享总线上有多个设备,并且必须在同一总线上使用固定地址进行唯一寻址。所有TS5设备都响应双线总线上特定的预定义设备选择码。有关详细信息,请参阅最新版本的JEDEC JESD302-1 TS511x规范。

四、DDR5与DDR4的对比

| 128b+8b SEC,错误检查和消除 | |||

| MIR(“镜像”引脚) | |||

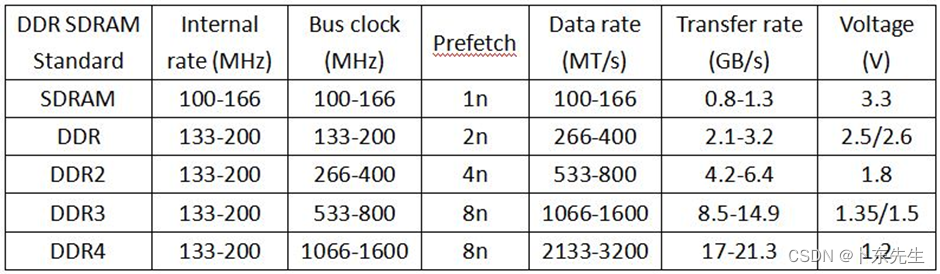

五、DDR4, DDR3, DDR2, DDR1 及SDRAM各有何不同

SDRAM(Synchronous Dynamic Random Access Memory):为同步动态随机存取内存,前缀的Synchronous告诉了大家这种内存的特性,也就是同步。1996年底,SDRAM开始在系统中出现,不同于早期的技术,SDRAM是为了与中央处理器的计时同步化所设计,这使得内存控制器能够掌握准备所要求的数据所需的准确时钟周期,因此中央处理器从此不需要延后下一次的数据存取。举例而言,PC66 SDRAM以66 MT/s的传输速率运作;PC100 SDRAM以100 MT/s的传输速率运作;PC133 SDRAM以133 MT/s的传输速率运作,以此类推。

SDRAM亦可称为SDR SDRAM(Single Data Rate SDRAM),Single Data Rate为单倍数据传输率,SDR SDRAM的核心、I/O、等效频率皆相同,举例而言,PC133规格的内存,其核心、I/O、等效频率都是133MHz。而Single Data Rate意指SDR SDRAM在1个周期内只能读写1次,若需要同时写入与读取,必须等到先前的指令执行完毕,才能接着存取。

DDR SDRAM(Double Data Rate SDRAM):为双信道同步动态随机存取内存,是新一代的SDRAM技术。别于SDR(Single Data Rate)单一周期内只能读写1次,DDR的双倍数据传输率指的就是单一周期内可读取或写入2次。在核心频率不变的情况下,传输效率为SDR SDRAM的2倍。第一代DDR内存Prefetch为2bit,是SDR的2倍,运作时I/O会预取2bit的资料。举例而言,此时DDR内存的传输速率约为266~400 MT/s不等,像是DDR 266、DDR 400都是这个时期的产品。

DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。DDR2内存Prefetch又再度提升至4 bit(DDR的两倍),DDR2的I/O频率是DDR的2倍,也就是266、333、400MHz。举例:核心频率同样有133~200MHz的颗粒,I/O频率提升的影响下,此时的DDR2传输速率约为533~800 MT/s不等,也就是常见的DDR2 533、DDR2 800等内存规格。

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。DDR3内存Prefetch提升至8 bit,即每次会存取8 bits为一组的数据。DDR3传输速率介于 800~1600 MT/s之间。此外,DDR3 的规格要求将电压控制在1.5V,较DDR2的1.8V更为省电。DDR3也新增ASR(Automatic Self-Refresh)、SRT(Self-Refresh Temperature)等两种功能,让内存在休眠时也能够随着温度变化去控制对内存颗粒的充电频率,以确保系统数据的完整性。

DDR4 SDRAM(Double Data Rate Fourth SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200 MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank Group具备独立启动操作读、写等动作特性,Bank Group 数据组可套用多任务的观念来想象,亦可解释为DDR4 在同一频率工作周期内,至多可以处理4 笔数据,效率明显好过于DDR3。 另外DDR4增加了DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,讓DDR4記憶體在更快速與更省電的同時亦能夠增強信號的完整性、改善資料傳輸及儲存的可靠性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?