欢迎关注我的微信公众号:射频工程师的日常,每天给你分享技术干货

1. Buck Layout注意事项

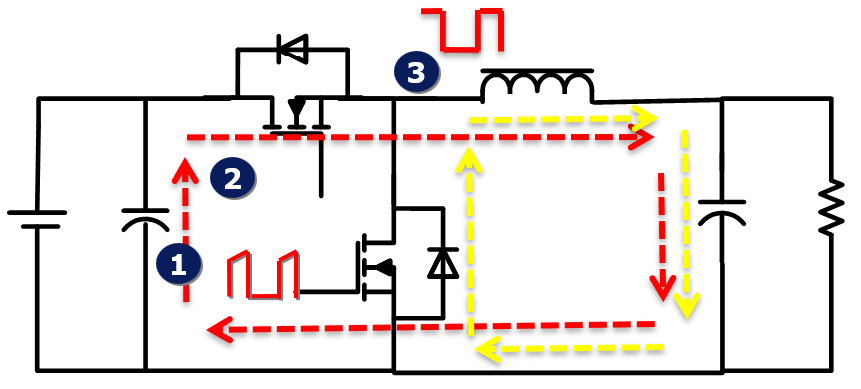

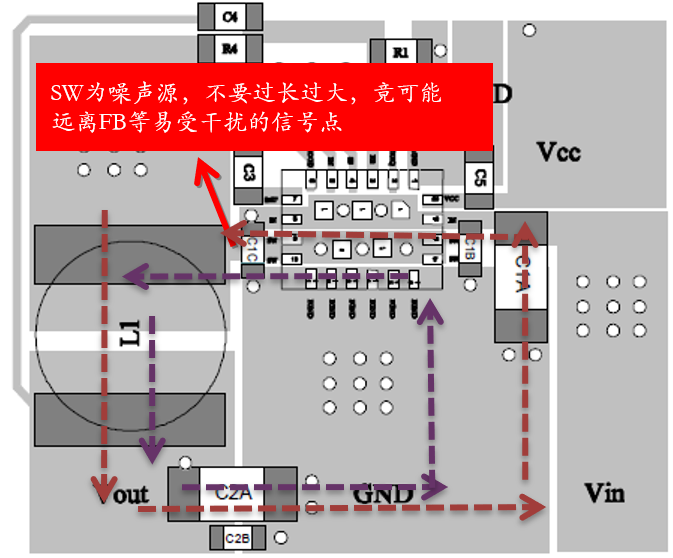

① 输入电容就近放在芯片的输入Vin和功率地PGND,减少寄生电感的存在,因为输入电流不连续,寄生电感引起的噪声对芯片的耐压以及逻辑单元造成不良影响;

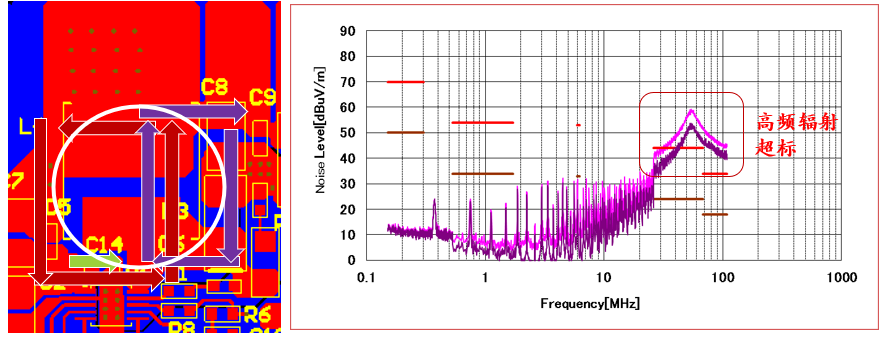

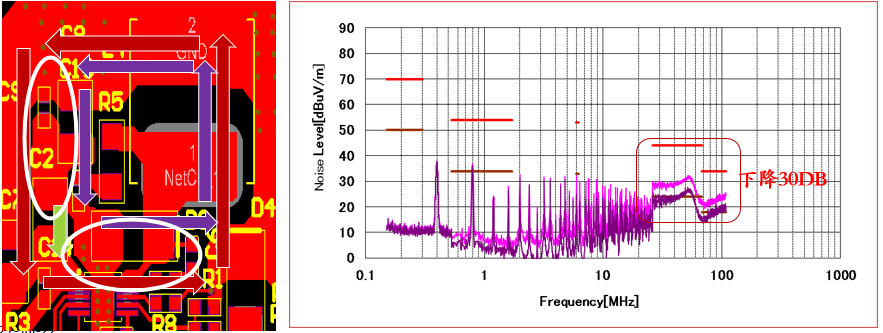

② 功率回路尽可能的短粗,保持较小的环路面积,较少噪声的发射;

③ SW点是噪声源,保证电流的同时保持尽量小的面积,远离敏感的易受干扰的位置;

④ VCC电容应就近放置在芯片的VCC管脚和芯片的信号地之间,尽量在一层,没有过孔对于信号地(AGND)和功率地PGND在一个管脚的芯片,同样就近和该管脚连接;

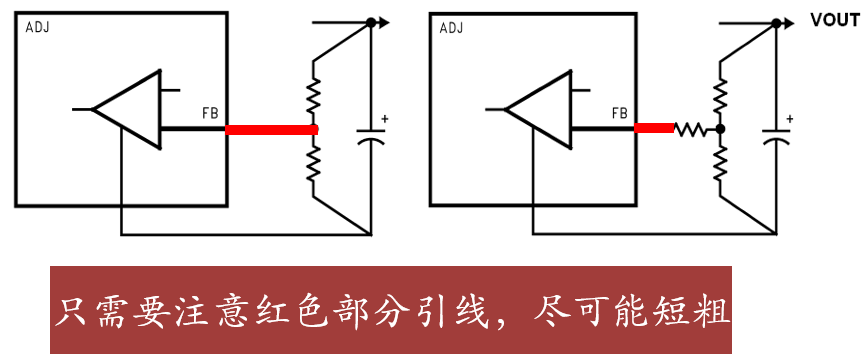

⑤ FB是芯片最敏感,最容易受干扰的部分,是引起系统不稳定的最常见原因。

-

FB电阻连接到FB管脚尽可能短,减少噪声的耦合;

-

远离噪声源,SW点,电感,二极管;

-

FB的下分压电阻通常接信号地AGND。

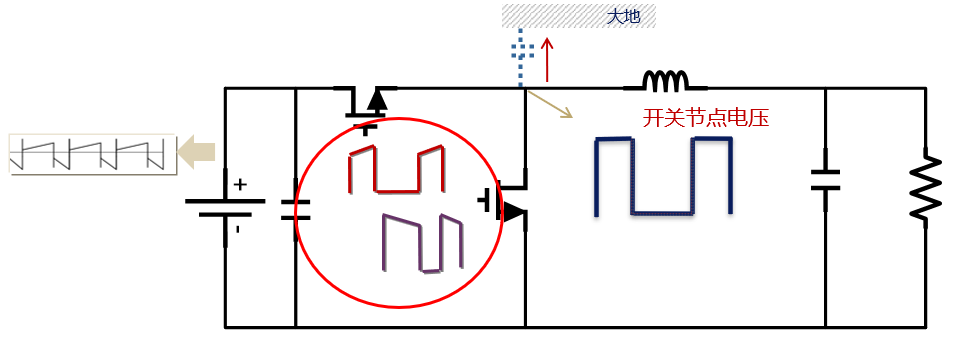

2. DCDC的噪声来源

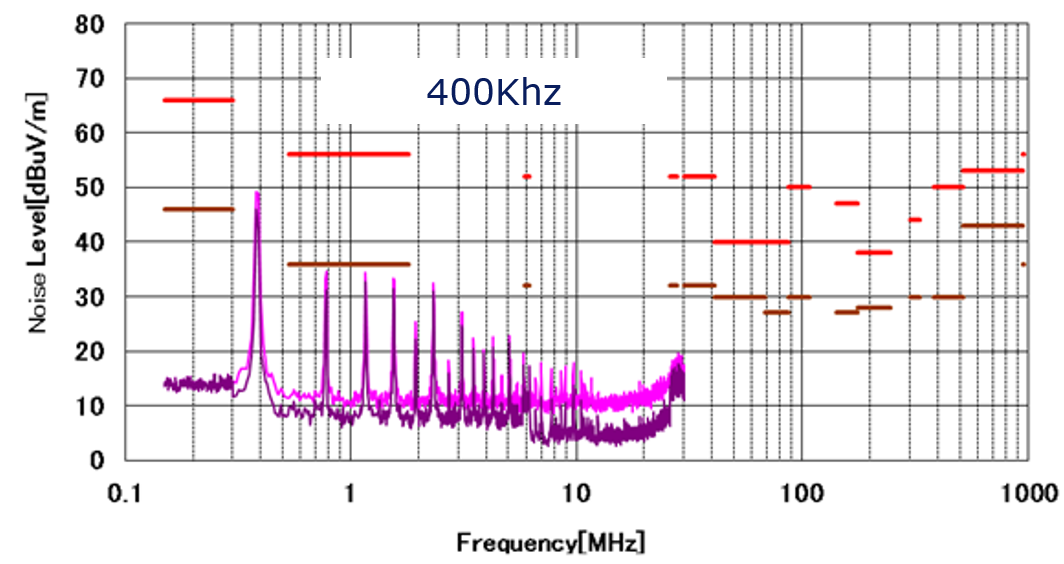

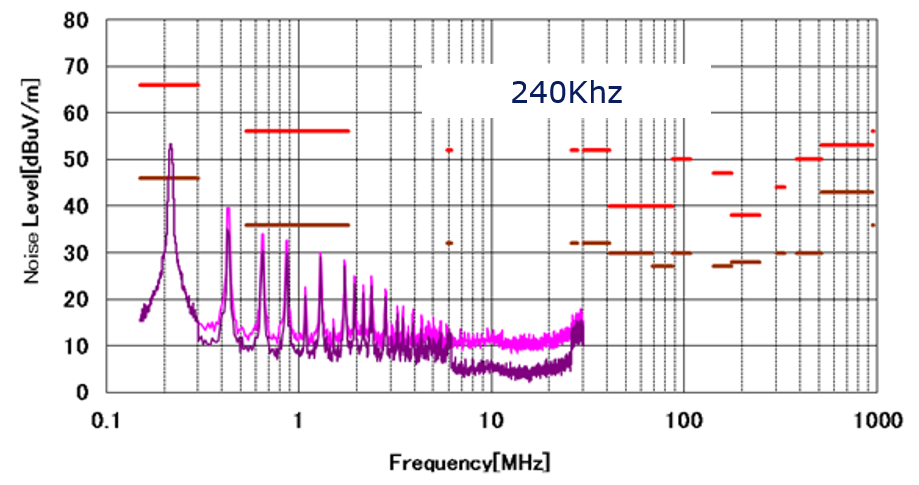

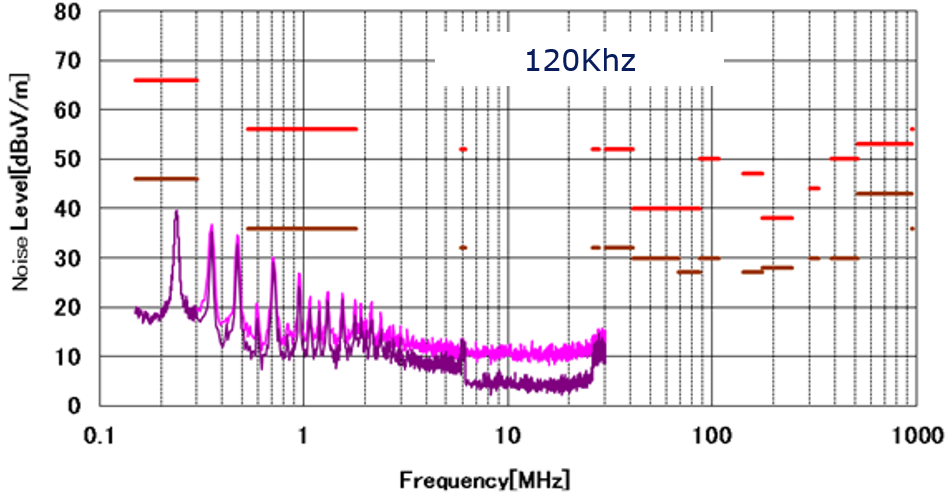

a. BUCK电路EMI的主要来源:高频电流环路和电压跳变

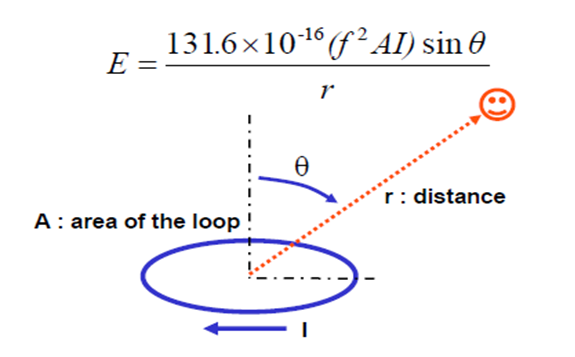

b. 环路天线原理:噪声分量和电流大小,环路面积和频率成正比,和距离成反比

3. DCDC的噪声抑制办法

a. 减慢开关速度,主要和上升时间Tr有关;

b. 减小高频环路面积,增加Vin和GND电容可以减少高频环路的电流;

c. 减小开关节点面积,降低容性耦合。

本文介绍了Buck电路布局的关键技巧,如输入电容布局、功率路径短化、SW点设计、VCC电容布置,以及DCDC控制器的噪声来源、环路天线原理和抑制方法。重点讲解了减慢开关速度、减小环路面积和节点面积来降低噪声的影响。

本文介绍了Buck电路布局的关键技巧,如输入电容布局、功率路径短化、SW点设计、VCC电容布置,以及DCDC控制器的噪声来源、环路天线原理和抑制方法。重点讲解了减慢开关速度、减小环路面积和节点面积来降低噪声的影响。

345

345

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?