施加约束

时序约束

施加时序约束主要是为了保证电路中每一条时序路径都能够处于约束下。在约束后查看电路的setup time和hold time是否满足要求,如果不满足,那么就需要返回代码检查修改或是添加修改新的约束。

DC中我们能够施加的时序约束一般有以下几种:

指定时钟: create_clock period 20 [get_ports CLK]

设置don’t touch属性:set_dont_touch_network [get_clocks Clk]加上这一句主要是为了DC在综合时不对CLK信号进行优化,因为布线之后还会根据布线情况对时钟树进行专门的优化,所以不用在这里做。

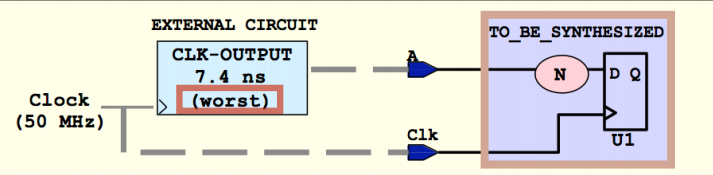

约束input delay:set_input_delay -max 7.4 -clock Clk [get_ports A]

input delay的值就是指外部电路的最大输入延时,在计算slack时,要将这个因素考虑进去,它主要影响setup time。

约束output delay:set_output_delay -max 5.4 -clock Clk [get_ports B]

DRC(Design Rule Constrains)

DRC约束主要由工艺库厂商提供,但是在实际中可以约束的更紧一点保证可靠性,DRC如

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

358

358

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?