使用xilinx官方提供的MIG IP核进行设计,接口协议为AXI,关于AXI协议的内容此处不做过多介绍。

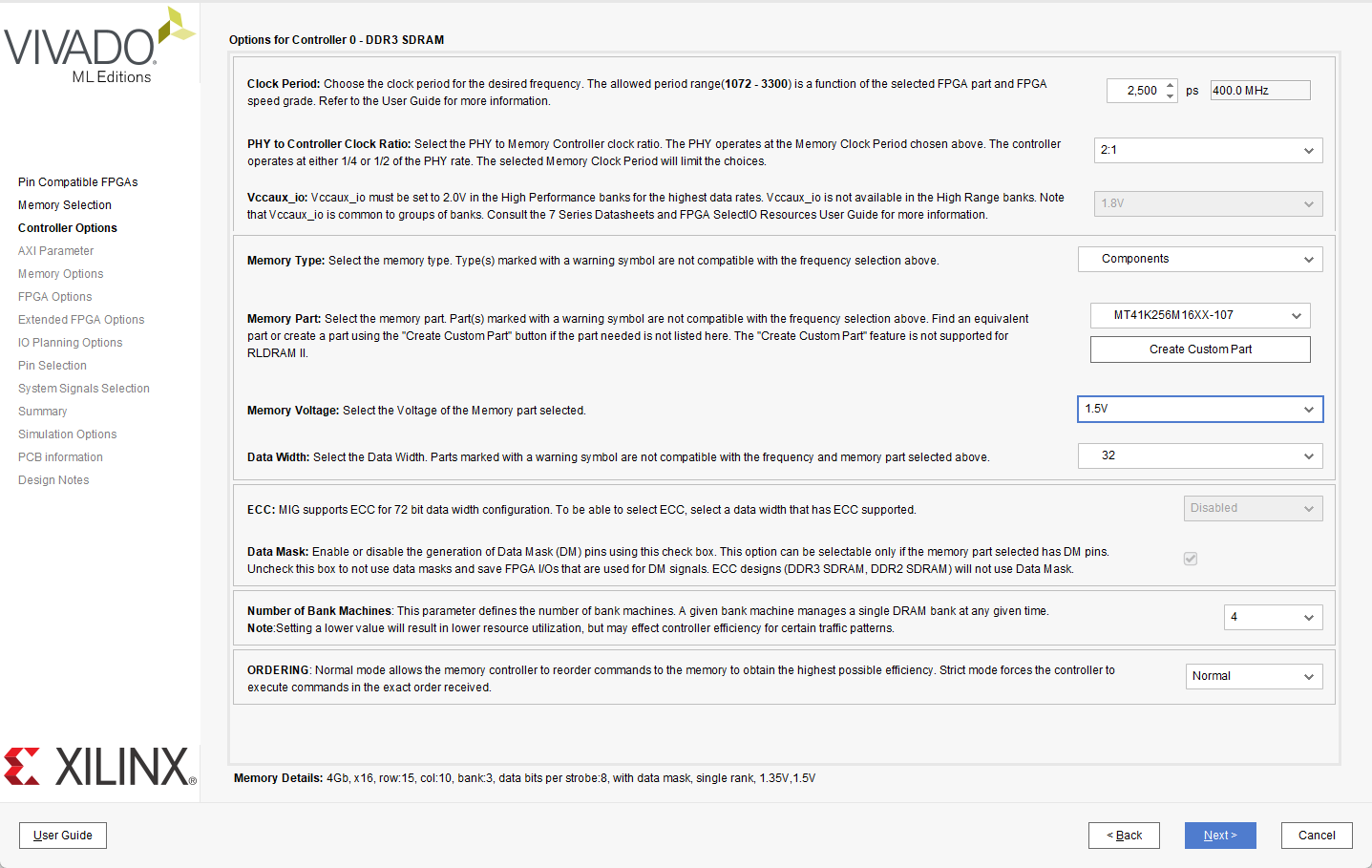

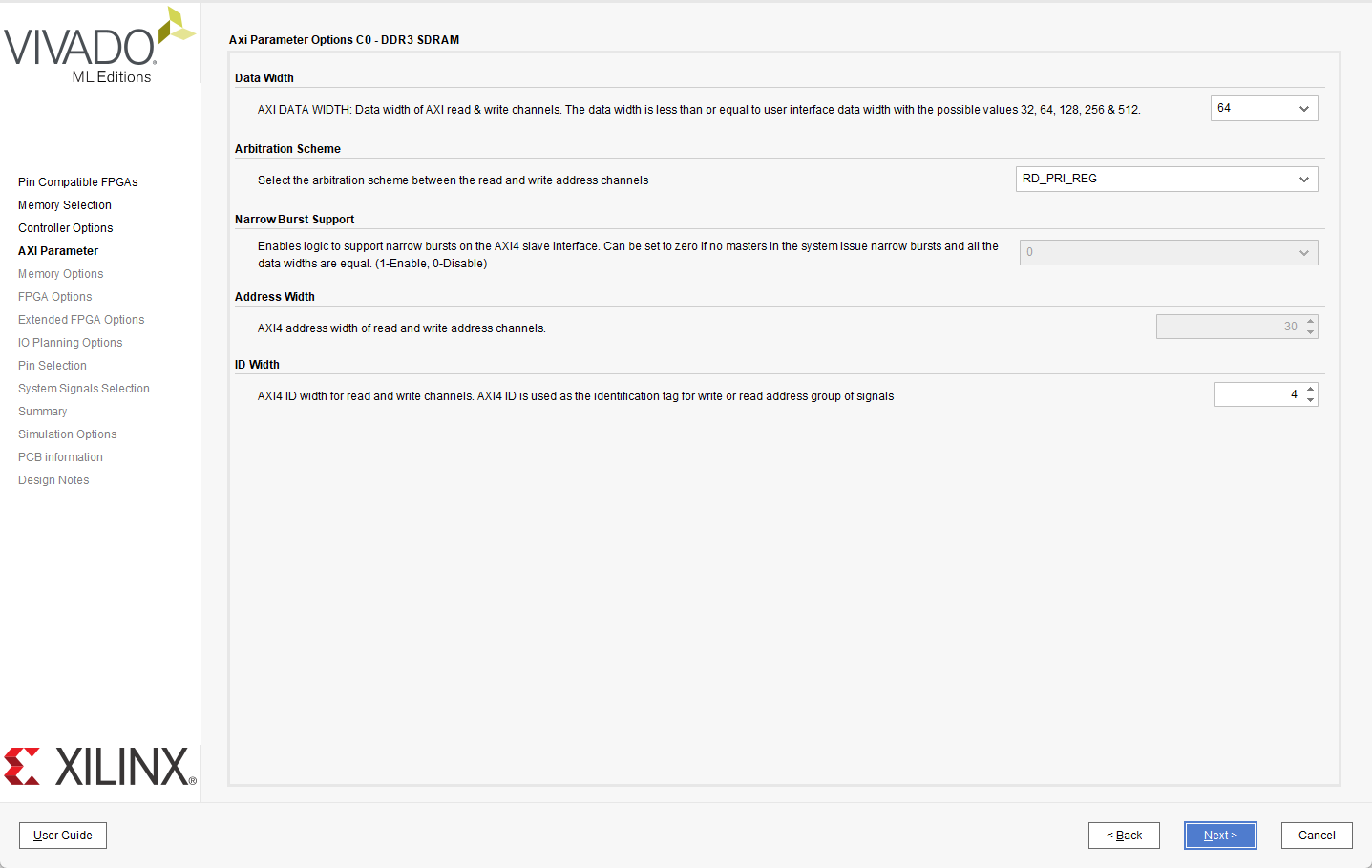

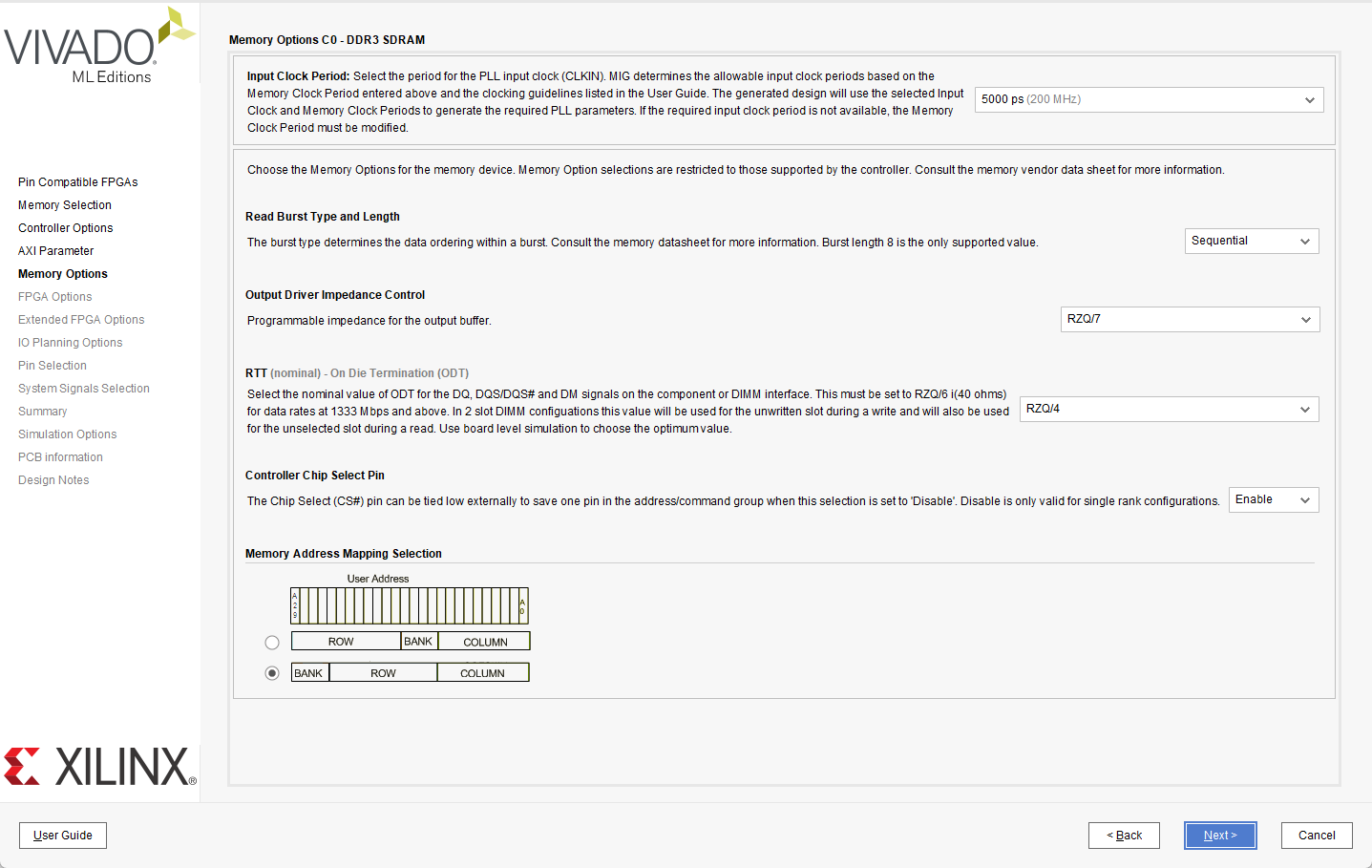

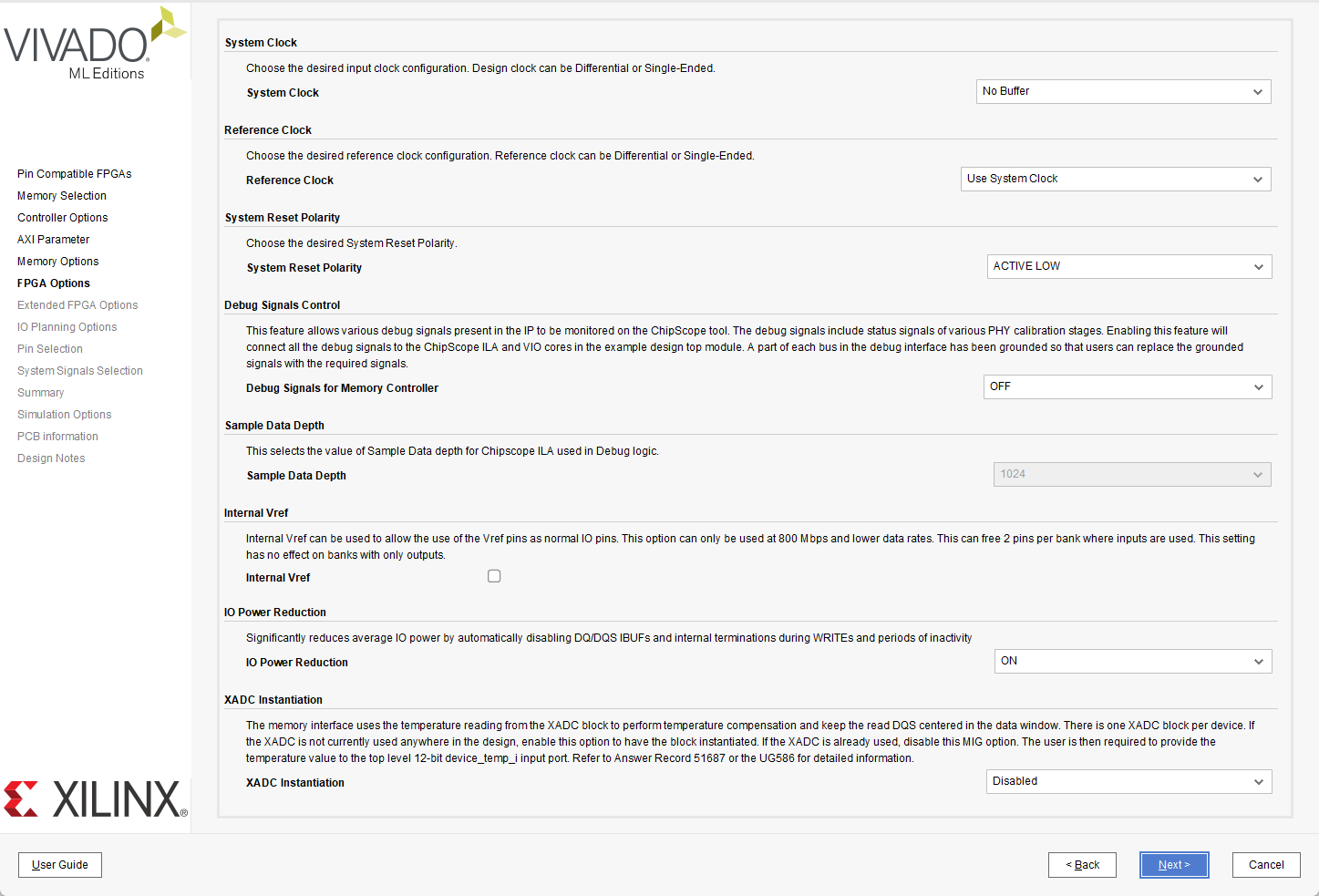

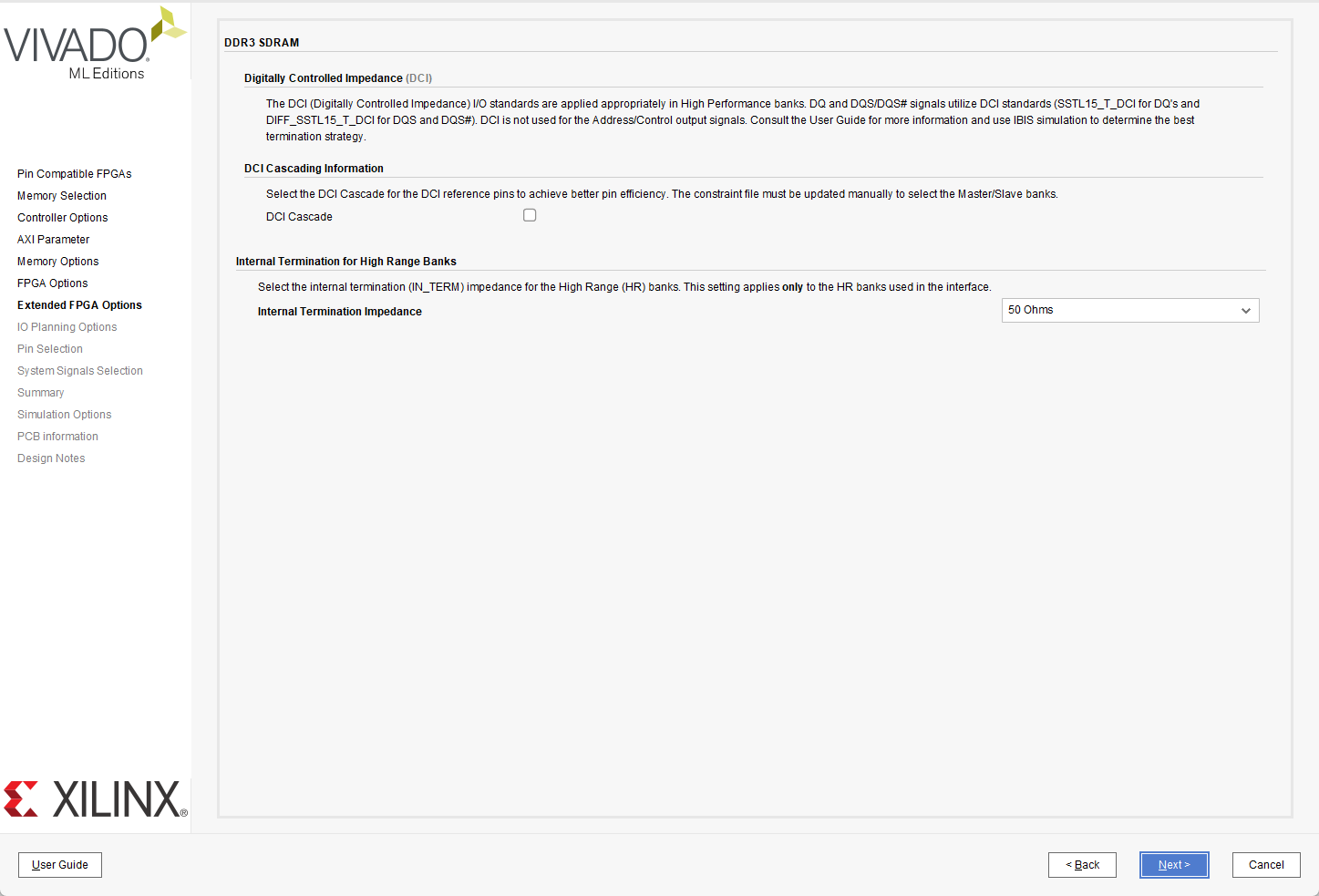

MIG核配置

关于IP核个参数的介绍可以参考野火教程,以下为目前使用的通用配置。

一些参数的设置

DDR物理接口的位宽为32bit

DDR用户接口的位宽为64bit

MIG核的XADC是关闭的,需要外部模块例化XADC模块读取FPGA的内部温度,并将温度传递给IP核。

突发长度为8,突发宽度为64bit,也就是说突发一次,地址就要增加8*8=64,因为地址是按照字节计算的,64bit是8个字节,每次突发长度是8,所以每次突发是64字节。

若要使用DDR进行数据缓存,那么数据量必须要是64字节的倍数。

DDR的读写地址是按照字节计算的,如果数据宽度为16bit,则地址需要乘以2.

用户读写接口模块设计

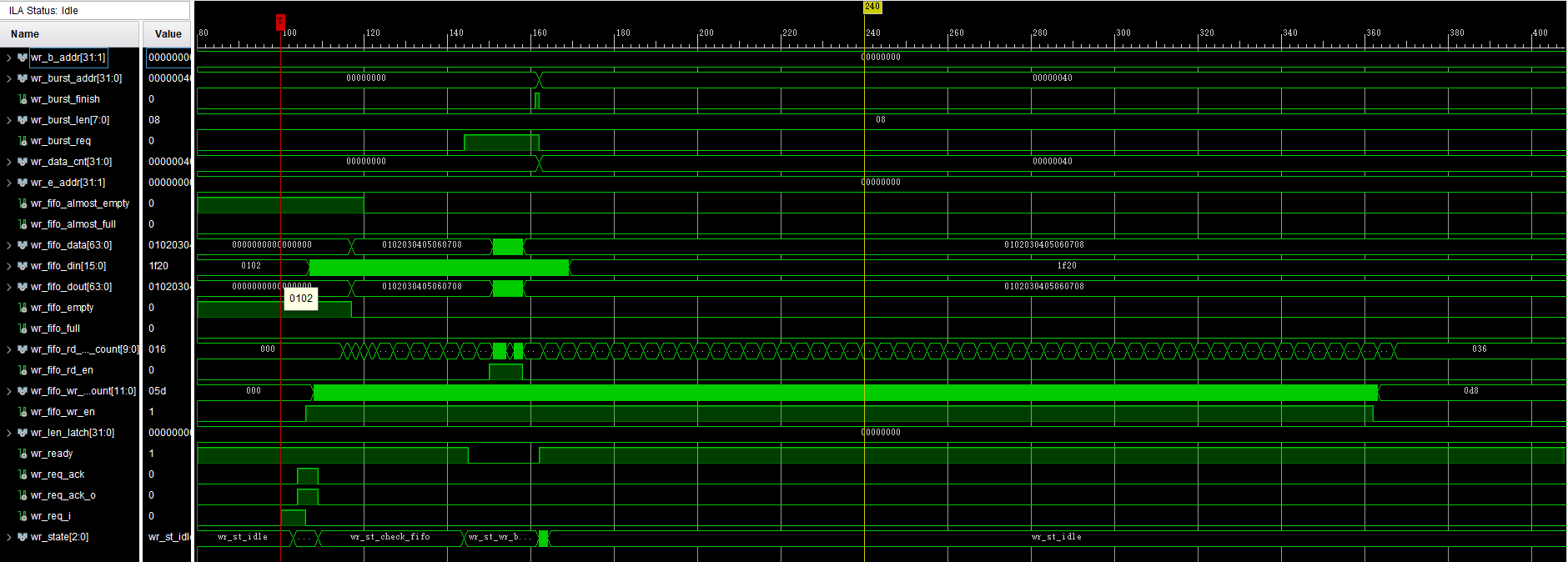

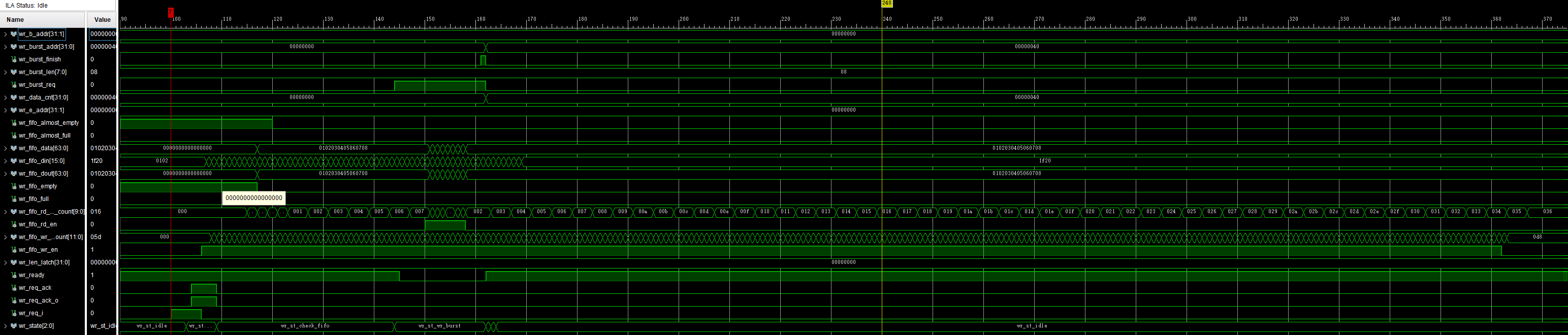

写模块设计

写接口时序

| 序号 | 信号名 | 位宽 | 方向 | 说明 |

| 1 | wr_req_i | 1 | input | 写请求信号:在写DDR前需要先发送写请求信号,用于启动写状态机,在收到响应信号后清零此信号 |

| 2 | wr_req_ack_o | 1 | output | 写请求响应信号:在收到写请求信号后,状态机跳转到响应状态,发送响应信号,并检测写请求信号是否清零,若清零则清零此信号 |

| 3 | wr_b_addr | 32 | input | 写DDR开始地址 |

| 4 | wr_e_addr | 32 | input | 写DDR结束地址 |

| 5 | user_wr_clk | 1 | input | 写FIFO时钟:与DDR的ui_clk相同 |

| 6 | data_wren | 1 | input | 写FIFO写请求 |

| 7 | data_wr | 16 | input | 写FIFO写数据 |

写接口状态机

| 序号 | 状态名 | 说明 |

| 1 | wr_st_idle | 初始状态:等待写请求信号,收到后跳转 |

| 2 | wr_st_ack | 写响应状态:收到写请求后产生写响应信号,并将写地址进行锁存;等写请求信号清零后,跳转 |

| 3 | wr_st_check_fifo | 写FIFO检查状态:若此状态中再次收到写请求信号,则跳转到写响应状态;若FIFO中的可读数据(数量+2)大于等于一次写突发的长度,并且AXI接口写空闲,则产生写突发请求信号,并跳转 |

| 4 | wr_st_wr_burst | 写突发状态:当写突发完成后,清零写突发请求,写地址增加64字节,写数据计数器增加64,跳转 |

| 5 | wr_st_wr_burst_end | 写突发结束状态:若写数据计数器小于写长度,跳转到写FIFO检查状态,否则跳转到结束状态 |

| 6 | wr_st_end | 写结束状态 |

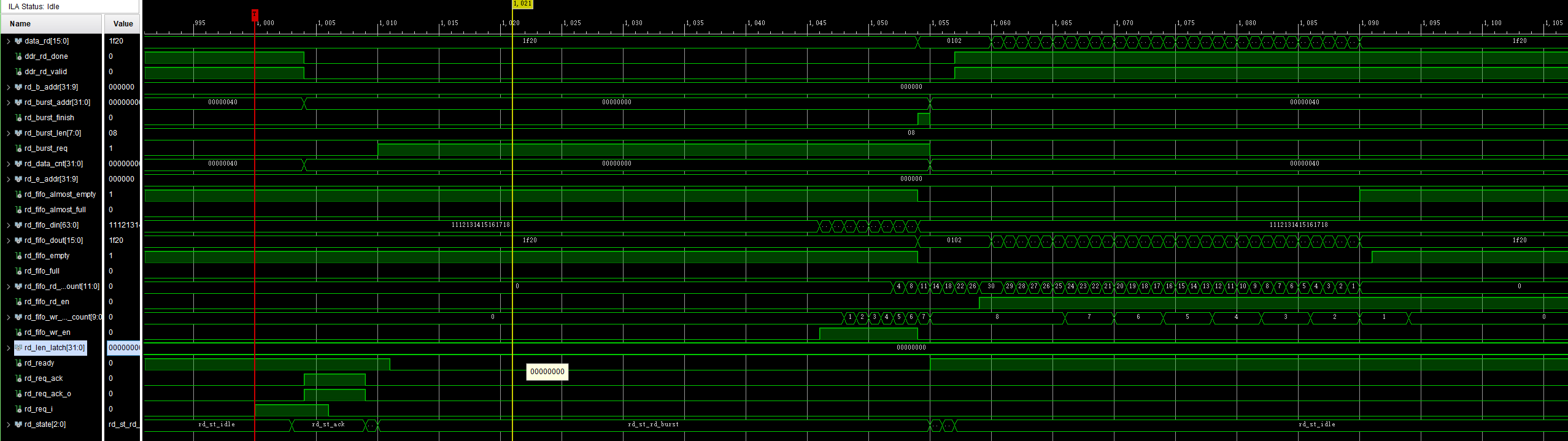

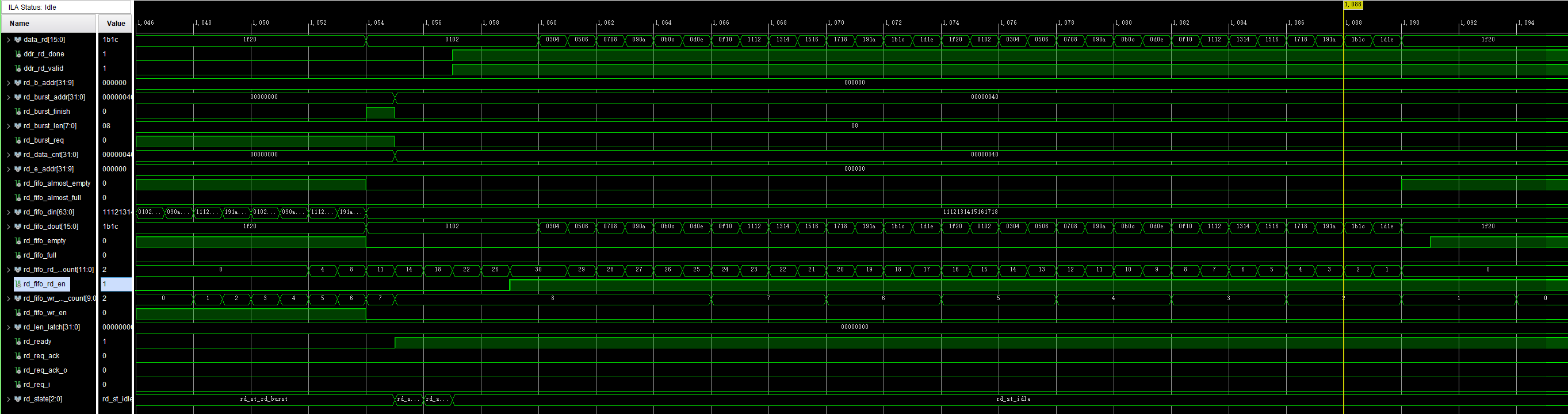

读模块设计

读模块时序

| 序号 | 信号名 | 位宽 | 方向 | 说明 |

| 1 | rd_req_i | 1 | input | 读请求信号:在读DDR前需要先发送读请求信号,用于启动读状态机,在收到响应信号后清零此信号 |

| 2 | rd_req_ack_o | 1 | output | 读请求响应信号:在收到读请求信号后,状态机跳转到响应状态,发送响应信号,并检测读请求信号是否清零,若清零则清零此信号 |

| 3 | rd_b_addr | 32 | input | 读DDR开始地址 |

| 4 | rd_e_addr | 32 | input | 读DDR结束地址 |

| 5 | user_rd_clk | 1 | input | 读FIFO时钟:与DDR的ui_clk相同 |

| 6 | data_rden | 1 | input | 读FIFO写请求 |

| 7 | data_rd | 16 | output | 读FIFO写数据 |

| 8 | ddr_rd_valid | 1 | input | DDR读有效标志:表示将DDR中的数据成功读出,缓存在FIFO中 |

读接口状态机

| 序号 | 状态名 | 说明 |

| 1 | rd_st_idle | 初始状态:等待读请求信号,收到后跳转 |

| 2 | rd_st_ack | 读响应状态:收到读请求后产生读响应信号,并将读地址进行锁存;等读请求信号清零后,跳转 |

| 3 | rd_st_check_fifo | 读FIFO检查状态:若此状态中再次收到读请求信号,则跳转到读响应状态;若FIFO中的可写数据小于等于(10'd1000-DDR_RD_LEN),并且AXI接口读空闲,则产生读突发请求信号,并跳转 |

| 4 | rd_st_rd_burst | 读突发状态:当读突发完成后,清零读突发请求,读地址增加64字节,读数据计数器增加64,跳转 |

| 5 | rd_st_rd_burst_end | 读突发结束状态:若读数据计数器小于读长度,跳转到读FIFO检查状态,否则跳转到结束状态 |

| 6 | rd_st_end | 读结束状态 |

1395

1395

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?