本节目录

一、内存简介

(1)内存基本存储原理

(2)内存频率

(3)DDR数据预取技术(Prefetch)

(4)DDR3工作流程

(5)DDR3控制器的特点

二、内存基本参数

(1)物理Bank

(2)逻辑Bank

(3)内存芯片容量

(4)行激活命令—tRCD

(5)列选通—CL

(6)写入延迟—tDQSS

(7)行预充电有效周期—tRP

(8)数据掩码—DQM

(9)数据选取脉冲—DQS

(10)突发长度—burst length

(11)刷新—Refresh

(12)模式寄存器—MR0、MR1、MR2、MR3

本节内容

一、内存简介

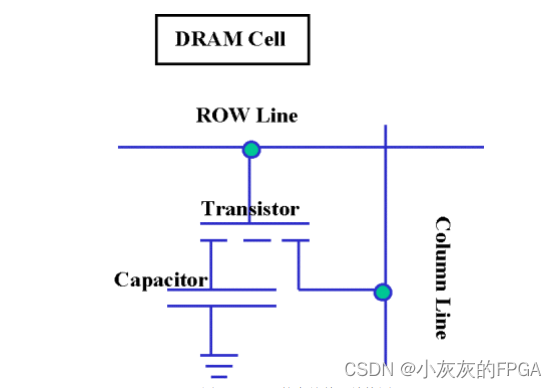

(1)内存基本存储原理

内存(Memory),即动态随机存储(Dynamic Random Access Memory,DRAM),利用电容存储电荷的多少来代表0和1,内存的最小单元-bit,每个bit只需要一个晶体管和电容。

行选与列选信号将使存储电容与外借间的传输电路导通,从而可进行放电(读取)与充电。

DRAM预充电——电容存在漏电,必须被周期性的刷新。

(2)内存频率

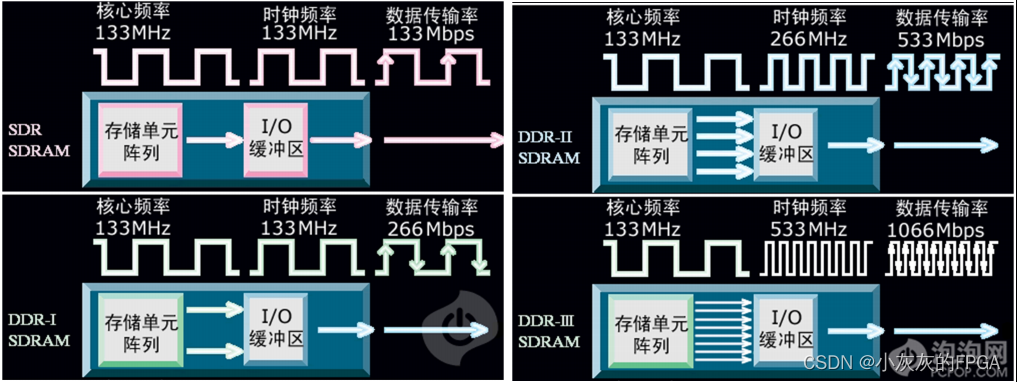

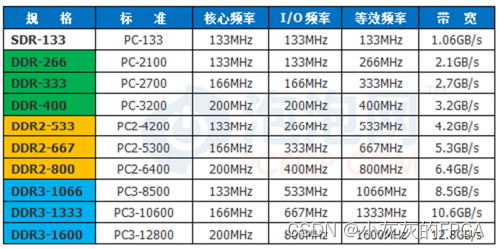

内存三种频率指标——核心频率、时钟频率、有效数据传输频率

核心频率——内存Cell阵列(Memory Cell Array,内存电容)的刷新频率,内存的真实运行频率;

时钟频率——I/O buffer(输入/输出缓冲)的传输频率;

有效数据传输频率——数据传送频率(等效频率),测试时关注的时钟频率。

内存的频率(等效频率)成倍增长,但核心频率一直在133M——200M之间(电容的刷新频率取决于制造工艺)。

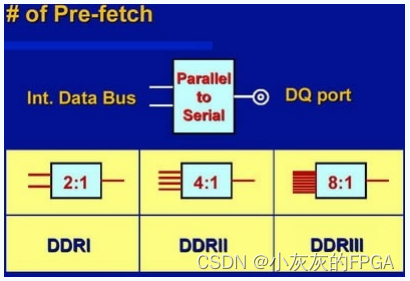

(3)DDR数据预取技术(Prefetch)

DDRI、DDRII、DDRIII内存关键技术是分别采用2/4/8bit数据预取技术,将带宽翻倍。

预取,预先/提前存取数据,I/O控制器发出请求之前,存储单元已经事先准备好2/4/8bit数据,可以理解为并行传输的数据转换为串行数据流。

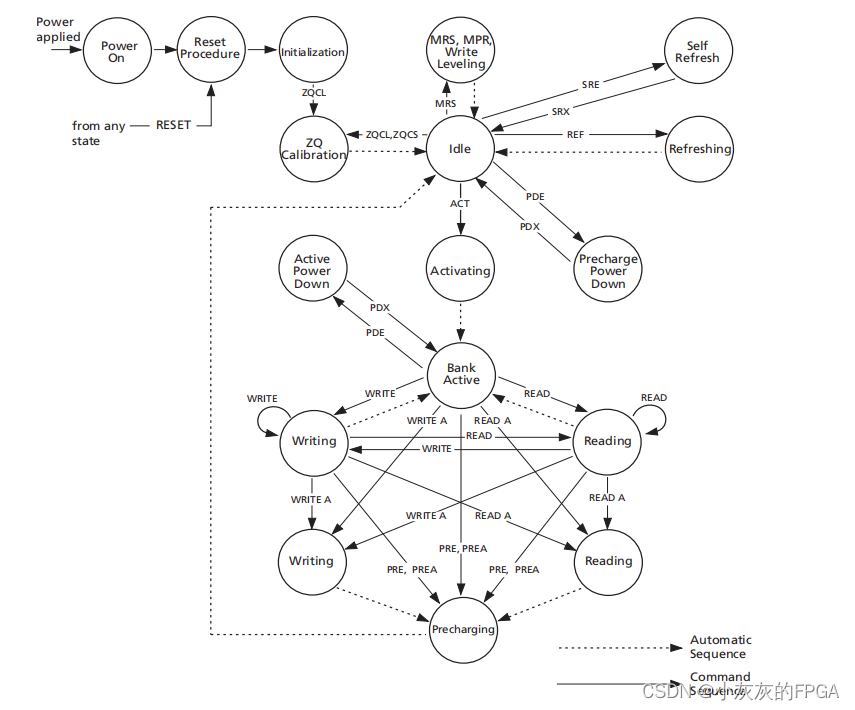

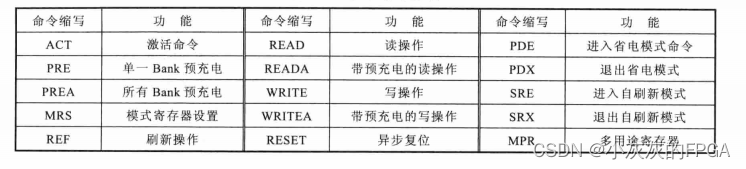

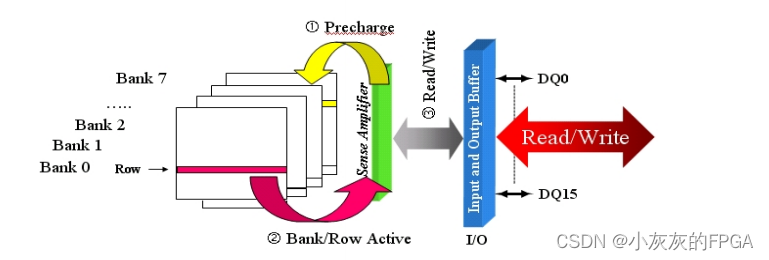

(4)DDR3工作流程

DDR3的相关操作主要包括上电(Power On)、复位(Reset procedrue)、初始化(Initialization)、ZQ对齐(ZQ calibration)、模式寄存器配置(MRS)、自刷新(SR)、刷新(Refreshing)、激活(Activing)、读(Reading)、写(Writing)、预充电(Precharging)及低功耗模式的操作等。

(5)DDR3控制器的特点

①逻辑划分采用了8Bank和16Bank的设计,增加了存储器容量。

②增加ZQ校准功能,ZQ采用一个命令集,通过片上校准引擎(On Die Calibratino Engine,ODCE)来自动校验数据输出驱动器导通电阻与ODT的终结电阻值。

③复位功能,RESET命令可以将DDR3存储器停止所有操作,切换至低功耗模式。

④采用点对点连接,控制器与存储器之间是一对一,并采用了“fly-by”布线结构,提高信号的完整性,同时引入读写均衡技术来解决布线结构带来的时间偏差问题。

⑤DDR3的预取位宽变成8bit,突变BL为8。

⑥DDR3将工作参考电压分成两个,一是与命令和地址信号相关的VREFCA;两一个是与数据总线相关的VREFDQ。

二、内存基本参数

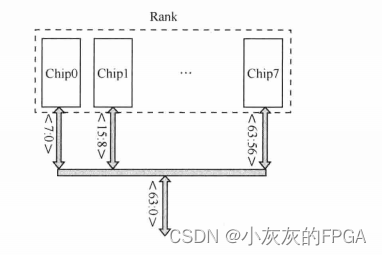

(1)物理Bank

为了保证CPU的正常工作,在一次传输周期内,内存系统必须完成传输所需要的数据,数据以bit为单位。

物理Bank(Physical Bank),指的是CPU数据总线的位宽,CPU在一个传输周期能接受的数据容量。

以8颗位宽为8bit的内存颗粒并行组成64bit的Bank

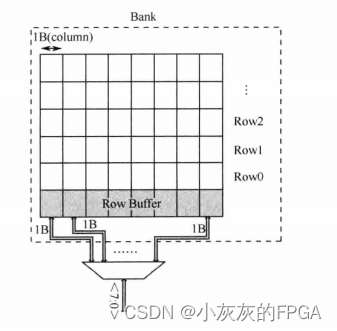

(2)逻辑Bank

DDR SDRAM的内部是一个存储阵列,将数据填写进去,类似一个带有行列寻址能力的二维平面的存储表格。类似于表格的检索过程,先指定一个行(Row),再指定一个列(Column),可以准确确定所需要的单元格,即内存寻址的基本原理。所谓的单元格就是逻辑Bank(Logic Bank)。

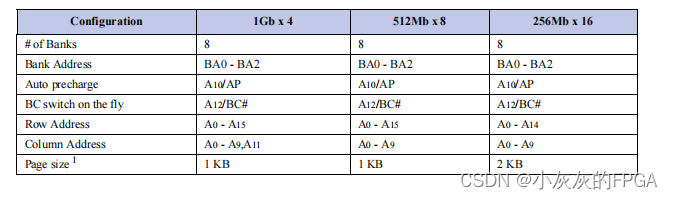

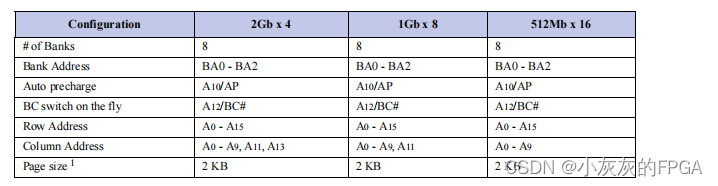

(3)内存芯片容量

内存芯片的容量,其实就是所有逻辑Bank中存储单元的容量综合,有一套计算公式,具体如下:

存储单元数量=行数×列数(一个Bank的存储单元数量)×Bank的数量

常用的一些单位换算,bit,byte,word

bit—表示位,二进制中一个0或者1表示1bit;

byte—表示字节,8个bit为一个字节,DB可以表示双字节;

word—表示字,两个字节为一个字,DW可以表示双字,即四个字节。

以MT41K256M16XX-107内存型号来计算内存容量为256Mb*16=4Gb

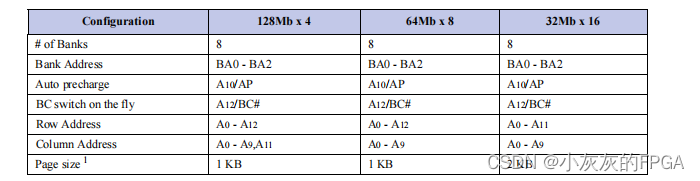

DDR3内存容量512Mb

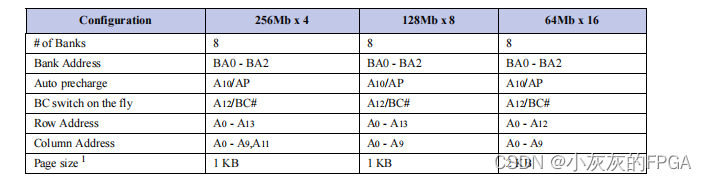

DDR3内存容量1Gb

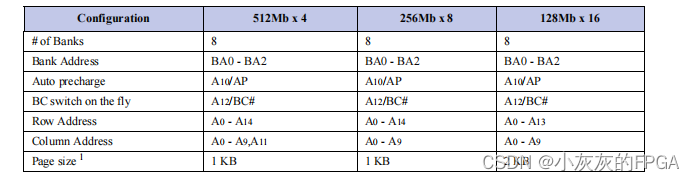

DDR3内存容量2Gb

DDR3内存容量4Gb

DDR3内存容量8Gb

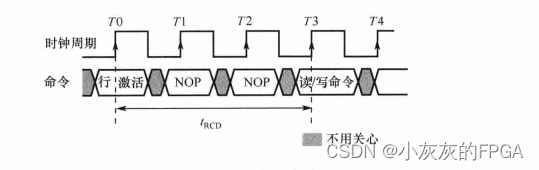

(4)行激活命令—tRCD

在对逻辑Bank内数据进行读写访问前,首先必须将Bank中的数据所在的行激活,或者行有效,即“Row Active”,一旦激活,保持激活状态直到发送预充电命令。

发送行激活命令时,Bank地址与相应的行地址同时发出,随后发送列地址寻址命令与具体的读或写操作命令,当然,因为这两个命令时同时发出,故以“读或写命令”来表示列寻址。

在内存的标准中,tRCD表示从行有效到读或写命令发出之间的时间间隔,即RAS to CAS Delay,行地址选通脉冲RAS到列地址选通脉冲CAS的延迟时间。

tRCD以DDR的时钟周期tck为单位,以tRCD=3为例,代表延迟周期为3个时钟周期tck,tck以内存时钟频率确定。

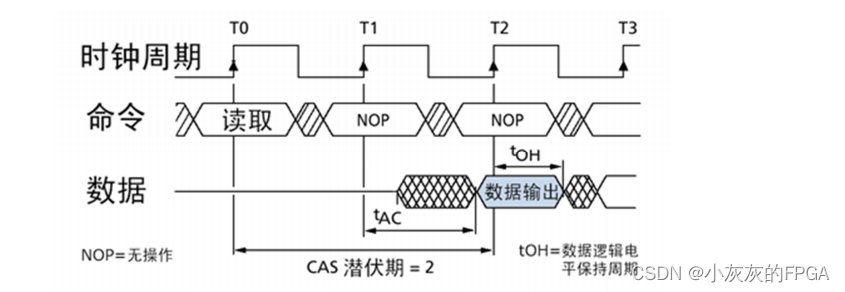

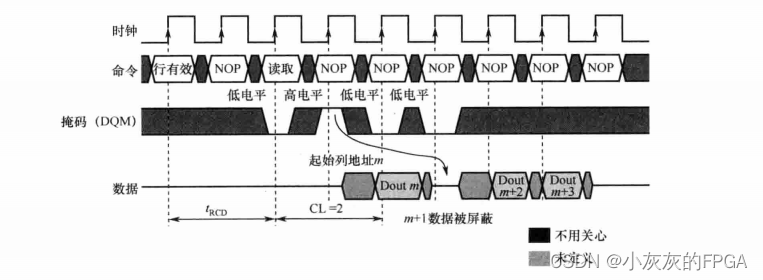

(5)列选通—CL

在读命令时,发送列地址后,将会触发数据的传输,但是从存储单元到芯片的I/O总线之间还存在一定的时间间隔CL(CAS Latency,列选通脉冲潜伏期)。CL以DDR的时钟周期tck为单位,CL=2,代表延迟周期为2个时钟周期tck。

在读取操作,数据经过触发,需要一定的驱动时间才能传送到I/O总线并输出,这段时间称为tAC(Access Time from CLK,时钟触发后的访问时间),tAC必须小于一个时钟周期,才能保证不会因为访问时间过程导致效率低。

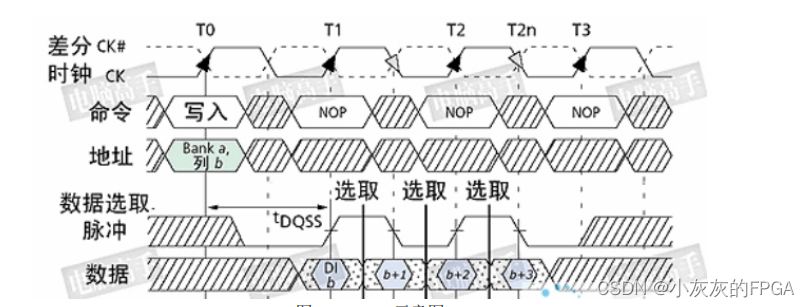

(6)写入延迟—tDQSS

tDQSS(Write Command to the first corresponding rising edge of DQS),在发出写入命令后,DQS与写入数据要等待一段时间才会在下个时钟沿送达。

(7)行预充电有效周期—tRP

数据读取完成之后,需要释放读出放大器,供同一Bank内其他行寻址操作和数据传输,将进行行预充电的操作来关闭当前的工作行。

预充电对行中所有存储单元进行数据重新加载,并对行地址进行复位。预充电命令之后,需要经过一段时间才允许发送行激活命令操作新的工作行,这个时间间隔称为tRP(RAS Perchange Time)。

以一个案例来说明下:

当前寻址的存储单元为B1、R2、C6。

若下一次的寻址命令为B1、R2、C3,则不需要预充电,读出放大器正在R2工作行服务。

若下一次的寻址命令为B1、R3、C3,则需要预充电,需要操作同一Bank的其他行,先把R2关闭,才能对R3进行寻址。从R2关闭到打开R3的间隔就是tRP。

如果是不同Bank之间的读操作,也需要关闭当前行,再激活新的Bank和ROW。

(8)数据掩码—DQM

数据掩码DQM(Data I/O Mask),用于屏蔽不需要的数据。

通过采用数据掩码,控制器能够以字节为操作单位指示I/O端口数据的有限性。当然,被掩码掩掉的数据仍然会从存储器中读出,在掩码功能模块中被屏蔽。

(9)数据选取脉冲—DQS

DQS功能是用来在一个时钟周期内准确的区分出每个传输周期,方便接收方准确接收数据。

DQS数据线是双向的,在写入时,用来传输由内存控制器发送的DQS信号;读取时,由芯片生成DQS向控制器发送。

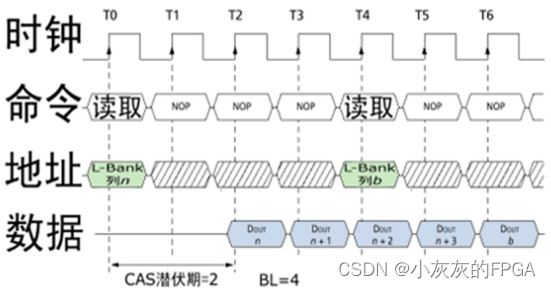

(10)突发长度—burst length

突发Burst是指在同一行中相邻的存储单元连续进行数据访问。

突发长度(BL,Burst Length)是指连续访问的时钟周期数。

在进行突发传输时,只需要制定起始列地址与突发长度,内存就会依次自动对后面相应数量的存储单元进行读或写操作,不需要控制器连续第提供列地址。

(11)刷新—Refresh

内存需要不断地进行刷新操作,才能在存储单元中维持数据的有效存储。刷新操作,有固定的操作周期,依次对所有行进行操作,以维护存储单元中的所有数据,其中行指的是所有Bank中地址相同的行。

刷新操作分为两种:自动刷新(Auto Refresh,AR)和自刷新(Self Refresh,SR)。

自动刷新AR,内部由一个行地址生成器用来自动的依次生成行地址,在刷新过程中,所有Bank都停止工作,每次刷新结束后,可进入正常工作状态。

自刷新SR主要用于休眠模式低功耗状态下的数据保存。在SR模式下,根据内部的时钟进行refresh,并且只有CKE信号可以使用,其余信号均无效,只有重新使CKE有效才能退出自刷新模式。

DDR3采用了一种自动自刷新模式SAR,开启SAR模式,通过内置于内存芯片的温度传感器来控制刷新的频率。

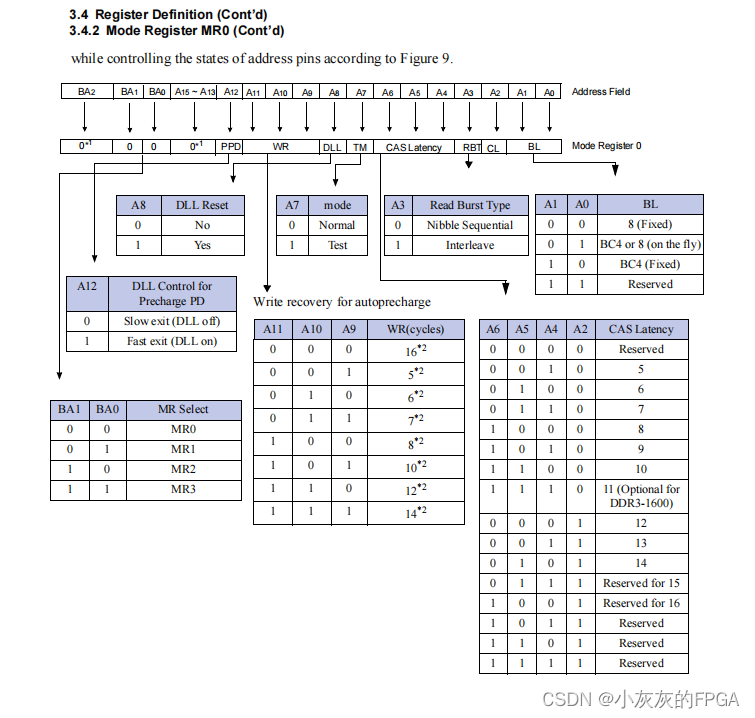

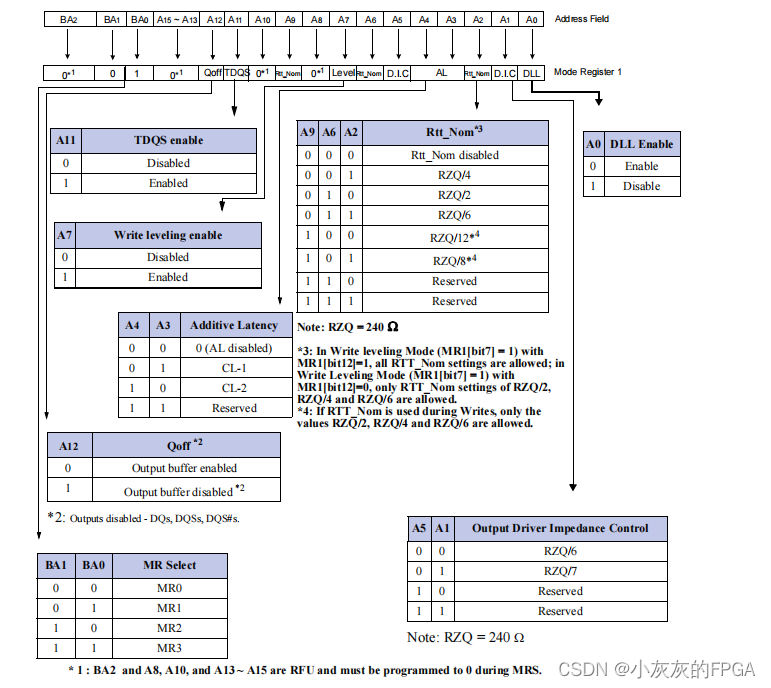

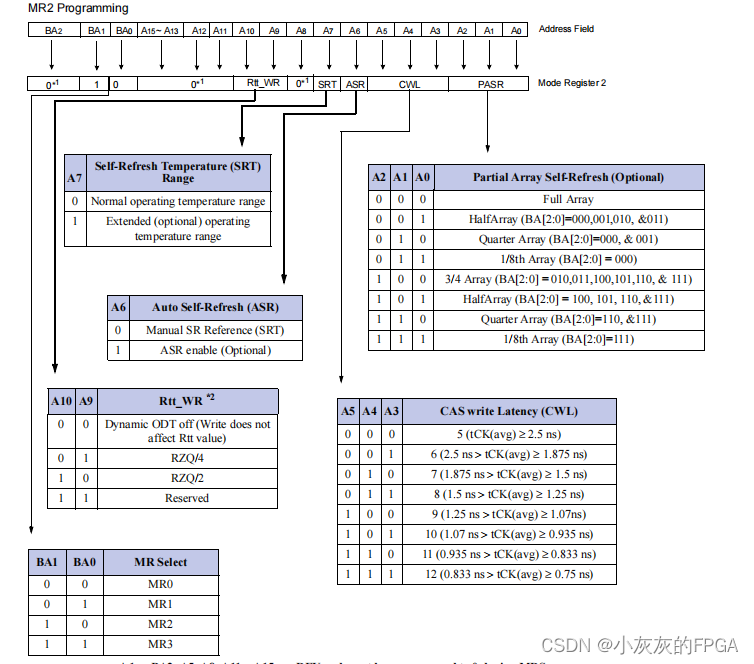

(12)模式寄存器—MR0、MR1、MR2、MR3

模式寄存器用于设置内存的工作模式。在初始化阶段,设置命令对模式寄存器进行变成,也支持在内存正常工作期间对模式寄存器进行内容修改。

模式寄存器MR0,存储用于控制DDR3 SDRAM的各种工作模式的数据。它控制突发长度、读取突发类型、CAS延迟、测试模式、DLL复位、WR和DLL控制。

模式寄存器MR1存储用于启用或禁用DLL、输出驱动器强度、Rtt_Nom阻抗、附加延迟、启用写入均衡使能、TDQS启用和Qoff的数据。

模式寄存器MR2存储用于控制刷新相关特性、Rtt_WR阻抗和CAS写入延迟的数据。

本文深入探讨了DDR3内存的工作原理,包括内存的基本存储、频率、预取技术,详细阐述了DDR3的工作流程,如上电、复位、初始化等,并解析了关键参数如物理Bank、逻辑Bank、tRCD、CL等,以及内存的刷新机制和模式寄存器配置。

本文深入探讨了DDR3内存的工作原理,包括内存的基本存储、频率、预取技术,详细阐述了DDR3的工作流程,如上电、复位、初始化等,并解析了关键参数如物理Bank、逻辑Bank、tRCD、CL等,以及内存的刷新机制和模式寄存器配置。

2671

2671

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?