On Die Termination Calibration

随着对于数字系统性能要求的不断提高,对信号完整性的要求也越来越高,从而能够在更高的速率下可靠运行。信号线端接是信号完整性管理中的有用元件,可以在memory外部或memory内部使用。在DRAM器件中加入电阻端接(通常称为片上端接(ODT,On Die Termination))可通过减少片外端接引入的电气不连续性来改善信号传输环境。然而,工艺、电压和温度 (PVT) 的变化会导致 ODT 元件的电阻特性不稳定。

ODT 校准可确定最佳端接阻抗,以减少信号反射并补偿 PVT 的变化。

校准 ODT 端接阻抗

减少信号反射

补偿 PVT 和工作条件的变化

什么是片上端接校准技术?

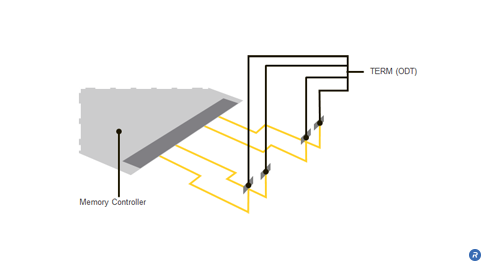

传统的DRAM memory module架构通常包括主板上的线路终端电阻器。尽管主板上的终端电阻减少了信号线上的一些反射,但它们无法防止连接到DIMM上 DRAM 的连接线产生的反射。从内存控制器传播到 DRAM 的信号在通向DIMM上 DRAM 的连接线处遇到阻抗不连续性。沿DIMM上 DRAM 的连接线处传播到DRAM的信号将被反射回信号线,从而将不需要的噪声引入信号中。

随着数据速率的提高和DIMM上连接线长度的延长,这种片外(off-die)端接无法解决的引入噪声和随之而来的信号劣化变得更加明显。包含多个DRAM DIMM的大型系统会引入更多的反射,从而增加更多的反射噪声,从而导致信号进一步衰减。

通过将端接电阻放在芯片本身而不是主板上,可以显著减少DIMM上连接线引起的反射,从而产生更清晰的信号并实现更快的数据速率。

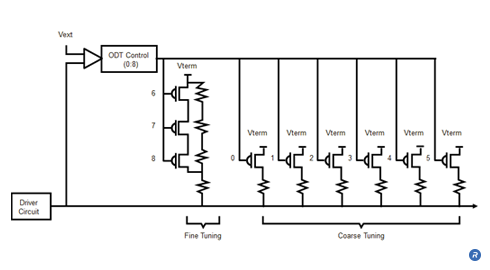

ODT 校准是一种涉及校准端接阻抗以优化信号反射减少的技术。ODT校准允许建立最佳端接值,以补偿过程和操作条件的变化。

校准的 ODT 值可显著减少不需要的信号反射,同时仅因增加的电阻负载而将信号摆幅的幅度降至最低。由此产生的更清晰的数据信号允许更高的数据速率。

ODT 校准是通过建立与外部精密电阻成正比的 ODT 阻抗来实现的。

ODT 校准控制器将 ODT 电阻网络上的压降与所表示的外部电阻器上的压降进行比较。控制器通过粗调和微调对电阻网络进行修改,以实现与外部基准电阻非常接近的阻抗值。

谁受益?

ODT 校准在器件、子系统和系统层面都具有优势。通过实施ODT校准,器件能够实现增强的信号性能和更高的数据速率,从而使设计人员能够实现卓越的DRAM器件和DIMM性能。

此外,将端接元件放置在DRAM器件上会从PCB中移除这些元件。这样一来,主板上的组件和信号线的数量就会减少,从而降低成本和复杂性,同时提高可靠性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?