前几天调了1块F103ZET6的开发板,用了个系统定时器,感觉不准,最终找到原因是因为选错了时钟源。

今天来分享一下也算是给大家以后出现问题做个参考吧。

说到时钟源,得说到STM32系统时钟的初始化。

24784631ef81c09c1b.png (44.07 KB )

2022-9-12 17:12 上传

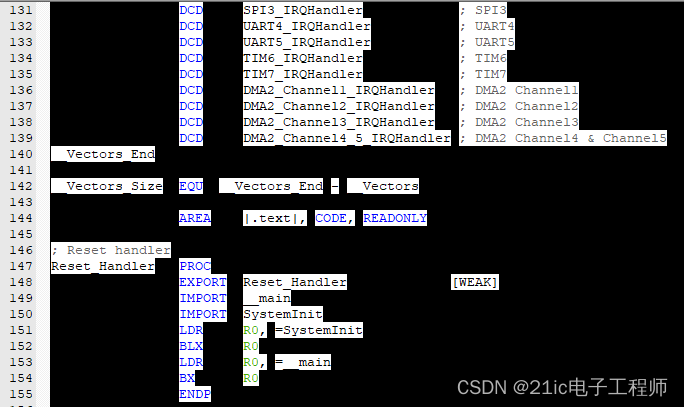

前面就不说了,直接从复位中断说起。 复位所有的中断之后,导入Main函数

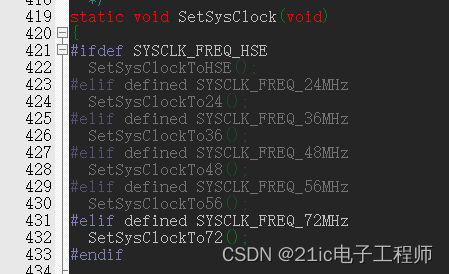

然后,进入SystemInit函数,进行时钟配置。在SystemInit函数中有一个 SetSysClock()函数

配置系统时钟为72M,这是在外部晶振为8M的情况下。

配置完系统时钟之后,然后运行Main函数,这就是STM32程序的启动过程。

系统定时器是是Core_cm3和Core_cm4内核均存在的定时器

F103c8t6,共有7个定时器,一个高级定时器TIM1,3个通用定时器TIm2、TIM3和TIM4、1个系统定

时器和2个看门狗定时器(独立的和窗口型)。

系统定时器(滴答定时器)是一个24位自减型计数器,也就是说他的最大计数次数为

111111111111111111111111,换算成十六进制为0XFFFFFF,十进制为16777215。

系统定时器的时钟来源可以通过 SysTick_CLKSourceConfig()来选择。

如果选择 SysTick_CLKSourceConfig(SysTick_CLKSource_HCLK)则为0,选择内部时钟72M。

若选择SysTick_CLKSourceConfig(SysTick_CLKSource_HCLK_Div8),则系统时钟72M的8分频,

网上很多说把SysTick_CLKSource_HCLK_Div8叫做外部分始时钟,不知道是啥原因?

系统定时器时钟频率为9M

1 = 外部时钟源(STCLK) (AHB总线时钟的1/8(HCLK/8)

0 = 内核时钟(FCLK) (AHB总线时钟的频率(HCLK))

也就是这里我用错了时钟源导致系统定时器不准!!

这是原因1,还有一个原因在下面解释。

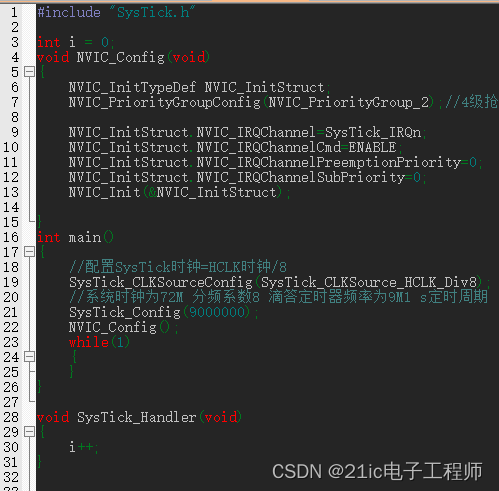

要是用滴答定时器中断,要配置滴答定时器的中断优先级,否则为默认的最低优先级。

滴答定时器发生中断后,不需要人为去清除中断标志位和重新加载预装值,系统会自动清除和装载,比较简单

滴答定时器配置

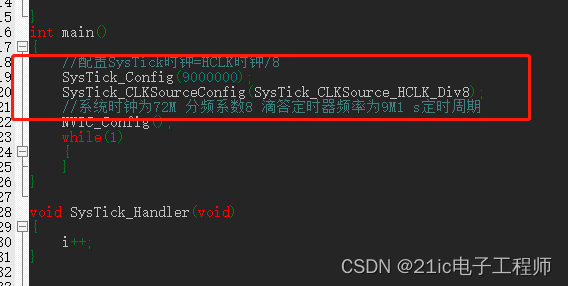

我们采用系统时钟的八分频,也就是系统时钟为9M,每秒钟计数为9M

设置计数值为9M,也就是说1秒钟进一次系统定时器中断函数,用变量i自加来表示。

但是这样的配置我们发现i的自加并没有按照1s加一次的理论进行,而且加的很快。

但后来把计数值放在系统分频的前面,也就是如下图所示,计数正常。

这个原因没找到,但是结果正确,哪位大佬帮忙解释一下,代码已上传。

还有个提示,就是用了滴答定时器做定时器中断之后,就不要再用于延时函数了

否则就冲突程序跑飞了,比如这样![]()

还需要知道一点的是:

时钟配置为72MHz,第一行代码已经选择为滴答定时器系统时钟的8分频,也就是滴答定时器时钟为9MHz,

下面的“fac_us”需要得到的是时钟周期,即1us(1个fac_us)需要9个时钟周期,1个fac_ms需要9000个时钟周期。

以上就是对系统定时器计数不准的解释。

---------------------

作者:woai32lala

链接:https://bbs.21ic.com/icview-3252426-1-1.html

来源:21ic.com

此文章已获得原创/原创奖标签,著作权归21ic所有,任何人未经允许禁止转载。

1240

1240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?