1.FIFO与RAM的差异:

FIFO : 先入先出,先进去的数据先出来

RAM : 读出的数据顺序跟写入数据顺序不一致,可以向RAM中的任意位置写入数据,也可以读取任意的位置的数据。

信号的差异:

以下以1R1W的RAM和异步FIFO作为案例

FIFO没有写地址和读地址,只能按顺序读写数据,而RAM具有读写地址,因此可以读写任意地址

FIFO | RAM | ||

wclk | 写时钟 | wclk | 写时钟 |

wen | 写使能 | wen | 写使能 |

wdata | 写数据 | wdata | 写数据 |

rclk | 读时钟 | waddr | 写地址 |

ren | 读使能 | rclk | 读时钟 |

rdata | 读数据 | ren | 读使能 |

|

| rdata | 读数据 |

|

| raddr | 读地址 |

2.FIFO与RAM的共同点

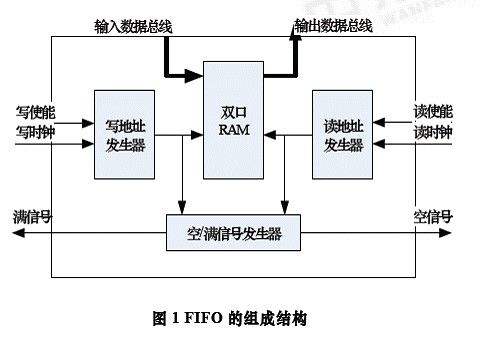

规模较大的FIFO一般都是用RAM实现的(规模特别小的FIFO才会使用寄存器实现)。如图所示,双端口RAM作为存储模块,加上外部逻辑结构组成了一个异步FIFO。

3.应用场景

FIFO常用于数据传输通道中,用于缓存数据,避免数据丢失:如不同速率时钟模块间的数据传输就需要用到异步FIFO。

RAM常用于存储指令或者中间的数据,如指令cache和数据cache就是由RAM实现的。

本文详细介绍了FIFO和RAM的基本概念、主要差异及共同点,并探讨了它们各自的应用场景。FIFO遵循先入先出原则,适用于数据传输通道中的缓存;RAM则允许随机读写,广泛应用于指令或数据的存储。

本文详细介绍了FIFO和RAM的基本概念、主要差异及共同点,并探讨了它们各自的应用场景。FIFO遵循先入先出原则,适用于数据传输通道中的缓存;RAM则允许随机读写,广泛应用于指令或数据的存储。

479

479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?