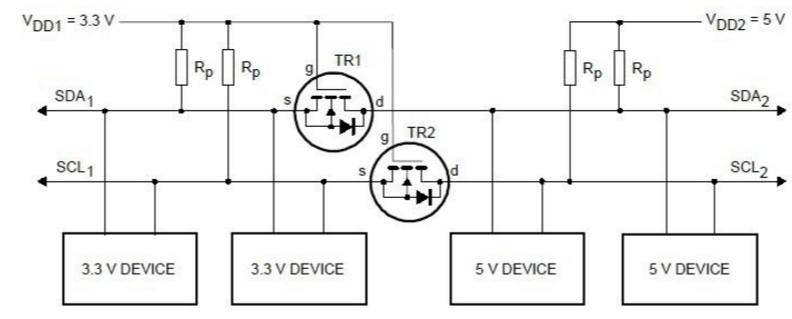

1、电路图如下:

注意:NMOS管Source端接低电平侧,Drain端接高电平侧,不然通过NMOS体二极管可能存在漏电。

上图中,SDA1/SCL1,SDA2/SCL2为I2C的两个信号端,VDD1和VDD2为这两个信号的高电平电压。电路应用限制条件为:

1,VDD1 ≤ VDD2;

2,SDA1/SCL1的低电平门限大于0.7V左右(视NMOS内的二极管压降而定),见本文案例分析章节;

3,Vgs ≤ VDD1;

4,Vds ≤ VDD2;

5,信号频率做不到很快。

对于3.3V和5V/12V等电路的相互转换,NMOS管选择AP2306或者SI2306即可。

2、电路分析如下:

2.1、没有器件下拉总线线路

3.3V部分的总线线路通过上拉电阻Rp上拉至3.3V。 NMOS管的栅极和源极都是3.3V, 所以它的Vgs 低于阀值电压,NMOS管不导通。这就允许5V部分的总线线路通过它的上拉电阻Rp上拉到5V。此时两部分的总线线路都是高电平,只是电压电平不同。

2 .2、一个3.3V 器件下拉总线线路到低电平

NMOS管的源极也变成低电平,而栅极是3.3V,Vgs上升高于阀值,NMOS 管开始导通。然后5V部分的总线线路通过导通的NMOS管被3.3V 器件下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

2.3、一个5V 的器件下拉总线线路到低电平

NMOS管的漏极基底二极管导通,源极电压为基底二极管导通0.7V,3.3V部分被下拉直到Vgs 超过阀值,NMOS管开始导通。3.3V部分的总线线路通过导通的NMOS管被5V 的器件进一步下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。

3、优点:

1、适用于低频信号电平转换,价格低廉。

2、导通后,压降比三极管小。

3、正反向双向导通,相当于机械开关。

4、电压型驱动,当然也需要一定的驱动电流,而且有的应用也许比三极管大。

4、3.3向5V转换测试:

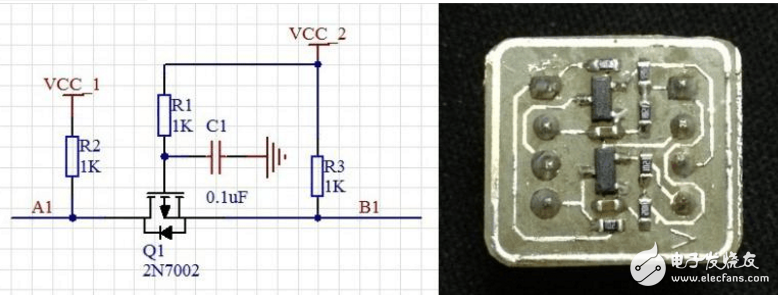

对这个电路测试了下,MOS管采用的是2N7002小信号NMOS,输入电容很小的,大概几十pF。下面是电路及实物

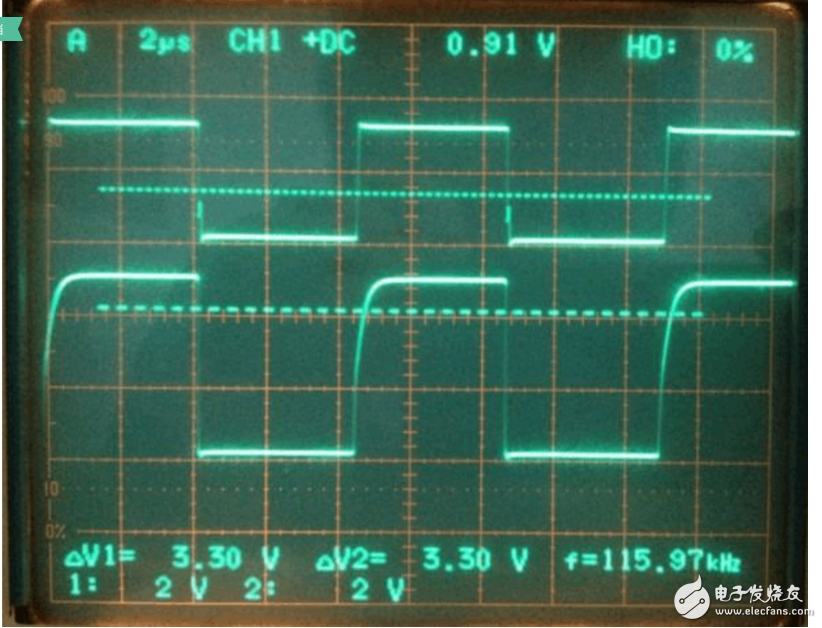

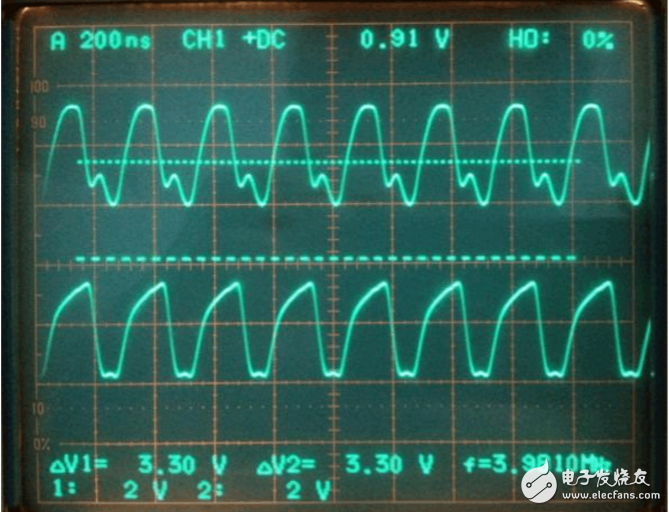

115KHz波形,这个是频率是常用串口较高的波特率

分析:5V电路上升沿缓是因为依靠上拉电阻上升至5V,时间常数决定,上拉电阻越小上升时间越小;5V电路下降沿陡是因为NMOS导通,直接由3.3V电路驱动低电平。

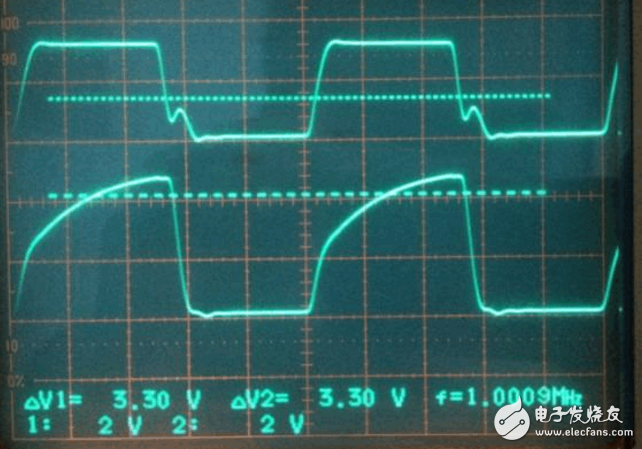

400KHz,高速IIC通信的时钟频率

1MHz,波形上升太慢了

4MHz,已经不能输出5V的电平了

分析:5V电路还没来得及上升至5V就被拉下来了。

5、案例分析

5.1、1.5V MDIO在低温下无法正确访问

5.1.1、问题描述

某颗以太网PHY芯片,MDIO电压设定为1.35V(1.5V-10%),其对接的MDIO工具为3.3V,利用NMOS进行电平转换。

由于NMOS体二极管的导通压降的存在,导致MDIO工具输出0的时候,PHY端的MDIO会有0.几伏的电压(体二极管导通压降)。

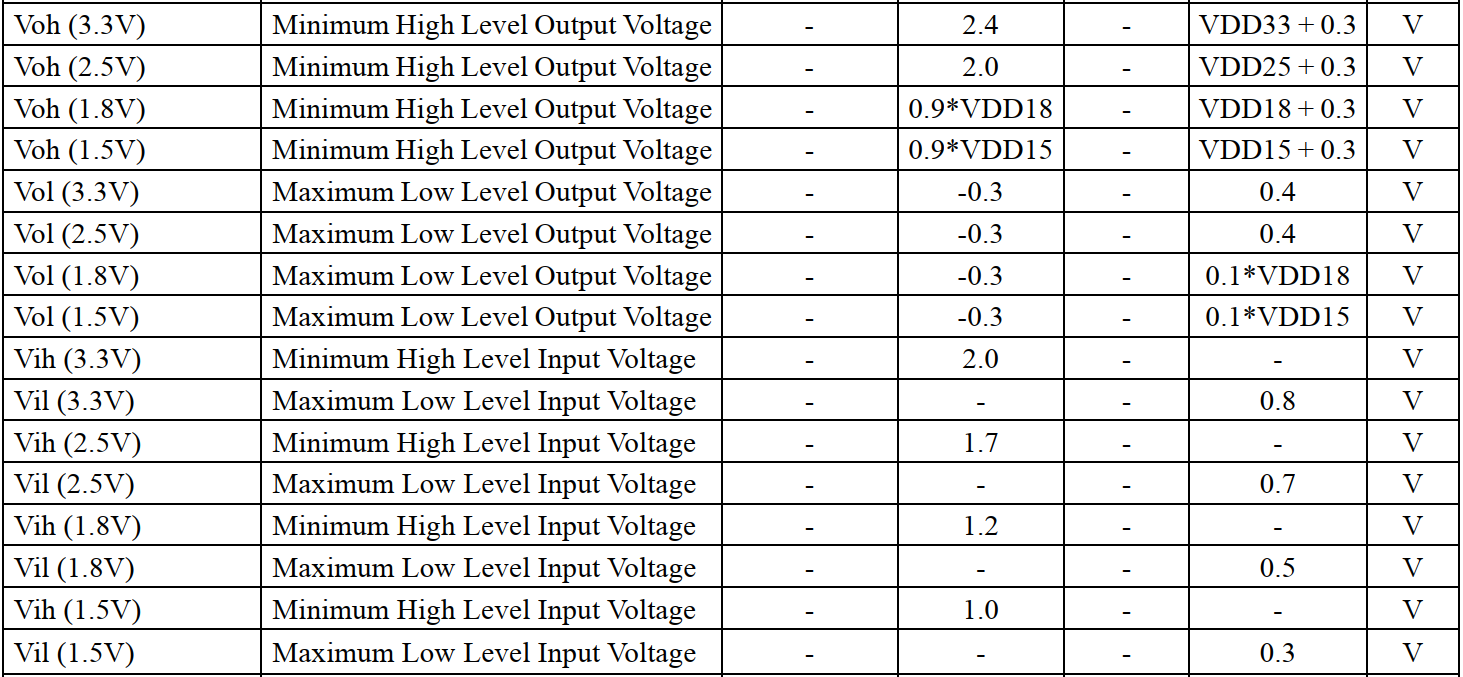

参照datasheet,当PHY芯片MDIO工作在1.5V时,Vil(1.5V)只有0.3V,导致不能正常工作。

5.1.2、为什么低温的时候才能复现?

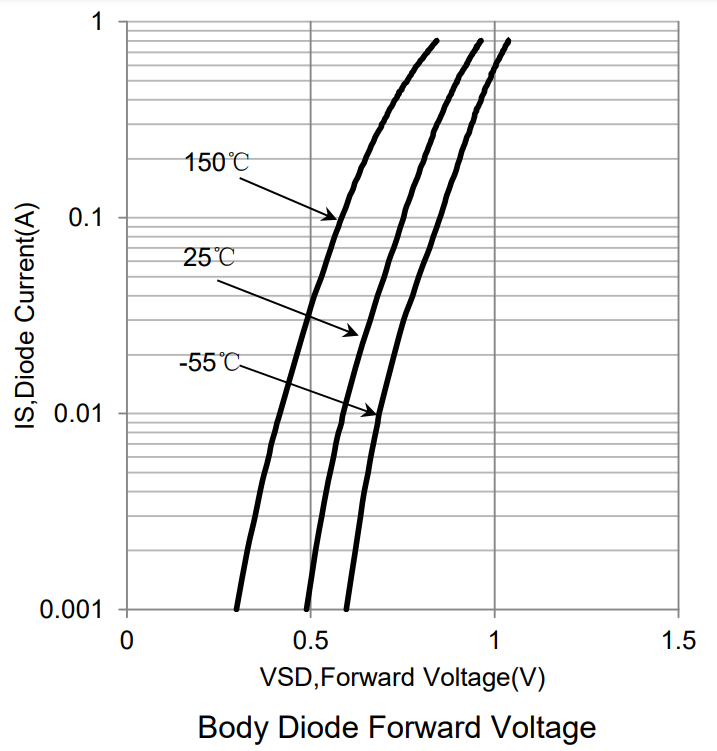

NMOS管体二极管在低温下导通电压会变大!

PS:二极管导通电压随着温度上升而下降。

723

723

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?