文章目录

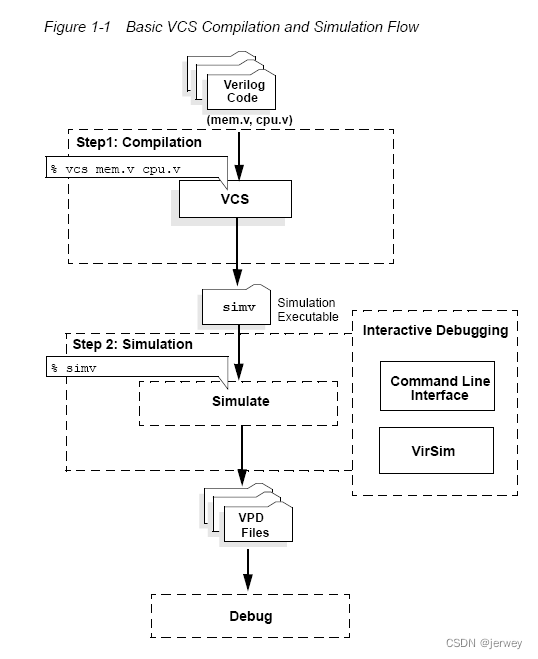

图中步骤:

- vcs 源文件[编译开关选项] —生成二进制可执行文件simv

- simv [run_time_options]

VCS仿真工具的使用/技巧

语法

vcs source_files [source_or_object_files] options

- source_files

The Verilog, OpenVera assertions, or OpenVera testbench source files for your design separated by spaces. - source_or_object_files

Optional C files (.c), object files (.o), or archived libraries (.a). These are DirectC or PLI applications that you want VCS to link into the binary executable file along with the object files from your Verilog source files. - Options

Compile-time options that control how VCS compiles your Verilog source files.

Not all the compile-time and runtime options described in this file work in VCS Basic.

For a list of options that do not work in VCS Basic, consult the VCS_Basic_Intro.pdf file.

常用命令

VCS常用命令詳解

https://blog.csdn.net/burningCky/article/details/111558398

https://blog.csdn.net/bcs_01/article/details/79803304

VCS对verilog模型进行仿真包括两个步骤:

-

- 编译verilog文件成为一个可执行的二进制文件命令为:vcs source_files

-

- 运行该可执行文件:./simv

VCS的+ -区别

“-”的一般是编译时用的,编译工具自带的。

“+"的是插件,环境,验证语言,等等加的,可扩展的,自定义的。

vcs常用的命令选项如下:

-cm line|cond|fsm|tgl|obc|path 设定coverage的方式

+define+macro=value+ 预编译宏定义

-I 进入交互界面

-l filename log文件名

-P pli.tab 定义PLI的列表(Tab)文件

+v2k //使用Verilog 1364-2001标准;Enables new language features in the proposed IEEE 1364-2001 standard. See “Implemented IEEE Std 1364-2001 Language Constructs” on page 2-23. Enables the use of new Verilog constructs in the 1364-2001 standard.

-y 定义verilog的库

-notice 显示详尽的诊断信息

-o 指定输出的可执行文件的名字,缺省是simv

+ nospecify 不对SPECIFY 模块进行时序检查和路径延时计算

+ notimingcheck 不进行时序检查;但是还是把path延时加入仿真中

-help //vcs帮助,有各编译选项意义;

-full64 //以64位模式编译设计并创建64位可执行文件用于64位模式下的模拟;

-vpi //允许使用vpi PLI访问例程;

-sverilog //允许在Accellera systemVerilog规范中使用Verilog语言扩展;

-cpp //指定C ++编译器

-debug_pp //允许转储到VPD并使用UCLI命令和DVE;

-debug //启用UCLI命令和DVE;

-debug_all //启用UCLI命令和DVE,也使线路步进;

-notice //启用详细的诊断消息;

+lint=[no]ID|none|all,... //使能或者禁用verilog的lint消息;

+rad //对设计进行辐射技术优化;

+vcs+lic+wait //Tell vcs to wait for a network ticense if none is avaitable;

//如果没有可用的通知,则告诉VCS等待网络许可证;当所有的license都不可用时,等待vcs的license

Note: Use +vcs+lic+wait ( or -licwait <minute> or -licqueue in Unified Use Model ) to queue for license

vcs中license相关的run cmd:+vcs+lic+wait,无限的等待下去;

+licwait timeout,最多等待指定的时间;

-f <filename> //指定一个文件,其中包含源文件和编译时选项的路径名列表;Specifies a file that contains a list of pathnames to source files and compile-time options

-o <name> //指定输出可执行文件的文件名,默认为 simv;

-R //该选项告诉VCS在编译完后直接运行可执行程序,若没有该选项,那么vcs在编译后直接退出;

-l <filename> //(小写字母L)如果包含-R,-RI或-RIG选项,则指定VCS记录编译消息和运行时消息的日志文件;

-Mupdate[=0]:默认情况下,VCS会在编译之间覆盖Makefile。 如果希望在编译之间保存Makefile,请输入此内容选项与0参数。输入不带0参数的参数,指定默认情况下,增量编译和更新Makefile文件;

-CFLAGS <options> //将选项传递给C编译器,允许多个-CFLAGS,允许传递C编译器优化级别。

-timescale=<time_unit>/<time_precision> //指明时间精度;

-ucli //在运行时指定UCLI模式;

+incdir+<directory> //指定包含使用`include 编译器指令指定的文件的目录,可以指定多个目录,用+字符分隔每个路径名称; 添加include 的文件夹

//指定包含包含`include文件的文件夹,以方便后续编译文件时不用逐个写出所有文件的路径,只需将其在pkg中include一下即可

+libext+<extension> //指定VCS仅在具有指定扩展名的Verilog库目录中搜索源文件,可以指定多个扩展名,用+字符分隔每个扩展名。例如+libext++.v指定搜索没有扩展名和库扩展名为.v的库文件。 输入-y选项时输入此选项。

+systemverilogext+<ext> //指定包含SystemVerilog源代码的源文件的文件扩展名;

-gui[=<dve|verdi>] //启动用户指定的图形用户界面,如果未提供参数,则在检测到有效的VCS_HOME环境变量时,VCS将启动Verdi。 否则DVE将默认启动;

-vcd <filename> //将输出VCD文件名设置为指定文件。默认文件名为verilog.dump。Verilog源代码中的$dumpfile系统任务将覆盖此选项;

-verdi //使用verdi图形界面;

+vcdfile+<filename> //指定想要用于后期处理的VCD文件;

-vpd_file <filename> //在运行时,定义VCS写入的VPD文件的替代名称,而不是缺省名称vcdplus.vpd;

+define+VCS //定义全局的VCS,编译器在编译时如果源文件有类似`ifdef VCS等字样,那么会执行定义之后的代码。

+vcs+vcdpluson //编译选项,加入后会使能产生vpd文件,默认文件名vcdplus.vpd

VCS有命令行模式和图形模式,图形模式使用的是DVE,命令交互模式使用的是Unified Command-line Interface (UCLI) 。ucli 为vcs的命令交互模式,需要在编译时加入参数以开启ucli,否则ucli交互时只能使用简单的’run’、‘dump’、'quit’命令。

-

-h or -help

列出最常用的编译时和运行时选项的说明 -

-gui[=<dve|verdi>]

运行时打开DVE窗口

启动用户指定的图形用户界面。如果没有给出参数,当检测到有效的 VC_HOME 环境变量时,VCS 将启动 Verdi。否则将默认启动 DVE。 -

-i

Specifies a file containing UCLI commands that VCS executes when simulation starts.

需要在编译时加入参数以开启ucli,否则ucli交互时只能使用简单的’run’、‘dump’、'quit’命令。

+incdir + <目录> :指定目录,该目录包含使用`include编译器指令指定的文件。 您可以指定多个目录,并用+字符分隔每个路径名。

+libext + <扩展名>:指定VCS仅在具有指定扩展名的Verilog库目录中搜索源文件。您可以指定多个扩展名,并用+字符分隔每个扩展名。例如,+ libext ++。v指定不带扩展名的搜索库文件和带.v扩展名的库文件。输入-y选项时,请输入此选项。

+liborder:指定在vcs命令行后的库中搜索模块定义,该库中包含一个未解决的实例,然后在vcs命令行中使用未解决的实例搜索该库之前的库。

+librescan指定始终使用vcs命令行上指定的第一个库开始搜索未解析的模块定义。

+libverbose: 当VCS在Verilog库目录中的源文件中找到模块定义时,告诉VCS显示一条消息,该消息可解析VCS在源文件,库文件或库目录中的另一个文件中读取的模块实例化语句。

+lint = [no] ID | none |all,…:启用或禁用有关您的Verilog代码的Lint消息。

覆盖率

性能分析

https://zhuanlan.zhihu.com/p/619230970

1 编译性能分析

选项-pcmakeprof来进行分析,可以把编译过程中的每一步所花费的时间做分析打印,并在编译日志的结尾进行输出

vcs -sverilog -pcmakeprof test.sv

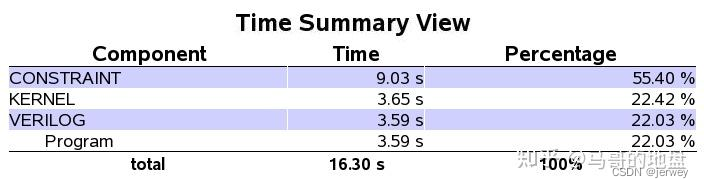

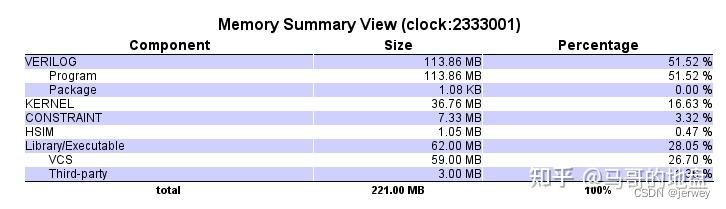

2 仿真性能分析

以相对“重量级”的方式进一步详细分析仿真运行的性能信息。

添加编译选项-simprofile,并且添加仿真选项-simprofile time 或mem来分析消耗的仿真CPU时间,以及消耗的内存。

(这个仿真选项后面除了跟time观测仿真时间信息还可以加:如mem收集服务器内存消耗信息等,当然也可以如time+mem同时收集)

这种“重量级”的方式,虽然会拖慢仿真时间,但一个优势是收集的信息更加详细,可以更直观的看到各部分资源消耗百分比,更好的协助我们找到消耗时间的性能瓶颈,提供优化方向和缩小优化范围。

参考:

查看详细的各个模块(module,package,pli等)占用时间和内存。(html txt格式报告)

vcs -simprofile or vcs -lca -simprofile

simv -simprofile time

#或者

vcs -simprofile

simv -simprofile mem

仿真结束之后会产生一个 profileReport.html文件

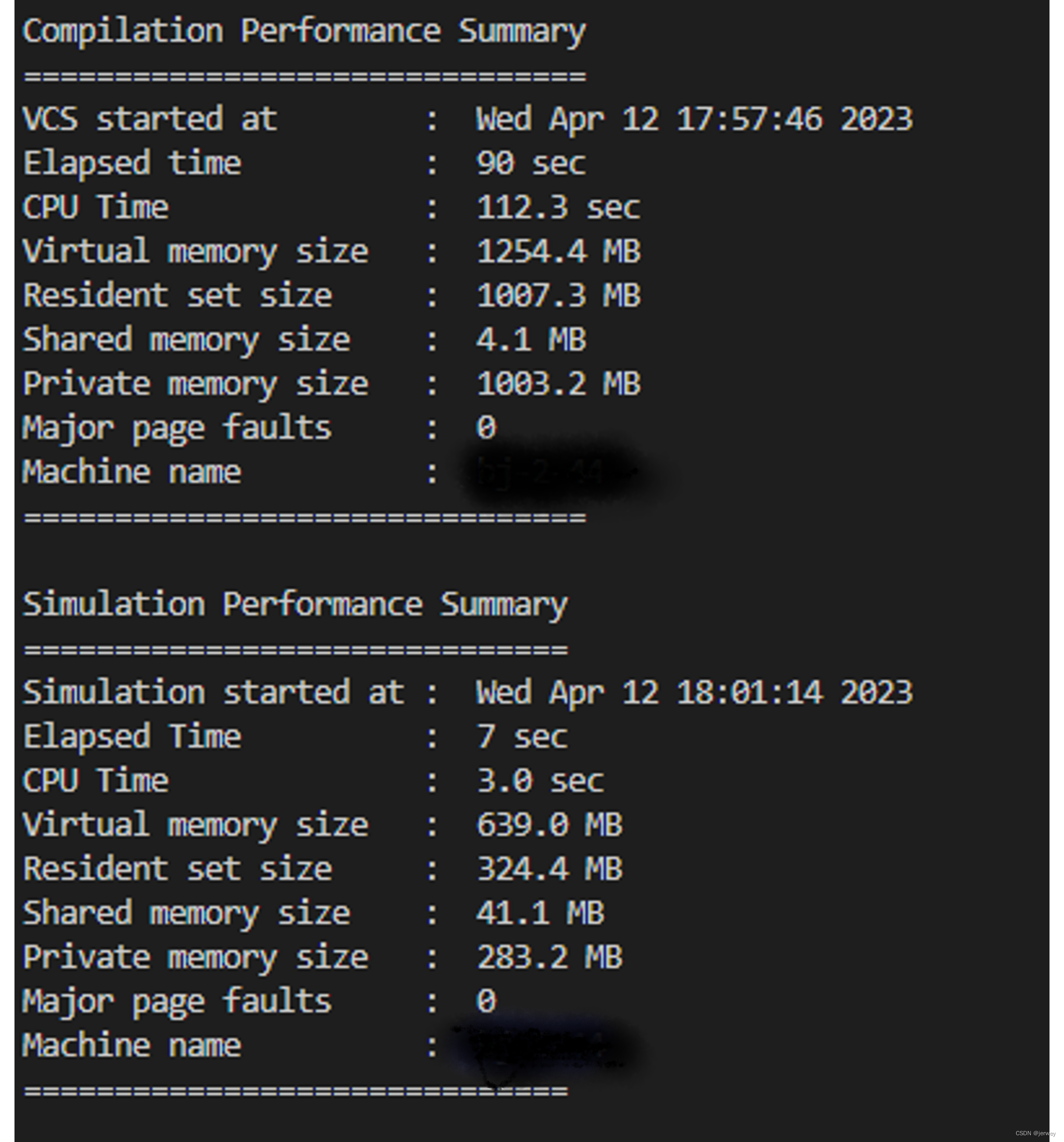

3 补充

以“轻量级”的方式输出编译和运行仿真过程中的性能汇总信息

通过添加-reportstats来分析VCS编译和仿真所占用的CPU资源使用情况。

show the summary time and mem of compile and runtime.

方法:

增加vcs编译选项 & simv仿真选项:-reportstats,如下

vcs –reportstats

simv -reportstats

工具将会直接把编译和运行的汇总性能报告直接打印在屏幕上

vcs -simprofile=uvm 查看UVM相关的资源消耗。(html txt格式报告)

加速

编译加速

1 VCS Partition Compile:

分块编译是将单线程编译的工作,拆分成多个小的子线程,去并行执行,从而达到减少编译时间的目的,另外,在修改了部分代码重新进行编译的时候,也只需要编译修改代码的部分,其他的不需要重新编译,进一步减少了编译的时间。

功能:将DUT和TB分成若干partition,调用多核分别编译。对于二次编译,只编译修改的partition。

命令:

2 VCS增量编译:

vcs –partcomp

3 并行编译

(Compile-Time Options)-j<number_of_processes>

Specifies the number of processes to use for parallel compilation.

There is no space between the j character and the number.

指定用于并行编译的进程数。

j字符和数字之间没有空格。(但是该方法不建议使用,因为根据实际经验会产生莫名逻辑错误问题,看起来还不成熟,Synopsys并没有优化的很好。)

仿真加速FGP

fgp 仿真加速

FGP (Fine-Grained Parallelism): 细粒度并行仿真技术;VCS利用FGP技术动态调整算法,能够优化并充分利用多核和众核处理器平台,提高仿真性能

Two-step flow

% vcs -fgp -full64 <otherOptions>

% simv -fgp=[FGP-OPTIONS]

注意:

- compile 添加 -fgp, simulation 不添加, simv 会采用单核仿真

- -fgp 需在-full64 使用

⼀、加速原理

正常仿真任务提交到机器上后,采⽤单核仿真。通过将线程与cpu多核进⾏绑定,设置亲和性affinity,来提⾼仿真速度。

⼀般机器上会显⽰有⼏个物理核,如16个物理核,每个核的⼯作负载work load,如果本⾝已经⾼负载,则⽆法继续选取该核进⾏绑定。同

样,如果该核本⾝已经被其它jobs锁定,也⽆法选取。

⼆、vcs命令选项

-fgp

-fgp=num_threads:3,sync:buswait,auto_affinity -xdprof=diag:ruse,profile -reportstats

选⽤4核,⾃动设置,打印诊断信息,报告状态。

三、fgp. affinity打印信息

机器cpu数量,cpu 未被选择原因,是high work load 还是 locked by other simulation process。

该功能需要核数量。

机器状态信息报告,包含cpu,%usr %nice %sys %iowait等等。

机器⾼负载cpu相关的进程信息,包含pid %usr %system %guest %CPU command等。

四、FGP_AFFINITY_FAILED

cpu_affinity/auto_affinity failed

simulation requested 4 cores but only 3 cores are available

VCS流程

https://ac.nowcoder.com/discuss/961531

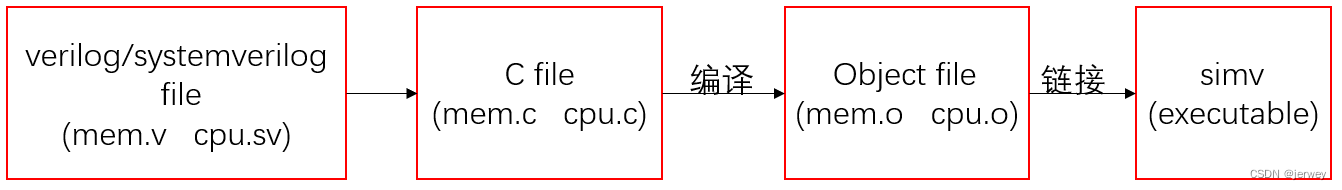

VCS是编译型verilog仿真器,处理verilog的源码过程如下:

VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

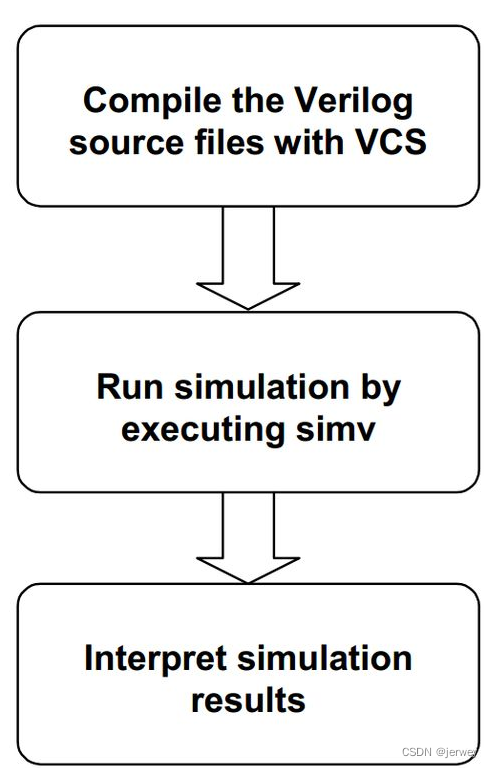

VCS使用步骤,先编译verilog源码,再运行可执行文件:

编译命令的格式:vcs sourcefile [compile_time_option] (编译选项用来控制编译过程)

执行仿真命令格式:./simv [run_time_option]

VCS与verdi联合进行单步调试

https://www.cnblogs.com/csjt/p/15623721.html

ucli命令

VCS有命令行模式和图形模式,图形模式使用的是DVE,命令交互模式使用的是ucli。

需要在编译时加入参数以开启ucli,否则ucli交互时只能使用简单的’run’、‘dump’、'quit’命令。

推荐编译时添加参数如下:

‘-debug_access<+option>’ for post-process debug 显然,应该有很多参数可选

‘-debug_access+classdbg’ for testbench debug

‘debug_access+all’ for capabilities

启动方式:./simv -ucli

vcs定义宏

在 VCS(Verilog Compiler Simulator)以及其他一些 Verilog 编译工具中,+define+MY_MACRO 和 -D 都用于定义宏,但它们在使用方式和工具支持的通用性上存在一些区别,下面为你详细介绍:

相同点

两者的主要功能都是在编译时定义宏,这些宏可以在 Verilog 代码里通过 ifdef、ifndef、else 和 endif 等预处理指令来控制代码的条件编译,从而实现不同的编译选项和功能切换。

不同点

1. 使用语法

+define+MY_MACRO:这是 VCS 等工具特有的宏定义语法,其格式为+define+<宏名>。如果宏需要带参数值,格式为+define+<宏名>=<值>。例如:

vcs +define+MY_MACRO +define+DATA_WIDTH=32 my_design.v

-D:是一种更通用的宏定义方式,许多编译工具都支持这种语法。其格式为-D<宏名>或-D<宏名>=<值>。例如:

vcs -D MY_MACRO -D DATA_WIDTH=32 my_design.v

2. 工具支持范围

+define+:主要在 VCS 及其相关的编译环境中使用,是 VCS 为了与自身的命令行选项风格保持一致而采用的宏定义方式。如果使用其他非 Synopsys 系的编译工具,可能不支持该语法。-D:具有更好的通用性,不仅 VCS 支持,像 GCC(在 C/C++ 编译中)、iverilog(开源的 Verilog 仿真器)等多种编译工具都支持-D来定义宏。所以在跨工具、跨平台的代码编译中,使用-D能提高代码的可移植性。

3. 历史和习惯

+define+:是 VCS 传统的宏定义方式,在一些老的 VCS 项目中比较常见,长期使用 VCS 的开发者可能更习惯这种写法。-D:源于 Unix/Linux 系统下的编译器传统,很多开发者对这种语法比较熟悉,在一些需要兼顾不同工具的项目中更倾向于使用-D。

综上所述,虽然 +define+MY_MACRO 和 -D 功能相似,但 -D 具有更广泛的工具支持和更好的通用性,而 +define+ 则是 VCS 特定的语法风格。在实际使用中,可以根据项目需求和工具环境来选择合适的方式。

889

889

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?