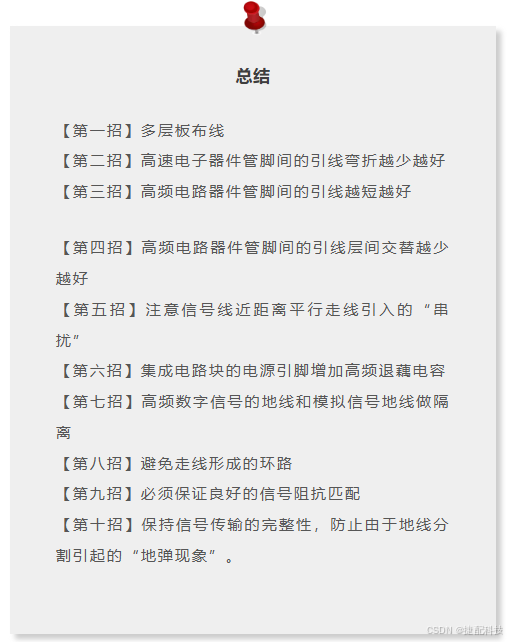

在电子工程的世界里,高频电路的设计无疑是一项挑战性极强的任务。当数字逻辑电路的频率触及或超越45MHz至50MHz的门槛,并且这些高频操作占据了整个电子系统相当的比例时,我们便将其定义为高频电路。这类电路的布线工作对于整个设计的成功至关重要。以下是十大秘籍,助您轻松驾驭高频电路布线。

秘籍一:采用多层板设计

高频电路通常具有高集成度和密集的布线需求。选择多层板不仅能够满足布线需求,还能有效减少电磁干扰。在PCB布局阶段,合理规划板层和尺寸,利用中间层进行屏蔽,实现就近接地,降低寄生电感,缩短信号传输路径,减少交叉干扰,从而提升电路的可靠性。

秘籍二:直线布线,减少弯折

在高频电路中,直线布线是减少信号辐射和耦合的关键。必要时,采用45度折线或圆弧转折,以最小化对外部的信号干扰。

秘籍三:缩短信号引线

高频信号的辐射强度与走线长度成正比。因此,对于时钟、晶振、DDR数据等高频信号,应尽可能缩短走线长度,以减少耦合和干扰。

秘籍四:减少层间交替

过孔(Via)的使用应尽可能减少,因为每个过孔都会引入额外的分布电容,影响信号的传输速度和质量。

秘籍五:警惕串扰

在布线时,要注意信号线近距离平行走线可能引入的串扰。通过在敏感信号线之间插入地线或地平面,增加信号线间距,以及优化走线方向,可以有效减少串扰。

秘籍六:增加退藕电容

在每个集成电路块的电源引脚附近增加高频退藕电容,以抑制电源引脚上的高频谐波,减少干扰。

秘籍七:数字与模拟地线隔离

为了避免数字信号地线和模拟信号地线之间的干扰,应进行适当的隔离,使用高频扼流磁珠或在合适位置进行单点互联。

秘籍八:避免环路

尽量避免形成环路,如果无法避免,应使环路面积尽可能小,以减少电磁辐射和干扰。

秘籍九:保证阻抗匹配

信号在传输过程中,阻抗匹配至关重要。不匹配会导致信号反射,形成过冲,影响信号稳定性。因此,应确保传输线的特性阻抗与负载阻抗相等,避免传输线出现突变或拐角。

秘籍十:防止地弹现象

保持信号传输的完整性,避免由于地线分割引起的“地弹现象”,确保电路的稳定性和可靠性。

53

53

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?