本文聚焦PCB布局设计中的三大核心环节——大电流环路优化、高频信号处理及接地系统构建,结合行业实践为硬件开发者提供可落地的设计指南。

一、大电流环路:降低EMI与热损耗的关键

1. 环路面积控制标准

大电流路径的包围面积应控制在20mm²以内。以12V/5A电源模块为例,采用2oz铜厚时,走线宽度需≥3mm。通过智能拼板系统优化走线路径,配合激光直接成像(LDI)技术实现±0.05mm的线宽精度。

二、高频信号布局:从EMI抑制到信号完整性

1. 关键元件布局规范

-

功率开关器件:MOS管与续流二极管间距≤5mm,SW节点铜箔面积压缩至最小(推荐0.8×1.2mm)

-

驱动信号:驱动IC到MOS栅极的走线长度控制在15mm内,线宽≥1.5mm

-

采样电路:检流电阻到控制IC的走线阻抗需<0.5Ω,采用四层板结构时走线距参考平面≤0.2mm

2. 抗干扰设计策略

-

差分信号:时钟信号对长度匹配误差<5mil,差分对间距≥3倍线宽

-

屏蔽措施:高频区域下方设置完整地平面,边缘进行包地处理

三、接地系统:

1. 分层接地架构

层级处理方式典型应用初级地单点接地+星型拓扑电源模块、电机驱动次级地浮地隔离+屏蔽层通信接口、传感器电路

2. 接地连接规范

-

功率地:大电流回路通过过孔阵列(≥4个/10mm²)连接到平面层

-

信号地:模拟地与数字地通过0Ω电阻单点连接,过渡区域设置10nF陶瓷电容

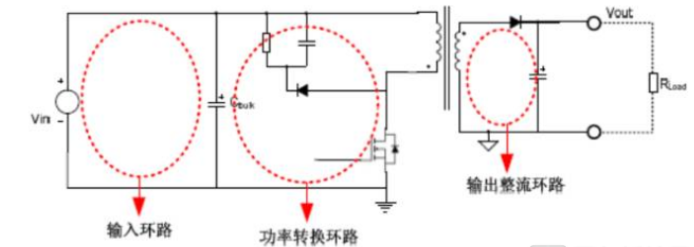

四、典型设计实例:DC-DC电源模块布局

1. 输入滤波电路

-

CIN(10μF)紧邻VIN引脚,与C_BYPASS(0.1μF)形成π型滤波

-

走线宽度:输入路径≥2.5mm,输出路径≥1.5mm

2. 功率级布局

-

MOS管与电感呈L型布局,SW节点铜箔面积压缩至0.6×1.0mm

-

检流电阻到FB引脚的走线阻抗<0.3Ω

3. 输出滤波

-

输出电容(220μF)靠近电感,Y电容跨接在初/次级地之间

-

反馈网络走线长度≤8mm,采用包地处理

图源网络,侵删

168

168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?