问题一

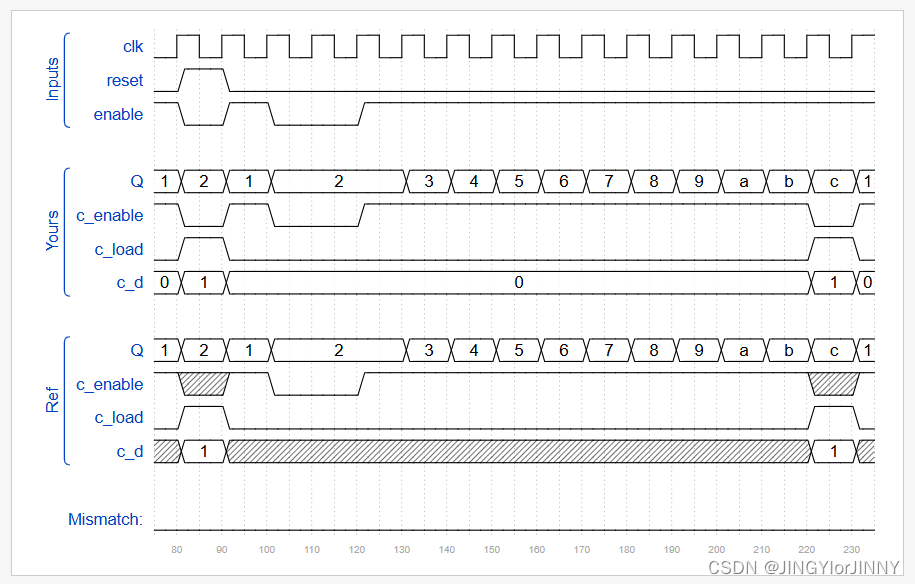

Design a 1-12 counter with the following inputs and outputs:

Reset Synchronous active-high reset that forces the counter to 1

Enable Set high for the counter to run

Clk Positive edge-triggered clock input

Q[3:0] The output of the counter

c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

logic gates

module count4(

input clk,

input enable,

input load,

input [3:0] d,

output reg [3:0] Q

);

The c_enable, c_load, and c_d outputs are the signals that go to the internal counter’s enable, load, and d inputs, respectively. Their purpose is to allow these signals to be checked for correctness.

//比较难理解c_load信号是干嘛的,准确来说,c_load指令负责当计数器复位或是计满后(12),将计数器再赋值为1(c_d)。而当c_load为低电平且输入使能信号enable为高电平时,c_enable为1使count4持续计数。

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

);

count4 the_counter (clk, c_enable, c_load, c_d ,Q );

assign c_load=reset|(Q==4'b1100&enable);

assign c_enable=(~c_load)&enable;

assign c_d=c_load ? 4'd1 : 4'b0;

endmodule

问题二

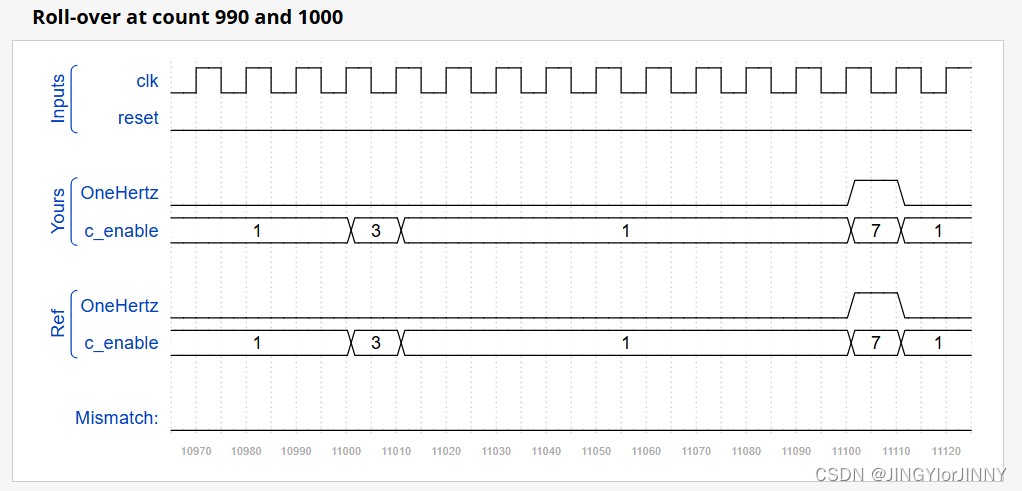

From a 1000 Hz clock, derive a 1 Hz signal, called OneHertz, that could be used to drive an Enable signal for a set of hour/minute/second counters to create a digital wall clock.(废话) Since we want the clock to count once per second, the OneHertz signal must be asserted for exactly one cycle each second(还是废话). Build the frequency divider using modulo-10 (BCD) counters and as few other gates as possible. Also output the enable signals from each of the BCD counters you use (c_enable[0] for the fastest counter, c_enable[2] for the slowest).

The following BCD counter is provided for you. Enable must be high for the counter to run. Reset is synchronous and set high to force the counter to zero. All counters in your circuit must directly use the same 1000 Hz signal.

module bcdcount (

input clk,

input reset,

input enable,

output reg [3:0] Q

);

//modulo-10(BCD)计数器的特点就是使用BCD码且只计十位,因此可以实现:10个1为10,10个10为100,10个100为1000的累加计数方式。

module top_module (

input clk,

input reset,

output OneHertz,

output [2:0] c_enable

);

wire [3:0] Q_10;

wire [3:0] Q_100;

wire [3:0] Q_1000;

assign c_enable[0]=1'b1;

bcdcount counter0 (clk, reset, c_enable[0], Q_10);

assign c_enable[1]=(Q_10==4'b1001 & c_enable[0]==1'b1)?1'b1:1'b0;

bcdcount counter1 (clk, reset, c_enable[1], Q_100);

assign c_enable[2]=(Q_100==4'b1001 & c_enable[1]==1'b1)?1'b1:1'b0;

bcdcount counter2 (clk, reset, c_enable[2], Q_1000);

assign OneHertz=(Q_1000==4'b1001)&(Q_100==4'b1001)&(Q_10==4'b1001);

endmodule

问题三

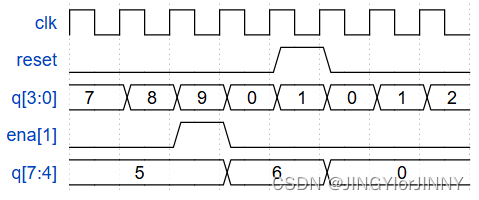

Build a 4-digit BCD (binary-coded decimal) counter. Each decimal digit is encoded using 4 bits: q[3:0] is the ones digit, q[7:4] is the tens digit, etc. For digits [3:1], also output an enable signal indicating when each of the upper three digits should be incremented.

You may want to instantiate or modify some one-digit decade counters.

//这道题主要需要搞清楚进位关系,例如ena[2]==1不仅需要q[7:4]已经计数到9,还需要在这个时钟下q[7:4]仍需加一(ena[1]==1)

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

assign ena[1]=(q[3:0]==4'b1001)?1'b1:1'b0;

assign ena[2]=(q[7:4]==4'b1001 && ena[1])?1'b1:1'b0;

assign ena[3]=(q[11:8]==4'b1001 && ena[2])?1'b1:1'b0;

always@(posedge clk) begin

if (reset) q[3:0]<=4'b0000;

else if (q[3:0]<4'b1001) q[3:0]<=q[3:0]+1'b1;

else if (q[3:0]==4'b1001) q[3:0]<=4'b0000;

end

always@(posedge clk) begin

if (reset) q[7:4]<=4'b0000;

else if (q[7:4]<4'b1001) begin

if (ena[1]==1'b1) q[7:4]<=q[7:4]+1'b1;

else if (ena[1]==1'b0) q[7:4]<=q[7:4];

end

else if (q[7:4]==4'b1001) begin

if (ena[1]==1'b1) q[7:4]<=4'b0000;

else if (ena[1]==1'b0) q[7:4]<=q[7:4];

end

end

always@(posedge clk) begin

if (reset) q[11:8]<=4'b0000;

else if (q[11:8]<4'b1001) begin

if (ena[2]==1'b1) q[11:8]<=q[11:8]+1'b1;

else if (ena[2]==1'b0) q[11:8]<=q[11:8];

end

else if (q[11:8]==4'b1001) begin

if (ena[2]==1'b1) q[11:8]<=4'b0000;

else if (ena[2]==1'b0) q[11:8]<=q[11:8];

end

end

always@(posedge clk) begin

if (reset) q[15:12]<=4'b0000;

else if (q[15:12]<4'b1001) begin

if (ena[3]==1'b1) q[15:12]<=q[15:12]+1'b1;

else if (ena[3]==1'b0) q[15:12]<=q[15:12];

end

else if (q[15:12]==4'b1001) begin

if (ena[3]==1'b1) q[15:12]<=4'b0000;

else if (ena[3]==1'b0) q[15:12]<=q[15:12];

end

end

endmodule

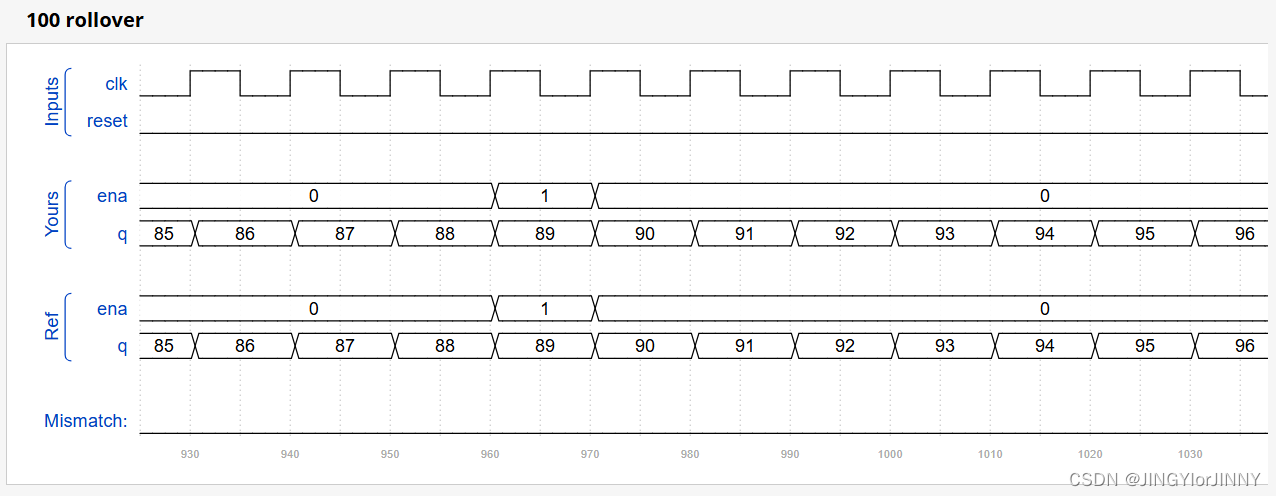

问题四

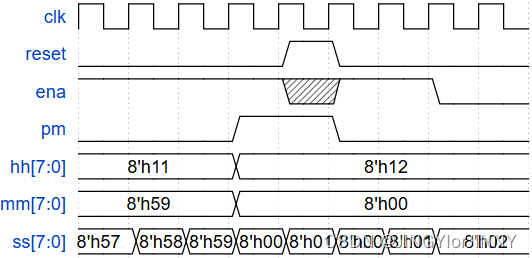

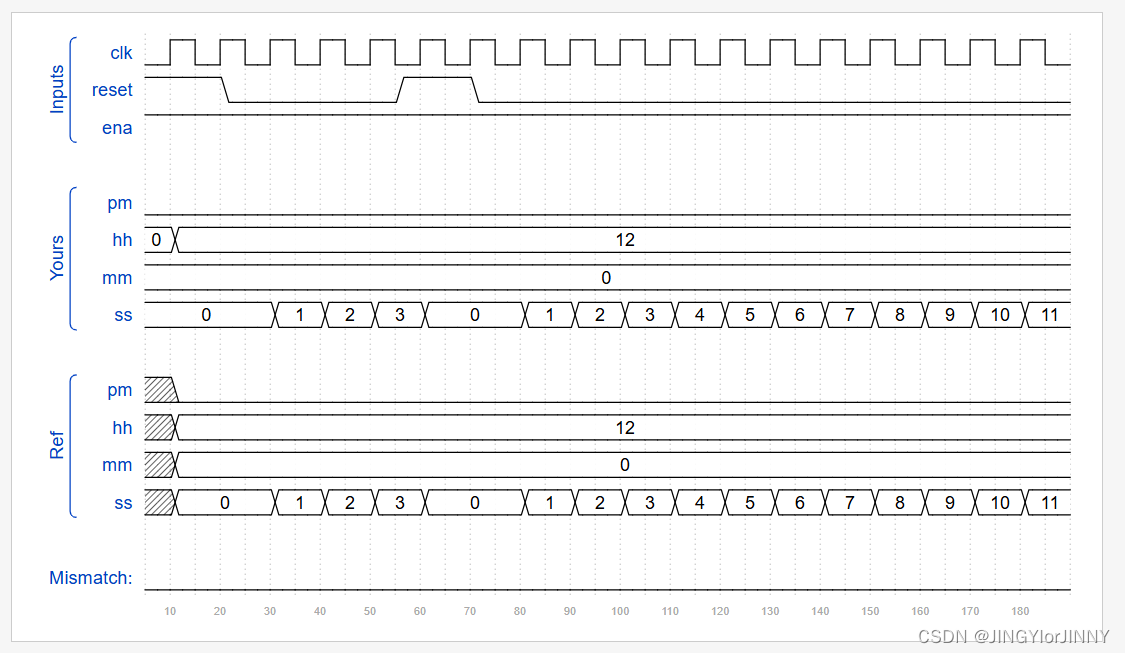

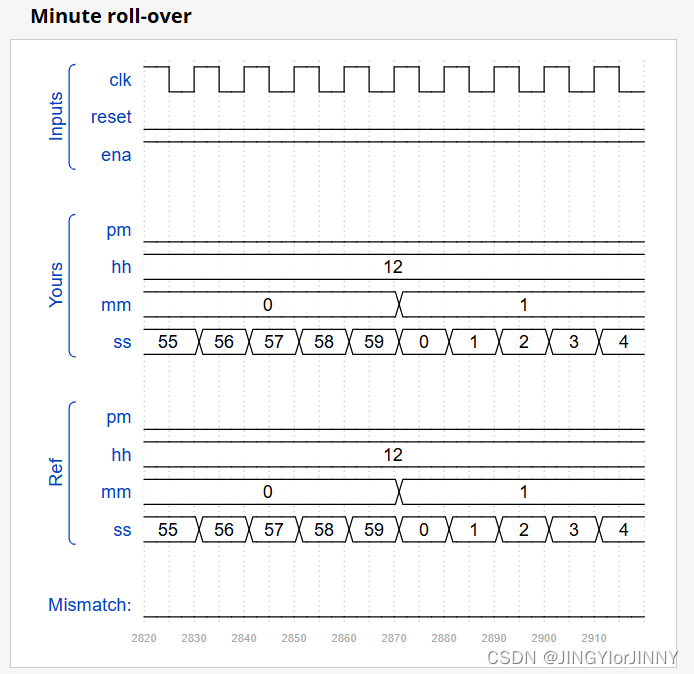

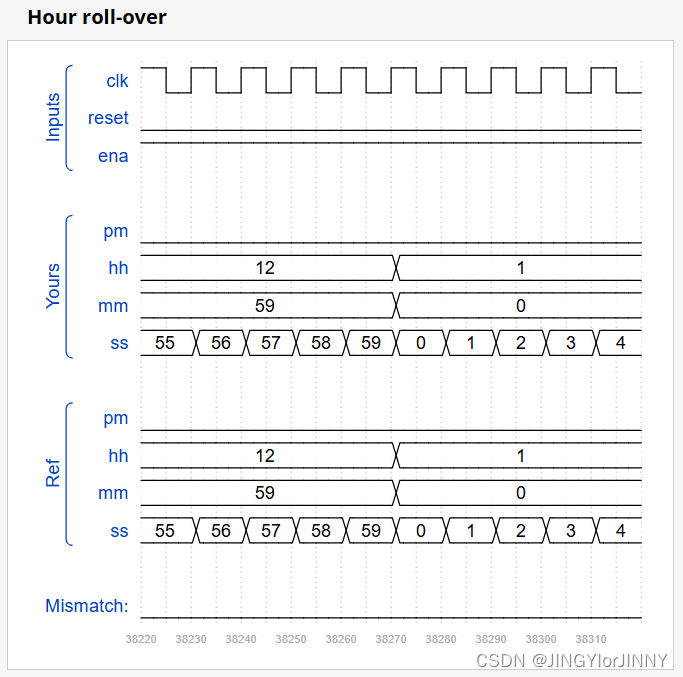

Create a set of counters suitable for use as a 12-hour clock (with am/pm indicator). Your counters are clocked by a fast-running clk, with a pulse on ena whenever your clock should increment (i.e., once per second).

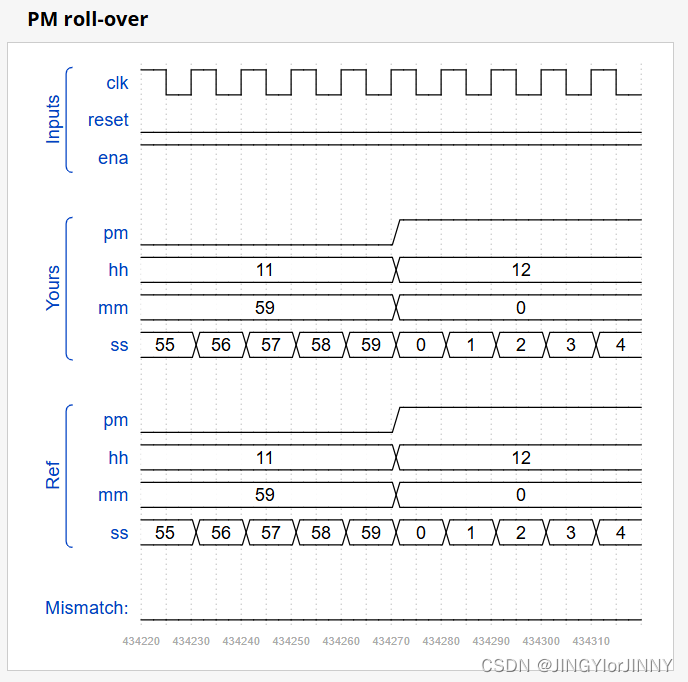

reset resets the clock to 12:00 AM. pm is 0 for AM and 1 for PM. hh, mm, and ss are two BCD (Binary-Coded Decimal) digits each for hours (01-12), minutes (00-59), and seconds (00-59). Reset has higher priority than enable, and can occur even when not enabled.

The following timing diagram shows the rollover behaviour from 11:59:59 AM to 12:00:00 PM and the synchronous reset and enable behaviour.

//这道题只是特别麻烦而已,注意ss,mm,hh都要实现BCD计数。此外,pm的翻转在11->12之间,hh计满后归位为8’h01(很容易按照惯性思维以为pm的翻转在12->00之间或者hh计满后归位为8’h00)

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire ena_m;

wire ena_h;

assign ena_m=(ss==8'b0101_1001)?1'b1:1'b0;

assign ena_h=(mm==8'b0101_1001 && ena_m)?1'b1:1'b0;

always@(posedge clk) begin

if (reset) begin

ss<=8'h00;

end

else if (ena) begin

if(ss[3:0]<4'b1001) ss[3:0]<=ss[3:0]+1'b1;

else if (ss[3:0]==4'b1001 && ss[7:4]<4'b0101) begin

ss[7:4]<=ss[7:4]+1'b1;

ss[3:0]<=4'b0000;

end

else if (ss[3:0]==4'b1001 && ss[7:4]==4'b0101) begin

ss[7:4]<=4'b0000;

ss[3:0]<=4'b0000;

end

end

end

always@(posedge clk) begin

if (reset) begin

mm<=8'h00;

end

else if (ena_m) begin

if (mm[3:0]<4'b1001) mm[3:0]<=mm[3:0]+1'b1;

else if (mm[3:0]==4'b1001 && mm[7:4]<4'b0101) begin

mm[3:0]<=4'b0000;

mm[7:4]<=mm[7:4]+1'b1;

end

else if (mm[3:0]==4'b1001 && mm[7:4]==4'b0101) begin

mm[3:0]<=4'b0000;

mm[7:4]<=4'b0000;

end

end

else mm<=mm;

end

always@(posedge clk) begin

if (reset) begin

pm<=0;

hh<=8'h12;

end

else if (ena_h) begin

if (hh[3:0]<4'b1001 && hh[7:4]==4'b0000) hh[3:0]<=hh[3:0]+1'b1; //0~8->1~9

else if (hh[3:0]==4'b1001 && hh[7:4]==4'b0000) begin //9->10

hh[3:0]<=4'b0000;

hh[7:4]<=4'b0001;

end

else if (hh[3:0]==4'b0000 && hh[7:4]==4'b0001) begin //10->11

hh[3:0]<=4'b0001;

hh[7:4]<=4'b0001;

end

else if (hh[3:0]==4'b0001 && hh[7:4]==4'b0001) begin //11->12

hh[3:0]<=4'b0010;

hh[7:4]<=4'b0001;

pm<=~pm;

end

else if (hh[3:0]==4'b0010 && hh[7:4]==4'b0001) begin //12->0

hh<=8'h01;

end

end

end

endmodule

1929

1929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?