【华为笔试真题】第二篇 (11~20)

11. 组合逻辑和时序逻辑

A

组合逻辑(combinational logic):组合逻辑电路不具备存储功能,输出数据由输入的状态决定。电路的分析和设计往往通过逻辑代数和真值表完成。应用实例:加法器,乘法器,编码器,解码器,多路选择器;

时序逻辑(sequential logic):时序逻辑是指那些具有存储能力的逻辑电路,其输出不仅依赖于当前的输入,还依赖于电路之前的状态或者历史输入(因此电路中包含反馈路径和存储元件)。电路的分析和设计比组合逻辑更复杂,往往需要使用状态图和状态表。应用实例:计数器、寄存器、存储器、时钟驱动的电路等。

B

12. 基本总线

B

基本总线包含数据总线(data bus),地址总线(address bus)和控制总线(control)。

数据总线(Data Bus):用于传输数据的通道,其宽度(即位数)决定了可以同时传输的数据量。

地址总线(Address Bus):用于指定源或目标的内存地址或I/O地址。地址总线的宽度决定了系统可以寻址的最大内存容量。

控制总线(Control Bus):用于传输控制信号,这些信号用于管理和控制计算机系统中的数据传输和处理过程。包括读/写信号、中断请求信号、时钟信号等。

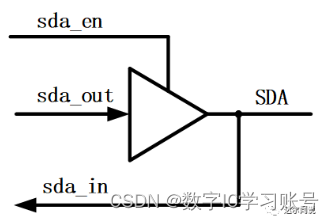

而三态门(tri-state gate)的作用是为了允许多个设备共享同一总线,从而确保双向数据总线中的正确传输。一种三态门逻辑解释如下:

当sda_en为高电平时,SDA作为输出口输出sda_out的数据;当sda_en为低电平时,三态门处于高阻态,此时SDA作为输入口将数据输入给sda_in。

13.加法器

B

对于加法器:两个加数位宽为别为m和n,其相加后的总位宽应为:[max(m,n)+1]

对于乘法器:两个乘数位宽分别为m和n,其相乘后的总位宽应为:m+n

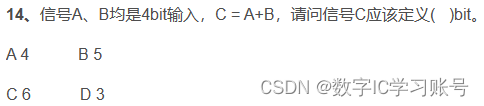

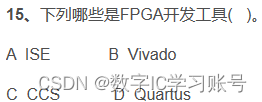

14.FPGA开发工具

C

常见的FPGA开发工具有:

Xilinx Vivado(Xilinx),Intel Quartus Prime(前身为Altera,后被Intel收购),Lattice Diamond(Lattice),Microsemi Libero SoC(前身为Microsemi,现为Microchip Technology的一部分),Xilinx ISE(负责Xilinx公司FPGA旧型号的开发)

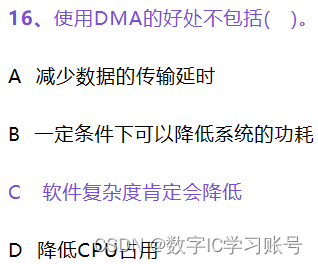

15.DMA访问协议

C

DMA(direct memory access),直接存储器访问,在DMA出现之前,CPU与外设之间的数据传输由程序直接控制。当外设需要和CPU进行数据交换时,外设需要向CPU发送请求信号,使CPU暂停正在执行的程序去执行数据的输入输出操作,待数据传送结束后,CPU再继续执行被暂停的程序。

DMA的出现就是为了解决批量数据的输入/输出问题。DMA是指外部设备不通过CPU而直接与系统内存交换数据的接口技术。通常系统总线是由CPU管理的,在DMA方式时,就希望CPU把这些总线让出来,即CPU连到这些总线上的线处于高阻态,而由DMA控制器接管,控制传送的字节数,判断DMA是否结束,以及发出DMA结束信号。

由于DMA减少了CPU介入数据传输的次数,因此减少了系统使用功耗。同时,在DMA使用总线传输数据时,CPU可以继续执行其他操作,这提升了处理器的整体效率。

对于A选项,当CPU进行数据传输时,需要先将数据从I/O端口复制到registers上,再复制到内存之中,这使得CPU处理数据传输的效率不如DMA。

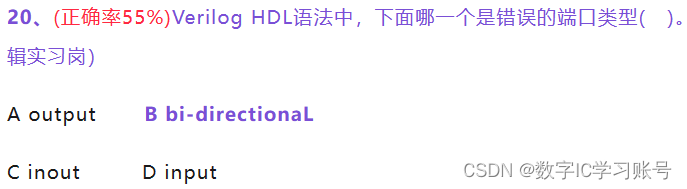

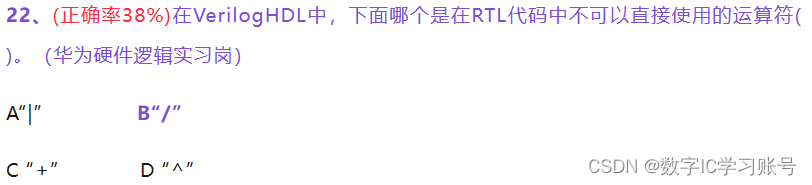

16.Verilog HDL语法

Verilog中有三种端口类型:input,output,inout,在verilog中的使用方式如下:

module test(

input wire sel,//输入输出控制信号,sel为1时向外输出数据,sel为0时向内输入数据

input wire data_out,//由内部模块传来要发送给双向数据总线向外输出的数据

inout wire data_bus,//双向数据总线

output wire data_in//接收双向数据总线从外部输入的数据后输出到其他内部模块

);

assign data_in =data_bus;//data_in:接收双向数据总线从外部输入的数据

assign data_bus =(sel==1'b1)?data_out :1'bz;//data_bus:sel为1时双向数据总线向外输出数据,sel为0时双向数据总线为高阻态可以向内输入数据

endmodule

B

|:一元运算时表示归约或,二元运算表示按位或;

^:一元运算表示规约异或,二元运算表示按位异或;

在Verilog中,虽然“/”除法运算符在语法上可以直接应用于RTL(寄存器传输级)代码中,但在实际的硬件设计和实现过程中,直接使用除法运算通常需要谨慎考虑。这是因为除法运算相比于加法、减法和乘法运算,在硬件上实现起来更为复杂和资源消耗更高,尤其是在涉及到整数除法时。

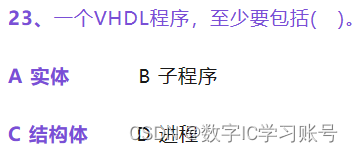

17.VHDL语法的基本认识

A,C

不管其功能复杂成度多大,VHDL程序的结构基本相同,一般由库、程序包、实体、结构体及配置语句构成。其中实体和结构体两部分是必需的,由这两部分即可构成一个简单的VHDL程序。

以关键字ENTITY引导、END ENTITY结尾的语句部分称为实体。VHDL的实体描述电路器件的外部情况及各信号端口的基本性质。

以关键字ARCHITECTURE、END ARCHITECTURE结尾的语句部分,称为结构体。结构体描述电路器件的内部逻辑功能或电路结构。

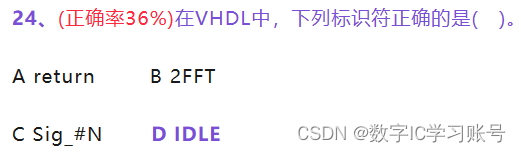

D

VHDL基本标识符的要求(87标准)如下所示:

1.由大小写字母、数字和下划线组成;

2.字母开头

3.下划线不可以连续使用

4.下划线不可以做结尾

5.基本标识符中的英文字母不分大小写

6.VHDL的保留字不能做标识符使用(例如本题的return)

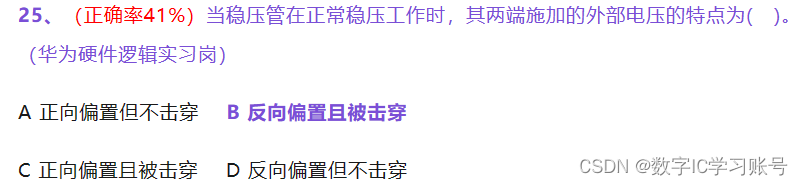

18.半导体器件–稳压管

B

齐纳二极管为常用的稳压二极管,其主要应用齐纳击穿的原理:当给PN结施加反向电压时,在低电压(小于5V)的状态下,由于电子隧穿效应,电子可以穿越bandgap直接从价带跃迁到导带,称为齐纳击穿;在更高的逆向电压状态下,由于连锁反应(一个电子撞击electron-hole bond导致产生多个电子),电流急剧增加,此时被称为雪崩击穿。

齐纳击穿的特点:器件突然从高阻态变为低阻态,允许电流通过,且器件两端电压保持相对恒定(电流大幅度变化,电压几乎不变),这也是齐纳二极管用作稳压二极管的基本原理。

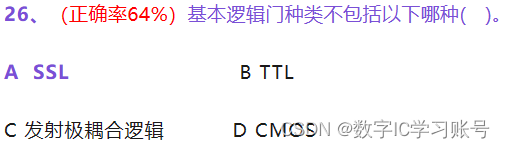

19.基本的逻辑门技术种类

A

TTL(transistor-transistor logic)门电路是由双极型晶体管组成的集成门,由于其输入级和输出级均采用了晶体管,所以称为晶体管-晶体管逻辑门电路,简称TTL门电路。TTL的特点有:速度快(比CMOS快),功耗高(静态功耗比CMOS高,因为TTL使用双极性晶体管,在非导电情况下仍然消耗电流),抗噪声能力强,电压范围较窄。

CMOS门电路是由PMOS和NMOS管组成的互补电路,静态功耗小(几乎只在切换状态的时候消耗能量),扛干扰能力强,工作稳定性好,且高输入阻抗(对前级电路几乎不产生负载)。

ECL(emitter-coupled logic)发射极耦合逻辑是一种用于数字电路的高速逻辑门技术,特别是在需要极高速操作的应用中,这是因为ECL门电路工作在非饱和状态,因此具有相当高的速度。

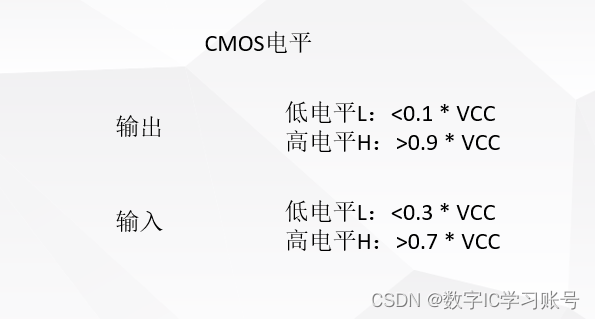

B

TTL电平信号规定,+5V等价于逻辑“1”,0V等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。

CMOS电源的电平比较宽,为3-15V。

电平标准:

TTL电路:对于输入来说的,如果这个信号是低于0.8V的话,在电路中我们会就会把它认为是一个低电平 0。如果输入是大于2.0V,那这个时候我们是认为它是高电平 1。对于输出来讲,输出的低压最高只能达到0.4V,低于0.8伏的话,会默认是低电平 0 。如果说是高于2.4V,会认为他是一个高电平 1。

CMOS电路:

不同种类的电平应用于不同场合,例如单片机使用TTL电平,电脑使用RS232,在不同电平设备之间进行通讯时,转换芯片需要投入应用。

TTL和CMOS之间的相互驱动:

一种情况,TTL电路的输出对接CMOS的输入。TTL电平输出最低是小于0.8V的,而对于CMOS来说,输入低电平的最大值是1.5V,显然TTL的输出低电平是满足CMOS输入低电平的。看看高电平的情况,TTL的高电平输出最低是2.4V,而CMOS的高电平最低是3.5V。如果TTL的输出正好在2.4V-3.5V之间,那么CMOS就无法判断他的状态,所以TTL电路输出驱动CMOS输入,是无法实现的。

另外一种情况,CMOS的输出对接TTL的输入。对于电压是5V的情况下,CMOS电平的输出根据公式可以得出,低电平小于0.5V,高电平是4.5V。TTL的输入,对于小于0.5V的输入必定是认为低电平的。对于大于4.5V的输入也是肯定认为是高电平的,所以TTL的输入电平是可以满足CMOS的输入的。CMOS电平是可以完全驱动TTL的,反之则是不行的。

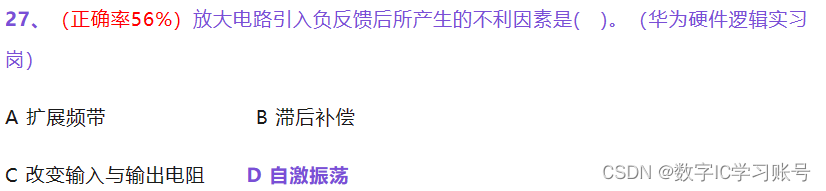

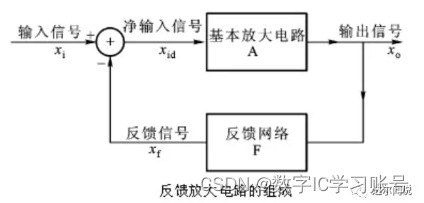

20.负反馈相关知识

D

将一个系统的输出信号的一部分或全部以一定方式和路径送回到系统的输入端作为输入信号的一部分,这个作用过程叫——反馈。按反馈的信号极性分类,反馈可分为正反馈和负反馈。负反馈是指返回来的信号与输入信号的极性相反。

采用负反馈使得放大器的闭环增益趋于稳定,消除了开环增益的影响。电子线路中阻抗匹配是一重要问题,负反馈还影响着放大器输入和输出阻抗,电压混合使输入阻抗增高,电流混合使输入阻抗降低; 电流取样使输出阻抗增高,电压取样使输出阻抗降低。利用负反馈还可大大减少放大器在稳定状态下所产生的失真,并可减弱放大器内部各种干扰电平。利用负反馈还可展宽放大器的频带,使得放大器的幅频特性变得比较平坦。因此,负反馈可大大提高放大器的放大质量,改善许多性能指标,而且反馈越深,改善的程度也愈大。

但过深的负反馈又可能引起放大器不能正常工作而导致自激。为了消除自激,通常会采用滞后补偿的方法,即在反馈环内的基本放大电路中插入一个含有电容C的电路,是得开环增益的相位滞后,达到稳定负反馈放大电路的目的。

本文详细解读了华为笔试中的电路理论、总线结构、加法器设计、FPGA开发工具、DMA访问协议、Verilog和VHDL语言基础、半导体器件稳压管、逻辑门技术(TTL和CMOS)以及负反馈原理等内容,涉及了IT技术的多个方面。

本文详细解读了华为笔试中的电路理论、总线结构、加法器设计、FPGA开发工具、DMA访问协议、Verilog和VHDL语言基础、半导体器件稳压管、逻辑门技术(TTL和CMOS)以及负反馈原理等内容,涉及了IT技术的多个方面。

980

980

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?