因为电脑之前一直蓝屏,然后重新装了Win10企业版系统,也重新安装了Vivado,在使用Vivado2018.3进行开发的时候,遇到了一个特别奇怪的报错。

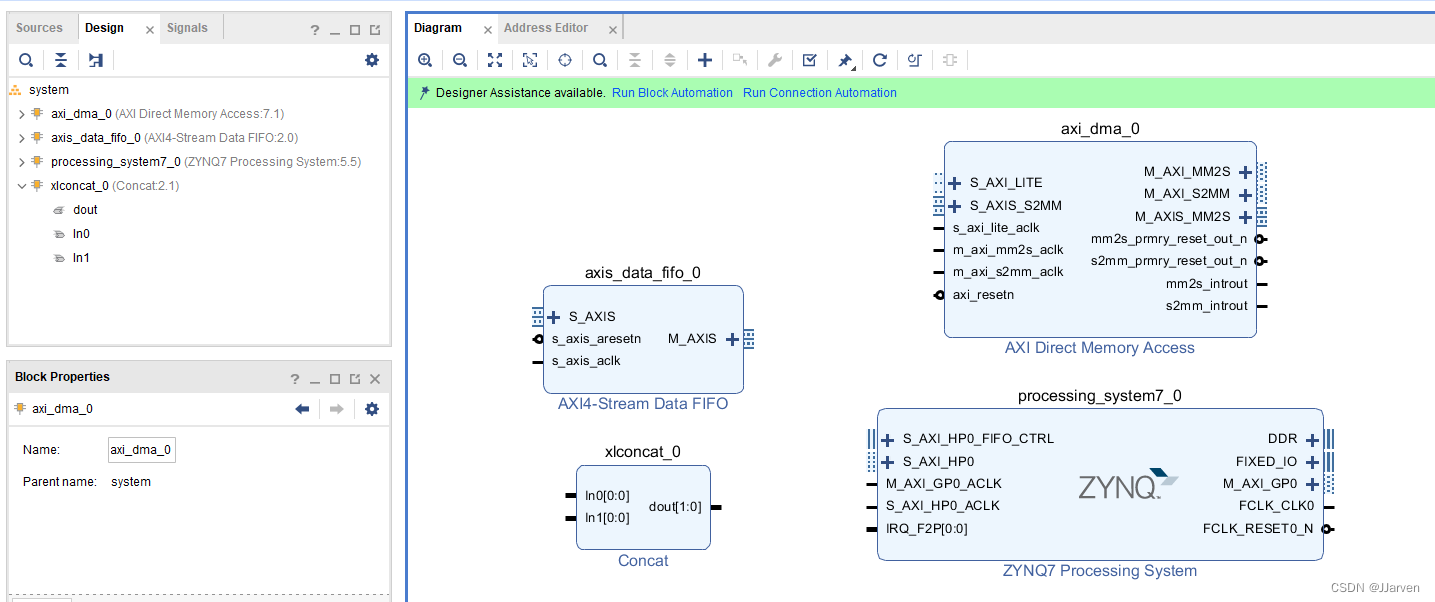

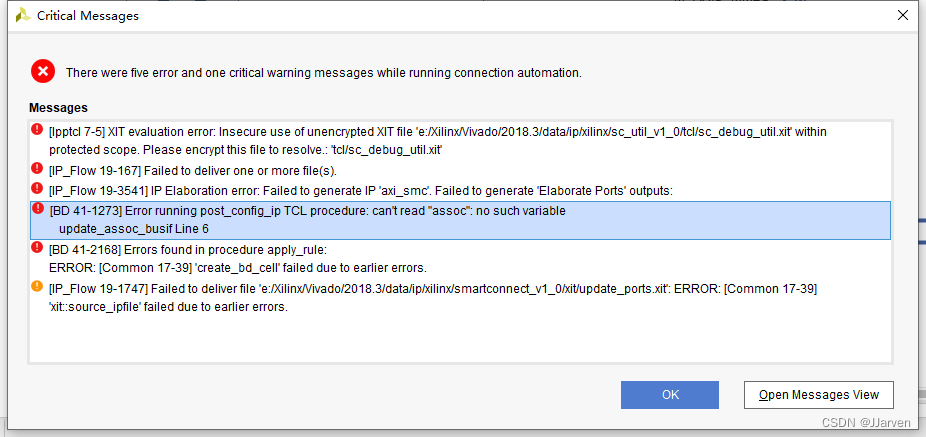

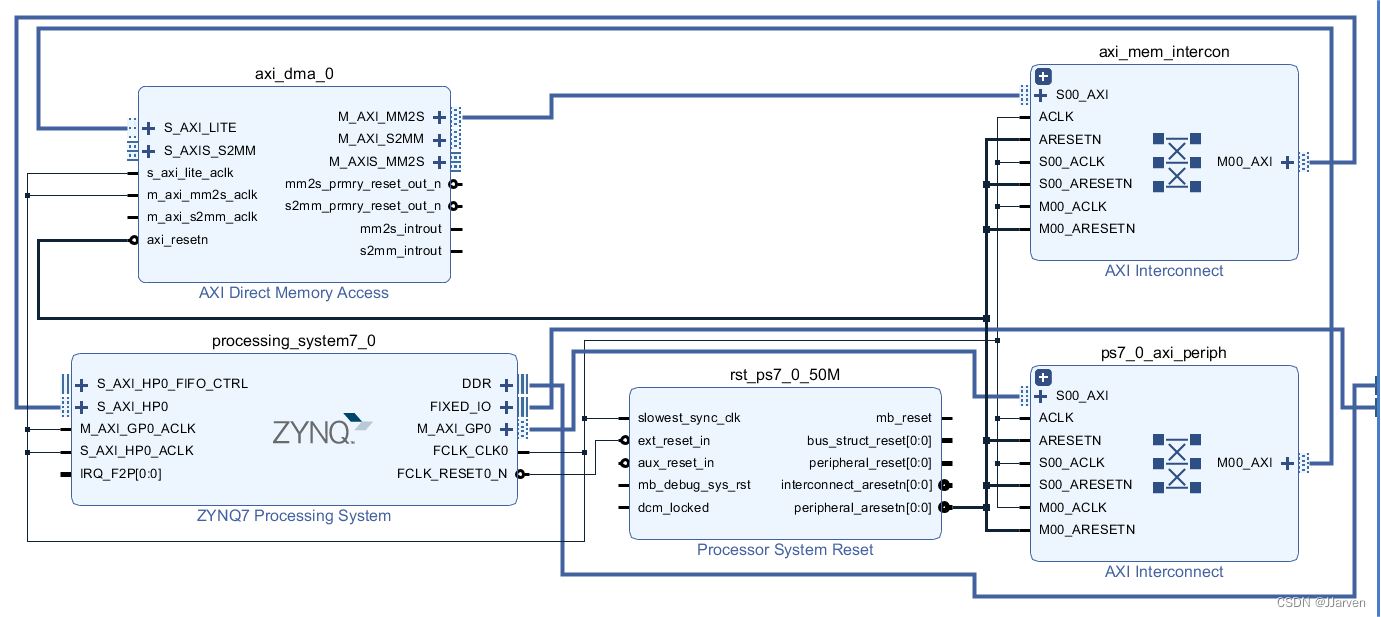

首先我新建了一个工程,然后进行Block Design,添加各种硬件系统需要的IP核(这里补充说明一下,在我的硬件系统中需要使用AXI接口、DDR3,所以这就避免不了数据的读写,也就是说在进行Block互联的时候,需要使用到S_AXI_HP接口)设计结束后点击AutoConnect,此时本来系统应该会自动在ZYNQ processing System IP核和AXI Direct Memory Access IP核之间添加SmartConnect连接器,但是系统只是添加了连接器,并没有将二者连接,并且报错

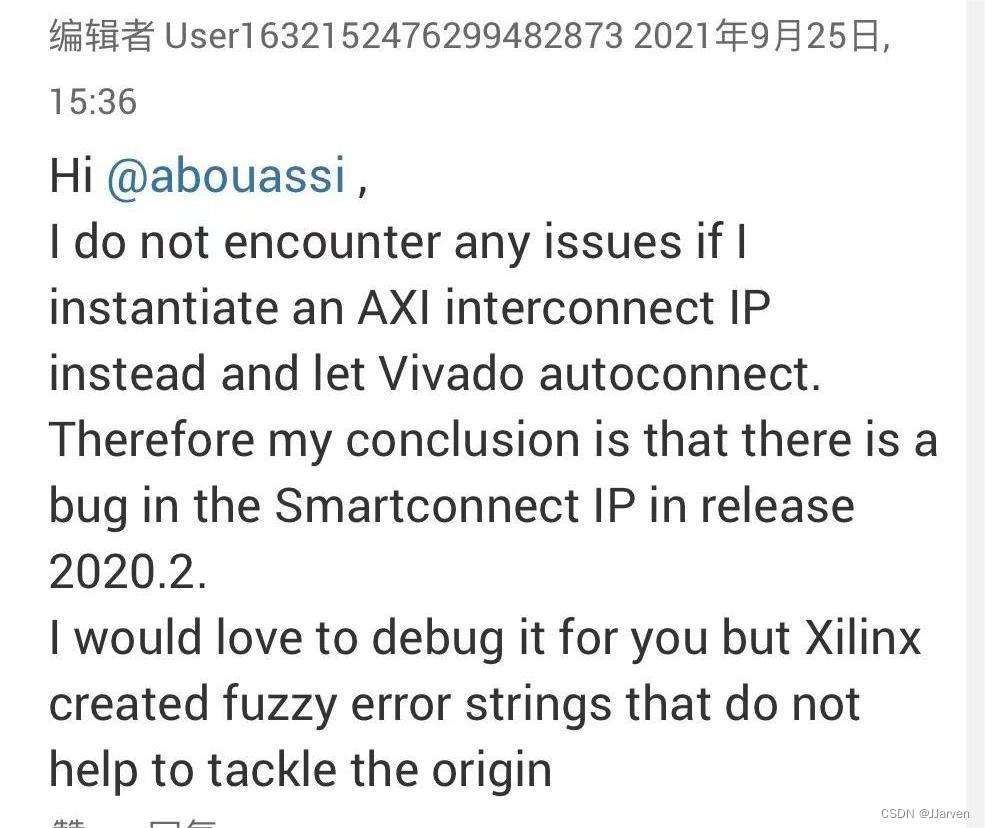

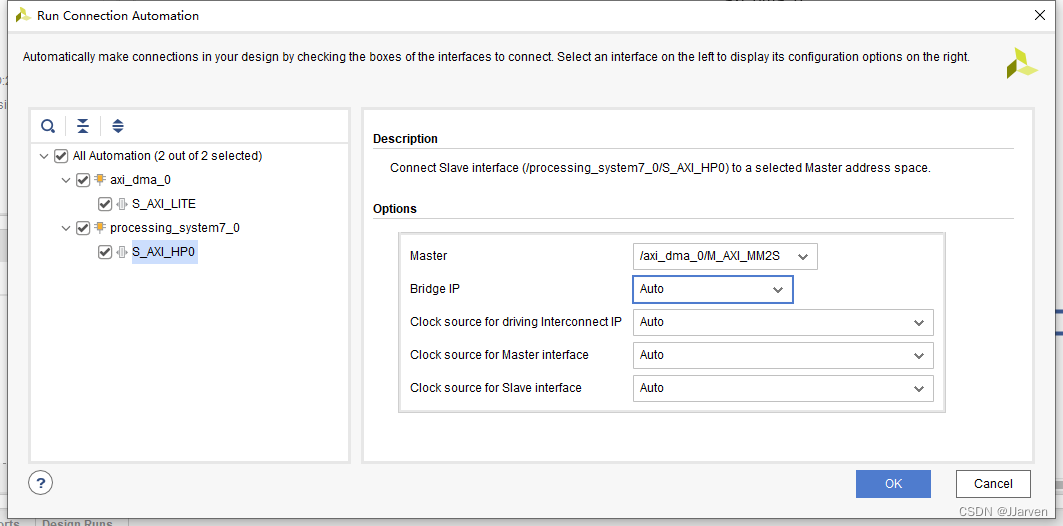

我在这里报错之后也问了大量的同行,都没有和我情况一样的,只能说是玄学,在FPGA这一行除了一些基础的错误,真的出现问题了很难找别人给你快速解决,因为有时候还有硬件方面的问题,所以我就上Xilinx Vivado论坛官网找相关的帖子,找到一个类似的问题,照着那个解决方法,解决了这个问题,具体方法看下面的图片。

将Auto模式改为InterConnect模式之后,系统自动就添加了InterConnect连接器,并且自动连接,AXI SmartConnect是AXI InterConnect的替代品,具有更高的性能,但是在这里使用InterConnect也没什么影响,所以我后面的设计过程也就没有太注意这个了。

2645

2645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?