板卡型号:xczu9eg-ffvb1156-2-e

Vivado版本:2019.1

做神经网络加速时PL侧需要完成指令接收,数据接收等操作;采用DDR4为片外存储器,在工程里使用BD创建DDR4 mig的IP核。主要是熟悉一下DDR4的IP核使用;

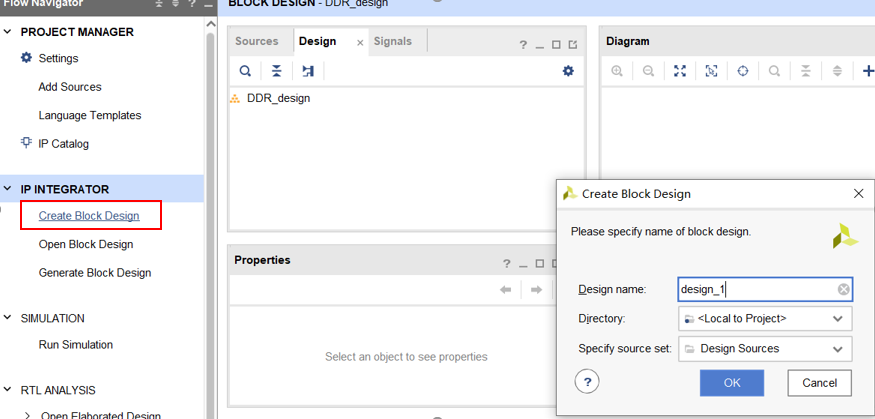

1、IP INTEFRATOR,Create Block Design新建一个BD文件

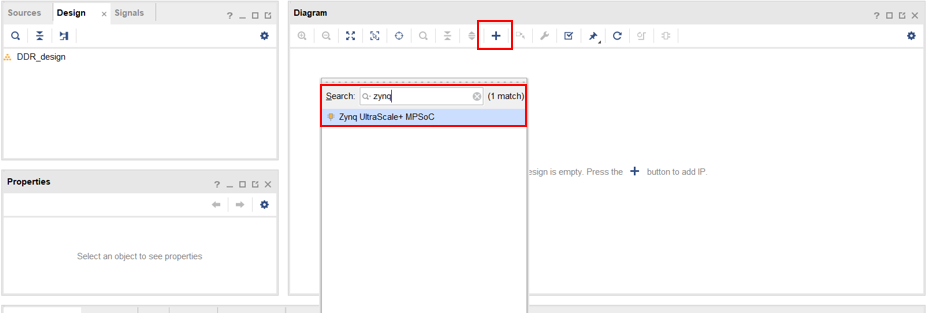

2、右侧Diagram界面中选择“+”添加IP核,搜索zynq添加Zynq UltraScale+ MPSoc

双击IP核进行设置,添加一组Master Interface;

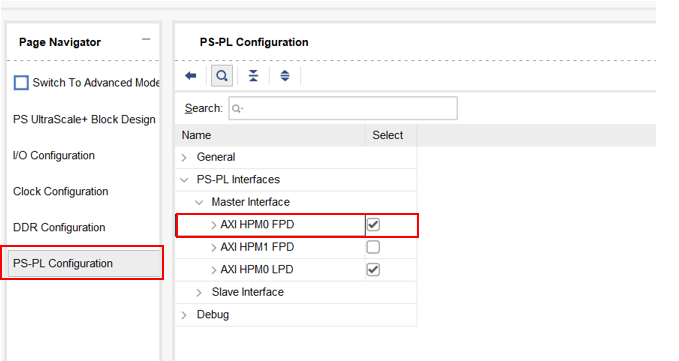

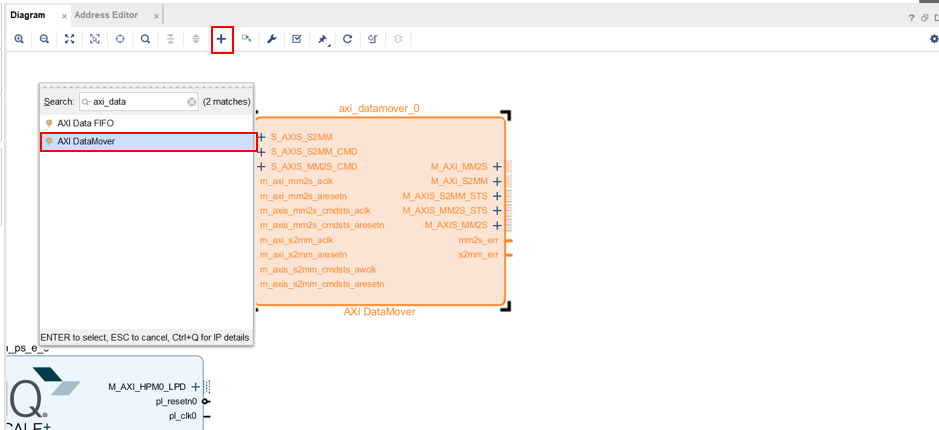

3、同步骤2再生成6个AXI DataMover分别控制bias、insrt、Ifm、scale、sfm、weight参数的数据;

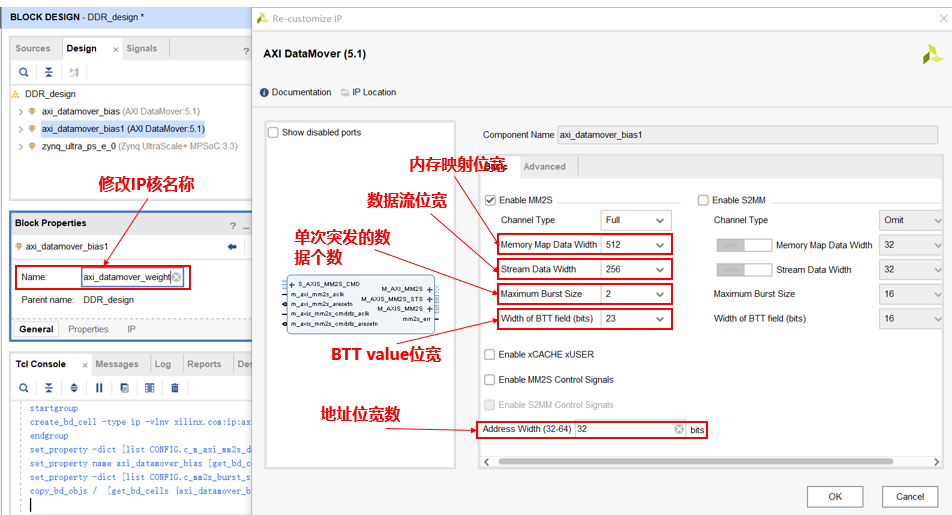

对axi_datamover ip核设置参数,具体操作界面如下,因为此处DataMover只用于读数据所以只勾选MM2S(内存映射到数据流),如果需要向DDR写数据则可以勾选S2MM:

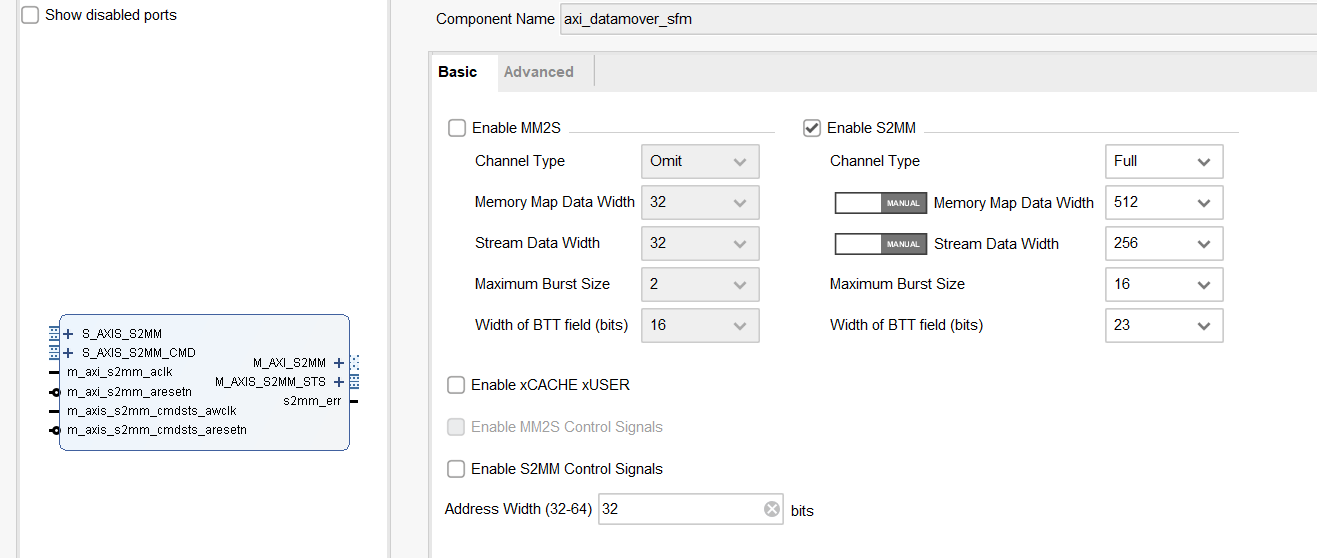

axi_datamover_sfm参数设置如下:

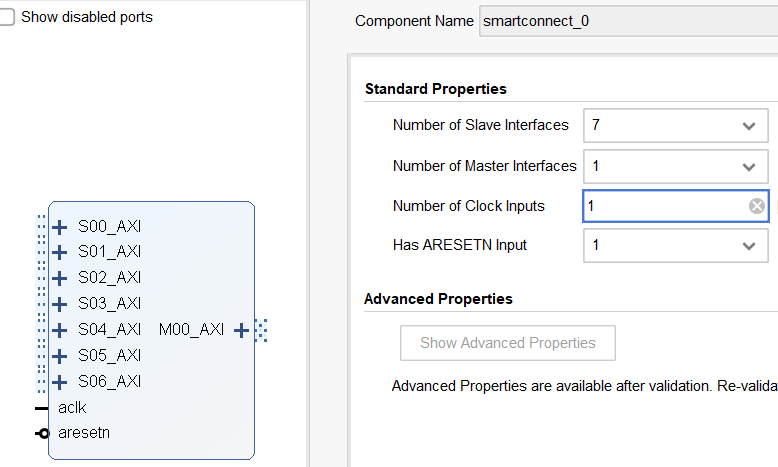

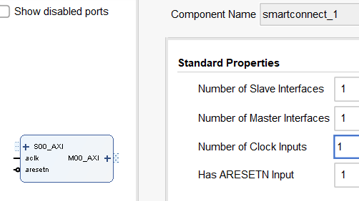

4、添加AXI SmartConnect IP核*2,设置如下参数

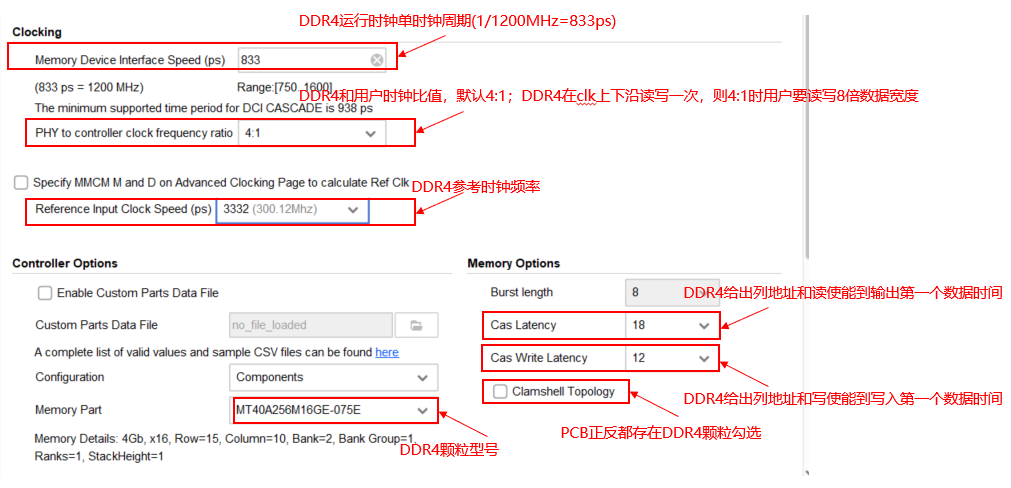

5、添加DDR4 SDRAM (MIG),根据具体DDR芯片参数设置

6、添加复位IP核Processor System Reset

至此PS侧的IP核全部添加完毕,下面把PL侧编写的CNN加速工程生成IP核导入原理图并连线;

7、创建自己的IP核

接下来需要将PL侧CNN推理加速的工程包装为IP核添加到BD的原理图中,需要创建自己的IP核。

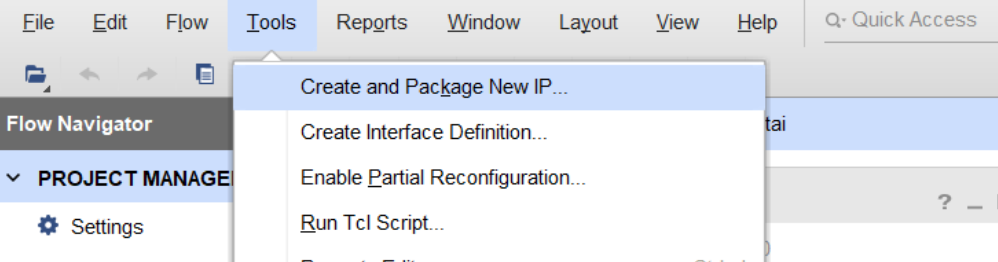

Tools——Create and Package New IP,建立一个IP核;

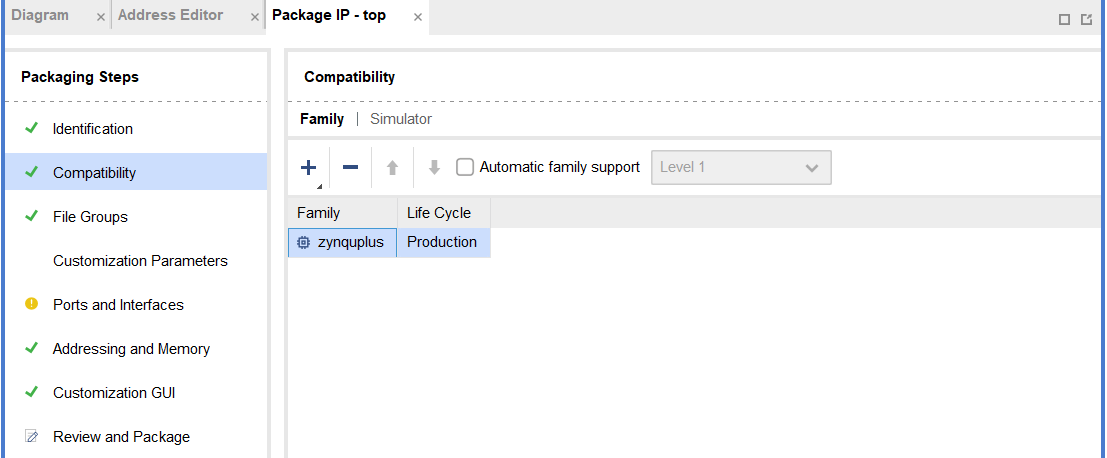

IP核适配的器件类型;

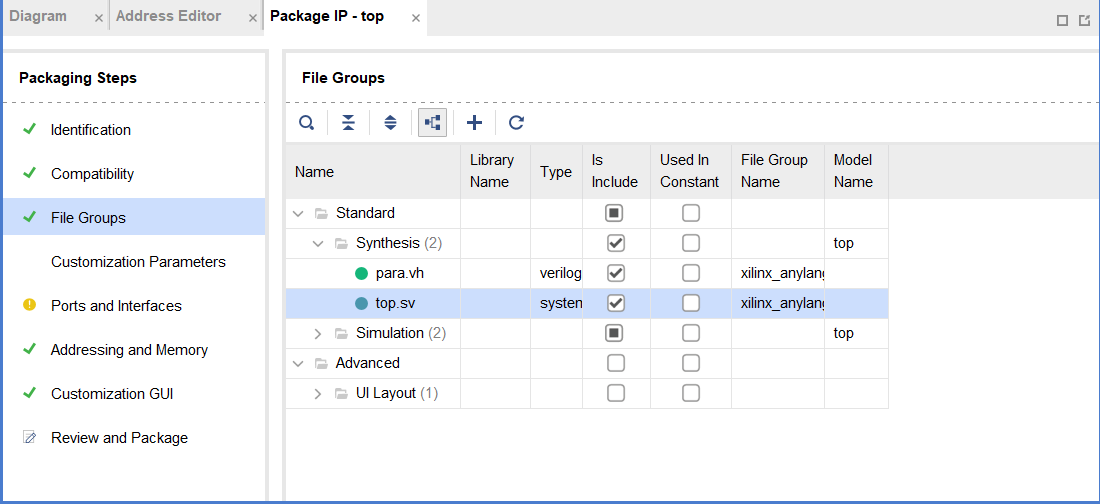

选择IP核关联的文件

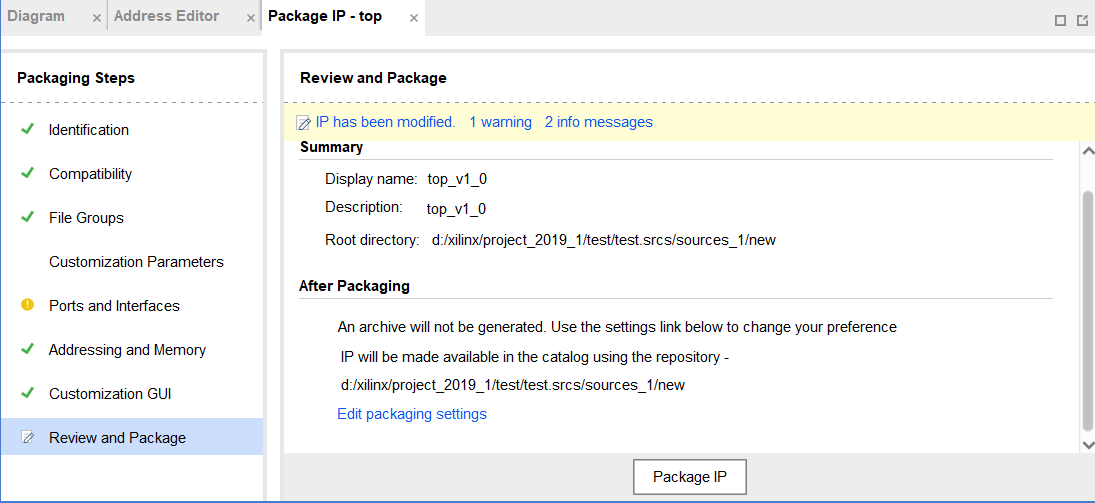

点击Package IP生成IP核

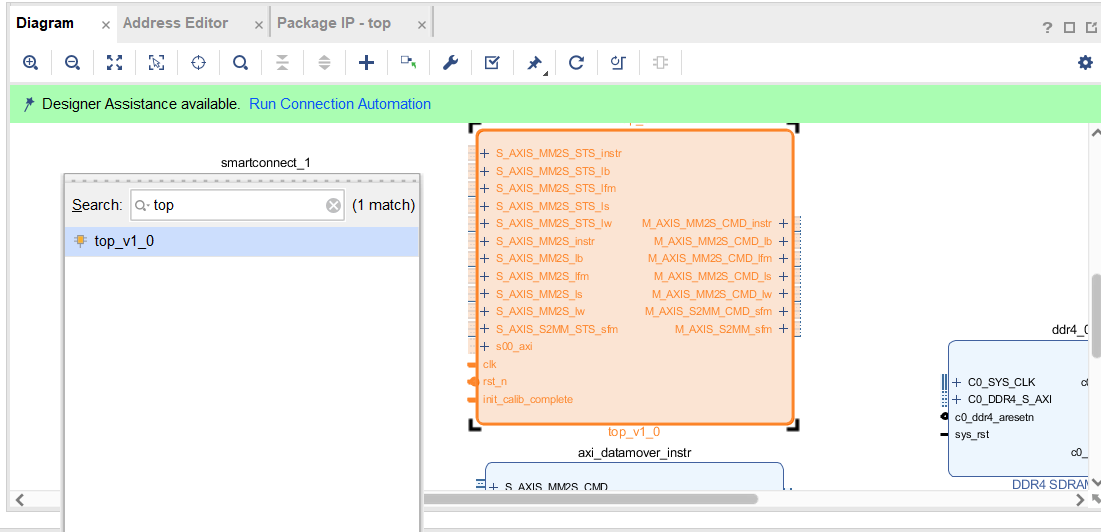

在原理图中添加自己的IP核top;

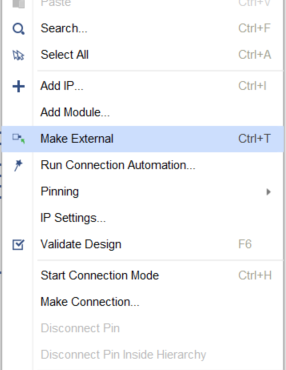

8、在DDR出把外部输入输出的端口创建出来(DDR CLK、DDR RESET、DDR)

右键DDR相关端口,选择Make External

9、完成连线

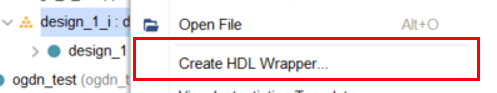

10、右键BD文件点击Create HDL Wrapper将原理图转化为RTL代码

本文介绍了如何在Vivado2019.1版本中使用XCZU9EGFPGA设计神经网络加速器,包括添加IP核(如ZynqUltraScale+MPSoc、AXIDataMover、AXISmartConnect和DDR4SDRAM),配置接口和参数,创建并包装自定义CNNIP,以及将外部端口外部化和生成HDL代码的过程。

本文介绍了如何在Vivado2019.1版本中使用XCZU9EGFPGA设计神经网络加速器,包括添加IP核(如ZynqUltraScale+MPSoc、AXIDataMover、AXISmartConnect和DDR4SDRAM),配置接口和参数,创建并包装自定义CNNIP,以及将外部端口外部化和生成HDL代码的过程。

1449

1449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?