如果您经常关注走线阻抗,但不习惯考虑过孔阻抗,那么本文适合您。或者,如果您正在关注过孔阻抗,但不确定什么尺寸会产生正确的阻抗,这也将有所帮助。那么,我什么时候应该使用 8 mil 钻头呢?

我为什么应该关心?

串行链路可能会因阻抗不匹配或不连续而失败。在实践中,不连续性造成的问题多于损失。虽然损失在某种程度上会使信号降级,并且可以通过均衡来补偿,但不连续性会导致更难驯服的反射。所以,修复不连续性,你就修复信号。在文章“将更高数据速率的串行链路投入生产 - 问题与解决方案”中,展示了通过纠正过孔阻抗实现400%眼睛改善的例子,但仅占互连的1%。1“New SI Techniques for Large System Performance Tuning” 中介绍了另一种改善过孔阻抗的方法,其由此产生的性能改进在硬件中测量。2

尽管过孔很小,但它们会显著影响性能。当 1/4 波长短截线悄悄进入系统时,这一点首先变得明显。A 过孔短线留在 1/4 英寸中。厚背板可以完全去除 12 Gbps 信号,近似值为 3/12(是的,只需使用 3 除以 Gbps 并得到英寸)。3虽然短截线可能是灾难性的,但随着数据速率的增加,过孔阻抗失配也越来越成问题。但是我们如何才能更好地理解过孔的阻抗呢?

进入 Via Modeling

几十年前,当我的 RF 朋友忙于研究奇特的过孔 3D 解决方案时,我们会在互连模型中的过孔位置放置一个 0.5 pF 的电容器,并称其为好。随着时间的推移,我们了解到将过孔建模为传输线是一种更好的方法。一些工具通过求解器快速实现4扩展了传输线概念以提供相关精度,如“快速、高效和准确:通过与 20 GHz 相关的模型”所述。5然而,即使您无法使用 Fast through 求解器,也可以直观地了解过孔阻抗,如此处所述。如果您想尝试 via 求解器,本文末尾提供了一个链接。

构建阻抗直觉

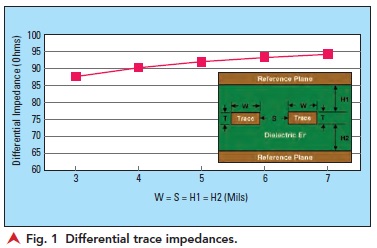

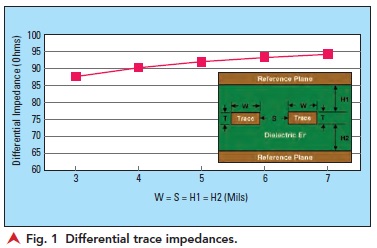

为了直观地了解什么过孔尺寸将产生我们想要的阻抗,让我们从

图 1 中所示的更熟悉的差分走线开始。事实上,过孔的行为有点像走线——尽管是在 Z 维度上。

图 1 显示了带状线走线阻抗与宽度、间距和到接地层的距离的关系(X 轴表示横截面图 W=S=H1=H2)。有趣的是,所有尺寸产生的阻抗都接近我们通常想要的阻抗,并且通过微小的调整来更精确地拨入该值。例如,增加一个或两个 H 值会使参考平面进一步远离,使走线更具电感性,从而提高阻抗 (Z=sqrt[L/C])。加宽走线 (W) 会使走线更具电容性,从而降低其阻抗。可视化这两个变化如何影响阻抗,因为我们即将将它们应用于过孔结构。

图 2 在 X 轴上绘制了差分过孔阻抗与常见钻孔尺寸的关系。焊盘尺寸为 drill+10 mils,圆形反焊盘尺寸为 drill+20 mils。间距为 1 mm,可在 BGA 下方或连接器附近找到。我们注意到的第一件事是,与走线阻抗范围相比,阻抗范围增加了 4× 以上

图 1.这种更宽的范围使通孔阻抗更难控制。与走线一样,我们可以更改过孔的结构以调整其阻抗。例如,加宽反焊盘或将它们连接成椭圆形“跑道”形状,会使参考平面进一步远离(如图 1 中增加走线 H),使通孔筒更具电感性,从而提高其阻抗。相反,增加钻头尺寸会加宽枪管(就像增加走线 W),使其更具电容性,从而降低其阻抗。

同样,通孔的挑战在于 4×+ 的阻抗范围与与走线相关的较窄范围相比——通过比较图 1 和图 2 可以清楚地看到。由于走线和过孔的结构调整具有相似的尺寸,因此它们对阻抗的影响也相似——在任一方向上可能是 5 Ω 或 10 Ω。因此,很难获得接近 100 Ω的 16 甚至 12 mil 过孔,因为它们的“自然”(即无结构修改)阻抗为 ~70 Ω。因此,8 mil 钻头在不太愿意转向 85Ω 阻抗的世界里越来越受欢迎就显而易见了——这是更常见的 10 mil 过孔的“自然”阻抗。

深入挖掘

您可能会反对我的概括,因为我没有说明我的介电常数 (Dk)。你是对的 — 它是 3.3。Dk 成比例地提高电容,因此对阻抗产生负影响。因此,我第一次用 Dk = 3.0 求解 10 mil 过孔时,我发现它们比预期的更接近 100 Ω。由于常见的 Dk 值变化为 50%(3.0 到 4.5),因此 Dk 确实是一个

重要的考虑因素。因此,当使用图 2 所示的差分阻抗时,如果 Dk 高于 3.3,则阻抗值会更低。同样,如果您的 Dk 低于 3.3,则您的阻抗会更高。例如,当 Dk 范围从 3.0 到 3.6 时,图 2 的阻抗变化± ~4 Ω。

我们还应该讨论 differential trace 和 through spacing。随着走线或过孔靠得更近,它们变得更具有电容性,因此阻抗会降低。虽然图 1 所示的走线阻抗可以通过分离走线增加 ~10 Ω,但随着过孔靠得更近,过孔阻抗将比图 2 所示的阻抗降低。 然而,由于它们相关的焊盘,过孔桶不能靠得更近 ~20 mils,因此很难将阻抗降低超过 ~5 Ω。

另外,请注意,当我们通过 28 Gbps NRZ 数据速率时,我们需要停止将过孔视为单个阻抗,而是将其视为其阻抗在焊盘处下降并在桶中上升的结构。在此数据速率下,这些单元在相关的特征大小范围内,因此将单独建模。6

结论

当您开始努力解决过孔阻抗问题时,会有更多的工具和测量可用于相同的工作,任务将会简化,就像走线一样。我的目标是为您提供一个参考点,使实现过孔阻抗的任务(从而消除过孔阻抗不连续性)变得不那么令人生畏。想要使用过孔尺寸试用自动求解器吗?下载 Signal Integrity Toolbox 免费试用版,其中包含过孔编辑器工具。7

*本文摘自 Donald Telian 的新书《Signal Integrity, In Practice》。面向硬件、SI、FPGA 和布局工程师的实用手册。可在亚马逊购买。

引用

1. D. Telian, S. Camerlo, K. Matta, et al. “将更高数据速率的串行链路投入生产 - 问题与解决方案”,DesignCon,2014年,第4页。

2. D. Telian、M. Steinberger、B. Katz,“用于大型系统性能调整的新 SI 技术”,DesignCon,2016 年,第 21 页。

3. D. Telian,“为 6 Gbps 及更高速率调整信号完整性工具和技术”,

SiGuys,CDNLive!,第 1-33 页,2007 年,第 5 页。

4. D. Telian、S. Camerlo、M. Steinberger 等人,“模拟具有数千个串行链路的大型系统”,DesignCon,2012 年,第 4 页。

5. M. Steinberger、D. Telian、E. Brock,“快速、高效和准确:通过与 20 GHz 相关的模型”,DesignCon,2013 年。

6. D. Telian,“哪些不连续性小到可以忽略?

信号完整性杂志 RSS,2022 年 4 月,

图 2。

1111

1111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?