前提:使用该方法进行debug的信号端口在模块中是可见的(即:顶层的输入输出信号)

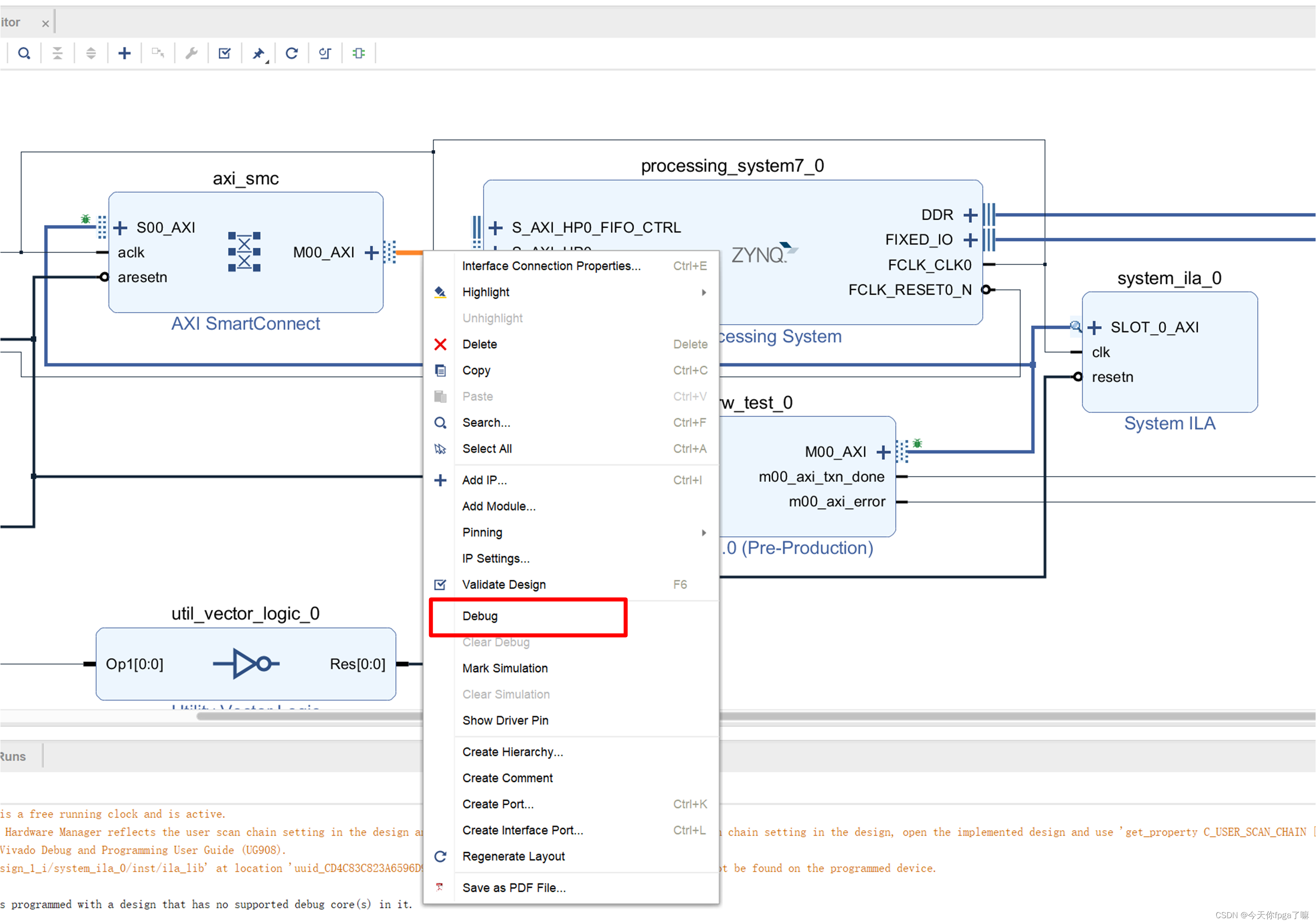

1.右键想要观察的信号,点击debug

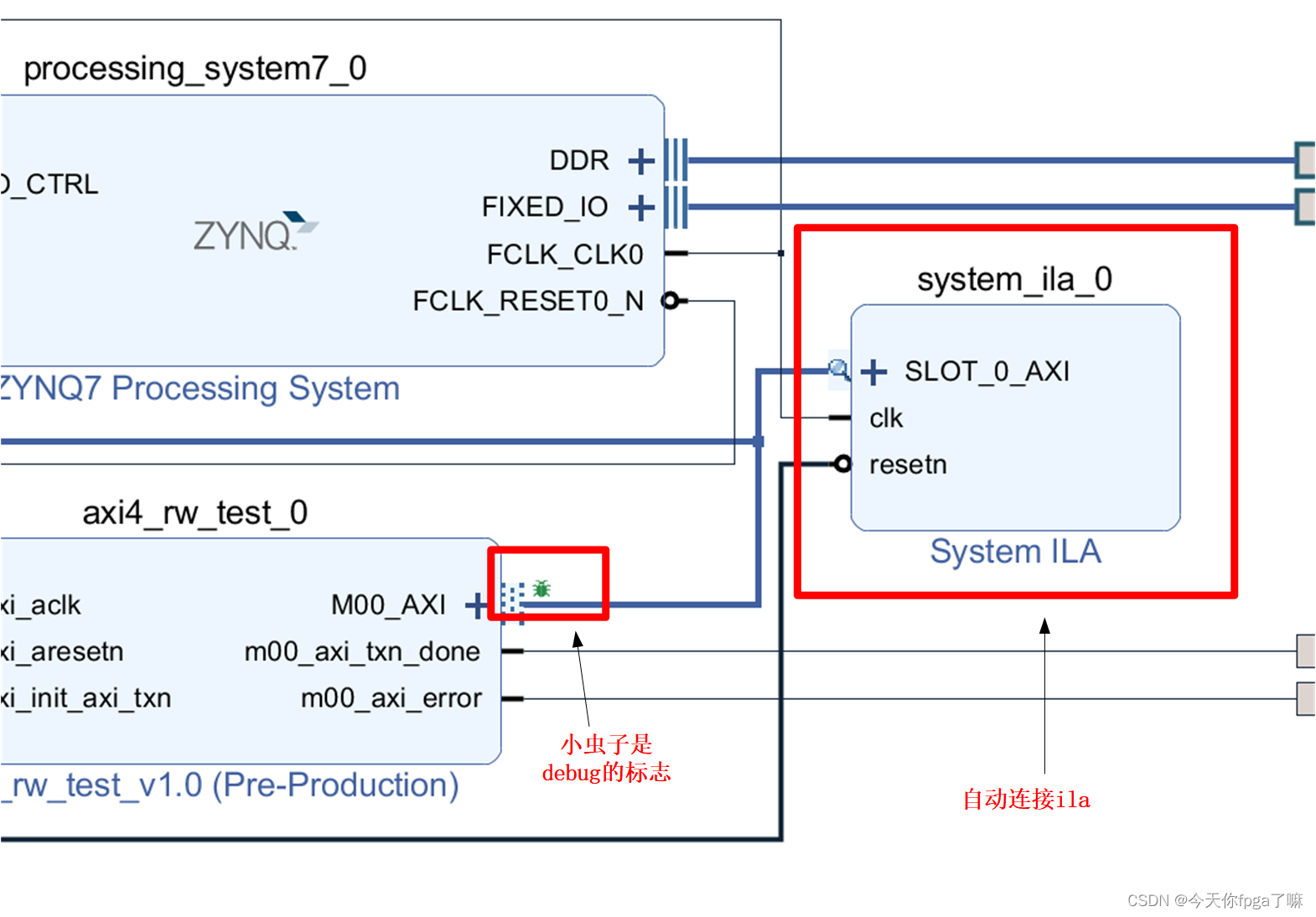

2.debug后会出现小虫标志,然后点击block design界面的自动连接,会自动连接ila(可设置观测信号深度)

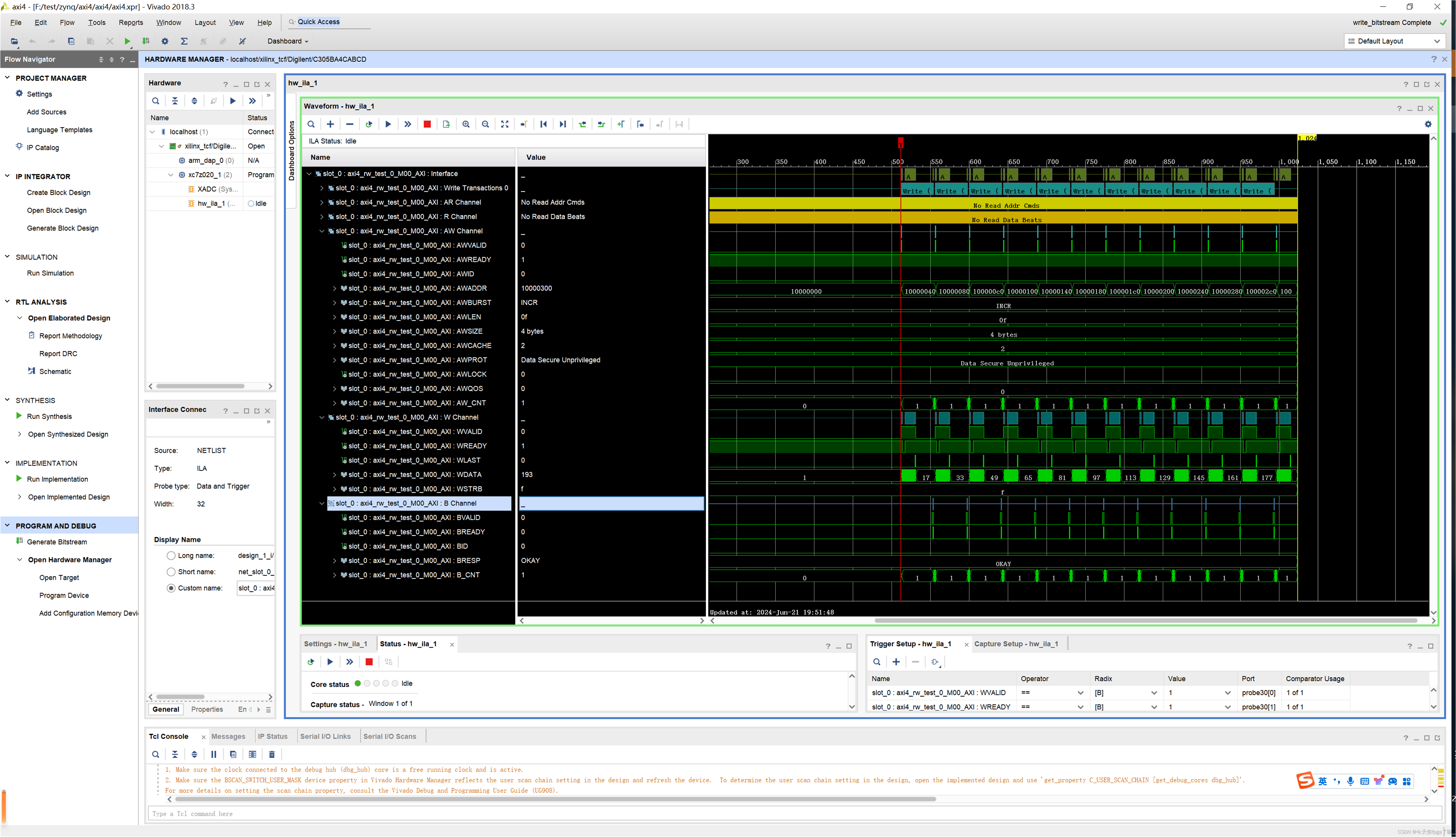

3.程序下载到板子后,会自动跳出ila界面,设置好触发条件即可观察波形。

07-23

5720

5720

5720

5720

09-06

2933

2933

2933

2933

05-13

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?