Vivado调试Debug使用总结

Vivado调试Debug使用总结

前言

提示:这里可以添加本文要记录的大概内容:

最近,工作不怎么忙碌,而且工程上遇到了关于ila在线调试时遇到识别不出时钟的问题,就看了一下Vivado的技术手册,发现了好多之前没有注意到的点,也对ila调试核有了新的认识,现在将这些关键的点记录下来,供大家参考,创作不易,希望大家多多关注和点赞,谢谢啦!!!

提示:以下是本篇文章正文内容,下面案例可供参考

一、调试ila创建分类

| 设置方式 | 调试目标 | 设置流程 |

|---|---|---|

| HDL代码添加 | 识别 HDL 源代码中的调试信号,同时保留稍后在流程中启用/禁用调试的灵活性。 | 使用 mark_debug 属性来标记要在 HDL 中进行调试的信号。使用“设置调试 (Set up Debug)”Wizard 来指导您完成“网表插入 (Netlist Insertion)”探测流程。 |

| 网表添加标记 | 识别已综合的设计网表中的调试信号线,无需修改 HDL 源代码。 | 使用“标记调试 (Mark Debug)”右键单击菜单选项从已综合的设计网表中选择要调试的信号线。使用“设置调试 (Set up Debug)”Wizard 来指导您完成“网表插入 (Netlist Insertion)”探测流程。 |

| Tcl窗口添加 | 使用 Tcl 命令自动执行调试探测流程。 | 使用 set_property Tcl 命令在调试信号线上设置 mark_debug 属性。使用“网表插入探测流程”的 Tcl 命令来创建调试核,并将其连接到调试信号线。 |

| 代码添加ila核 | 在 HDL 源中将信号显式连接到 ILA 调试核实例。 | 识别要调试的 HDL 信号。使用“HDL 例化探测流程”来生成并例化 Integrated Logic Analyzer (ILA) 核,并将其连接到设计中的调试信号。 |

以上4种ila核调试方式的加入方式就不在这里赘述了,如果有想详细了解的,可以去查ug908手册。

二、ILA 调试核属性

| 调试核属性 | 描述 | 可能的值 |

|---|---|---|

| C_DATA_DEPTH | ILA 核可存储的数据样本的最大数量。如果增大该值,则会在ILA 核中占用更多块 RAM,从而对设计性能产生不利影响。 | 1024(默认值)、2048、4096、8192、16384、32768、65536、131072 |

| C_TRIGIN_EN | 启用 ILA 核的 TRIG_IN 端口和 TRIG_IN_ACK 端口。请注意,您需要使用高级网表更改命令才能将这些端口连接到设计中的信号线。如果要使用 ILA 触发器输入或输出信号,请考虑使用将 ILA核添加到设计中的 HDL 例化方法。 | false(默认值)、true |

| C_TRIGOUT_EN | 启用 ILA 核的 TRIG_OUT 和 TRIG_OUT_ACK 端口。请注意,您需要使用高级网表更改命令才能将这些端口连接到设计中的信号线。如果要使用 ILA 触发器输入或输出信号,请考虑使用将 ILA核添加到设计中的 HDL 例化方法。 | false(默认值)、true |

| C_ADV_TRIGGER | 启用 ILA 核的高级触发器模式。请参阅“在硬件中调试逻辑设计”以获取有关此功能的详细信息。 | false(默认值)、true |

| C_MEMORY_TYPE(仅适用于 Versal) | 选择要用于 AXIS-ILA 走线存储器的存储器原语(BRAM 或UltraRAM)。UltraRAM 适用于块 RAM 利用率较高的设计。 | 0 (BRAM)、1 (URAM) |

| C_INPUT_PIPE_STAGES | 在 ILA 核的 PROBE 输入上启用额外的流水线阶段层级(例如,触发器寄存器)。您可使用此功能来支持 Vivado 工具将 ILA 核布局在远离设计关键部分的位置,从而提升设计的时序性能。 | 0(默认值)、1、2、3、4、5、6 |

| C_EN_STRG_QUAL | 启用 ILA 核的基本采集控制模式。 | false(默认值)、true |

| C_ALL_PROBE_SAME_MU | 启用 ILA 核的所有 PROBE 输入,使其包含相同数量的比较器(也称为“匹配单元”)。该属性应始终设置为 true。 | false(默认值)、true |

| C_ALL_PROBE_SAME_MU_CNT | ILA 核的每个 PROBE 输入的比较器(或匹配单元)数量。所需的比较器数量取决于 C_ADV_TRIGGER 和 C_EN_STRG_QUAL 属性的设置:如果 C_ADV_TRIGGER 为 false 且 C_EN_STRG_QUAL 为 false,则此项可设置为 1 到 16。如果 C_ADV_TRIGGER 为 false 且 C_EN_STRG_QUAL 为 true,则此项可设置为 2 到 16。如果 C_ADV_TRIGGER 为 true 且 C_EN_STRG_QUAL 为 false,则此项可设置为 1 到 16。如果 C_ADV_TRIGGER 为 true 且 C_EN_STRG_QUAL 为 true,则此项可设置为 2 到 16。重要:如不遵循上述规则,则将在实现期间生成 ILA 核时遇到错误。 | 1、2、3、4、5、6、7、8、9、10、11、12、13、14、15、16 |

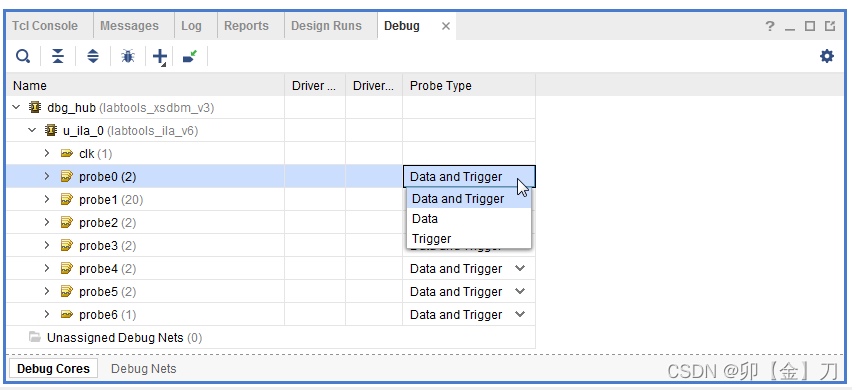

三、探针用作为数据和/或触发器

您可在 Vivado 硬件管理器中自定义探针,将其用作为数据和/或触发器。如果探针参与触发或采集比较值,则应将其配置为仅限“触发器”探针。这样即可最优化 ILA 核使用 BRAM 的方式。通常,如需采集探针数据,则应将其配置为仅限“数据”探针。如果探针同时参与触发比较值并且还需采集其数据,则应将其配置为“触发器和数据”。

对于包含配置为仅限“数据”的探针的设计,如果在运行时对其执行器件编程,则将无法使用这些探针来配置触发或采集设置条件。相反,在“Waveform”波形中,将无法使用配置为仅限“触发器”的探针。

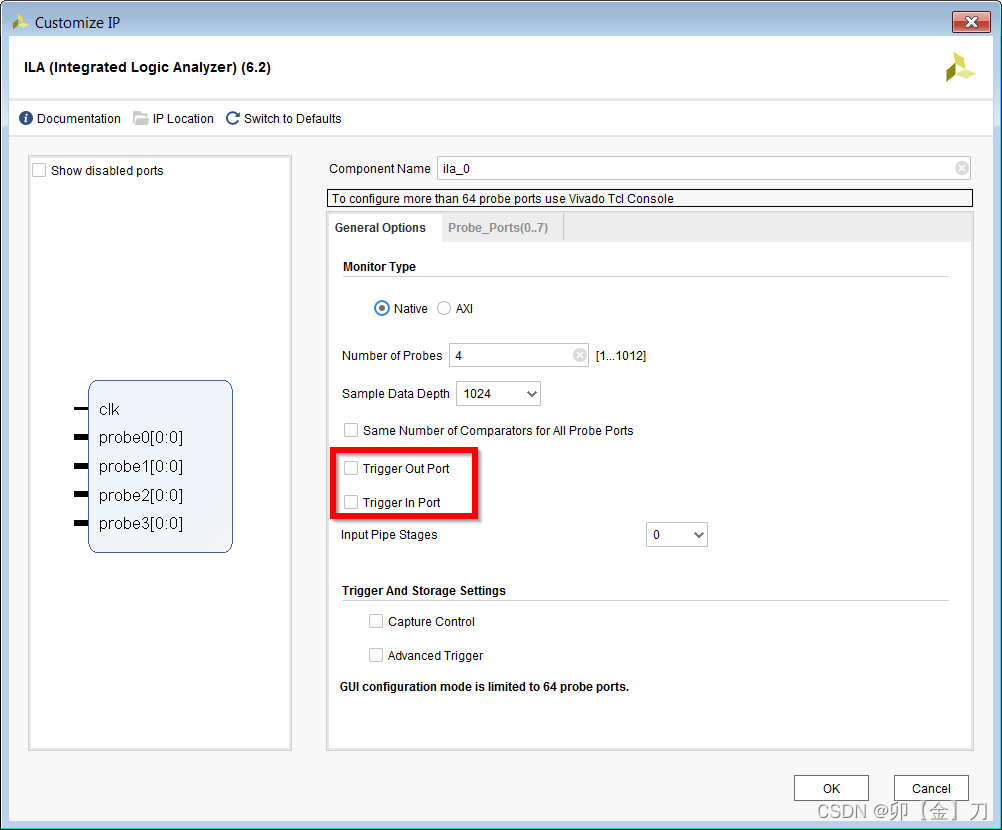

四、ILA 交叉触发

ILA 交叉触发功能支持在 ILA 核之间以及在 ILA 核与处理器(如 Zynq®-7000 SoC)之间进行交叉触发。如需在位于不同时钟域中的 2 个 ILA 核之间执行触发,或者要在处理器与 ILA 核之间执行硬件/软件交叉触发,可使用该功能。

要使用交叉触发功能,在核生成时,应配置 ILA 核心以使其包含专用触发器输入端口(TRIG_IN 和 TRIG_IN_ACK)和专用触发器输出端口(TRIG_OUT 和 TRIG_OUT_ACK)。如果要使用 ILA 触发器输入或输出信号,则必须使用将 ILA核添加到设计中的 HDL 例化方法。

TRIG_OUT_ACK 是 ILA 核(另一个 ILA、用户设计或处理器)的指示信号,表明已正确接收到 TRIG_OUT,它会导致ILA 在接收到 TRIG_OUT_ACK 时拉低 TRIG_OUT 信号。

换言之,TRIG_OUT 将保持高电平直至 TRIG_OUT_ACK 可用为止。如果 TRIG_OUT_ACK 信号绑定到低电平,那么RIG_OUT 将保持高电平,直至用户重新装备 ILA 为止。届时 TRIG_OUT 才会转至低电平。如果 TRIG_OUT_ACK 绑定到低电平,那么您可重新装备 ILA。

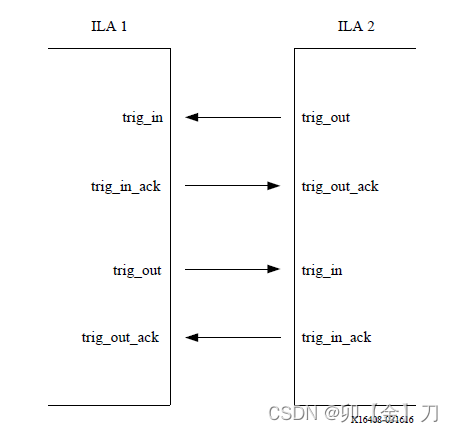

以下显示了典型的交叉触发设置,其中 ILA2 交叉触发到 ILA1 内。ILA2 的 TRIG_OUT 信号连接到 ILA1 的 TRIG_IN 信号。ILA1 的 TRIG_IN_ACK 信号则连接到 ILA2 的 TRIG_OUT_ACK 信号。

(ILA 2) trig_out -> (ILA 1) trig_in

(ILA 1) trig_in_ack -> (ILA 2) trig_out_ack

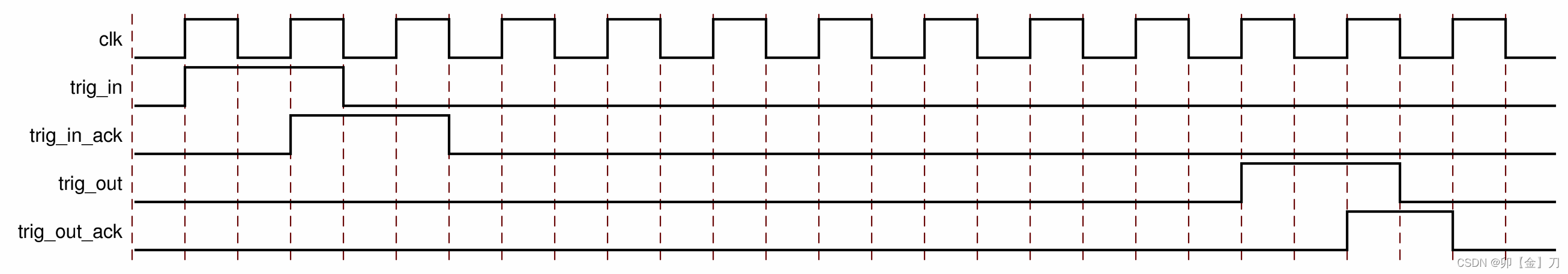

- 假定驱动 trig_in 端口的逻辑与 ILA clk 保持同步。

- 当 trig_in 断言有效后,trig_in_ack 信号需经过 1 个时钟周期后才能断言有效。

- 当使用 trig_in 或者满足触发条件后,trig_out 信号需经过 9 个时钟周期才能断言有效。

- 仅当触发器信号断言无效后,trig_in_ack 和 trig_out_ack 信号才会转至低电平。

五、ILA 核和时序考虑因素

请根据下列建议进行操作,以便最大程度减少对时序的影响:

-

List item

-

请审慎选择探针宽度。随探针宽度增加,对资源利用率和时序的影响也会增大。

-

请审慎选择 ILA 核数据深度。随数据深度增加,对块 RAM 资源利用率和时序的影响也会增大。

-

请确保为 ILA 核选择的时钟均为自由运行的时钟。否则可能造成在器件上加载设计时无法与调试核通信。

-

在添加调试核之前完成设计上的时序收敛。赛灵思不建议使用调试核调试相关时序问题。

-

请确保输入到 ILA 核的时钟与正在探测的信号同步。否则在设计编程到器件中时会产生时序问题并导致通信失败。

-

在硬件上运行设计之前请确保设计已满足时序要求。否则会导致结果不可靠。

-

对于非 Versal 架构:请确保提供给 dbg_hub 的时钟为自由运行的时钟。否则可能造成在器件上加载设计时无法与

调试核通信。可使用 connect_debug_port Tcl 命令将 Debug Hub 的 clk 管脚连接到自由运行的时钟。 -

对于非 Versal 架构:如果仍发现因添加 ILA 调试核而导致时序劣化,并且关键路径位于 dbg_hub 中,请执行以下

步骤:1. 打开已综合的设计。2. 找到网表中的 dbg_hub 单元。3. 转至 dbg_hub 的“Properties”选项卡。4. 找到 C_CLK_INPUT_FREQ_HZ 属性。5. 将其设置为连接到 dbg_hub 的时钟频率 (Hz)。6. 找到 C_ENABLE_CLK_DIVIDER 属性并将其启用。7. 重新执行设计实现。

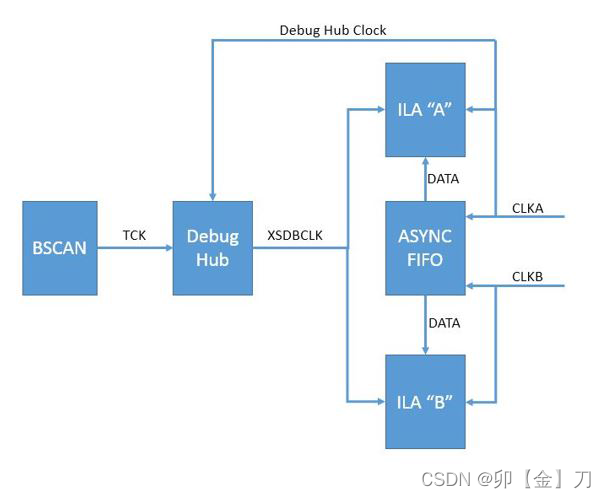

Debug Hub IP 用于桥接主机(通过支持串行接口的 BSCAN 原语)与芯片上的调试核(通过支持并行接口的 XSDB 接口)。BSCAN 原语时钟用于以串行方式将进出芯片的数据转换为 Debug Hub IP。Debug Hub IP 会收集数据,并使用Debug Hub 时钟将其发送至并行接口上的所有调试核,反之亦然。如有任一调试核时钟未自由运行或者不稳定,则将发生数据损坏,导致出现“Debug Cores not detected”消息。为了避免数据损坏,重要的是确保 JTAG 时钟和Debug Hub 时钟在调试核检测流程中保持稳定并自由运行。

- Debug Hub 时钟必须自由运行并保持稳定。赛灵思建议从已正确约束并且已满足时序的时钟驱动器来驱动时钟。

- 如果从 MMCM/PLL 驱动时钟,那么在执行任何调试核测量之前,请确保 MMCM/PLL LOCKED 信号处于高电

平。如果时钟连接到 Debug Hub 或任一调试核并且在调试操作中间 MMCM/PLL LOCKED 信号转换为 0,那么时

钟可能发生显著抖动,从而可能导致调试逻辑出现不可预测的行为。 - 为了检测调试核,请使用满足上述要求的核与捕获的数据来执行测量。所有关联的时钟都必须自由运行并保持稳

定。

下图提供了含 2 个 ILA 核的设计示例:

此设计示例包含 2 个 ILA 核:ILA“A”和 ILA“B”。

此调试网络的时钟设置拓扑结构如下所示。当设计编程到器件中之后,Vivado 硬件管理器会尝试在设计中发现存在的Debug Hub 核。而 Debug Hub 则会尝试发现并考量连接到自己的所有调试核。在此设计中,调试核为 ILA“A”和 ILA“B”。请注意,CLKA 同时驱动 ILA“A”和 Debug Hub 核。CLKB 则驱动 ILA“B”调试核。

连接到目标并进行器件编程时,JTAG clk 应处于活动状态。在“调试核发现阶段”,应有自由运行且保持稳定的时钟,用于驱动 Debug Hub 核,在此情况下,即 CLKA。在“调试核测量阶段”(即,涉及在调试核上获取/设置属性的任何操作),JTAG、Debug Hub 和调试核时钟应处于活动状态。如果要触发并采集 ILA“B”上的数据,那么 JTAG、Debug Hub (CLKA) 和调试核(CLKB) 时钟应自由运行并保持稳定。

六、ila核的窗口调试说明

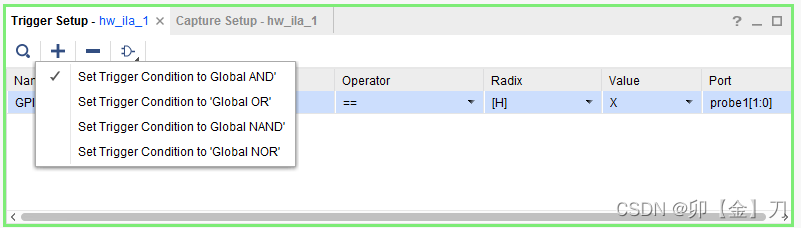

1、设置基本触发条件

下表中显示了 4 个可能的值的含义。

| GUI 中的触发条件设置 | CONTROL.TRIGGER_CONDITION 属性值 | 触发条件输出 |

|---|---|---|

| Global AND | AND | 如果所有参与的探针比较器求值结果均为“true”,那么触发条件为“true”,否则触发条件为“false”。 |

| Global OR | OR | 如果至少一个参与的探针比较器求值结果为“true”,那么触发条件为“true”,否则触发条件为“false”。 |

| Global NAND | NAND | 如果至少一个参与的探针比较器求值结果为“false”,那么触发条件为“true”,否则触发条件为“false”。 |

| Global NOR | NOR | 如果所有参与的探针比较器求值结果均为“false”,那么触发条件为“true”,否则触发条件为“false”。 |

2、设置采集窗口数量

ILA 采集数据缓存可分为 1 个或多个采集窗口。每个窗口的深度均为 2 次幂,它表示样本数且范围为 1 到 (((缓存大小) / (窗口数)) - 1)。例如,如果 ILA 数据缓存深度为 1024 个样本,且分为 4 个采集窗口,那么每个窗口深度最大为256 个样本。每个采集窗口都有各自独立的触发器掩码,对应于触发器事件,此类事件会导致填充采集窗口。

提示:这里对文章进行总结请在整个 ILA 数据采集缓存填满之前单击“停止触发器 (Stop Trigger)”,以上传并显示已填充的所有采集窗口。例如,如果 ILA 数据缓存分为 4 个窗口,其中 3 个已填充数据,那么单击“Stop Trigger”就会停止ILA 核,然后上传并显示 3 个已填充的采集窗口。

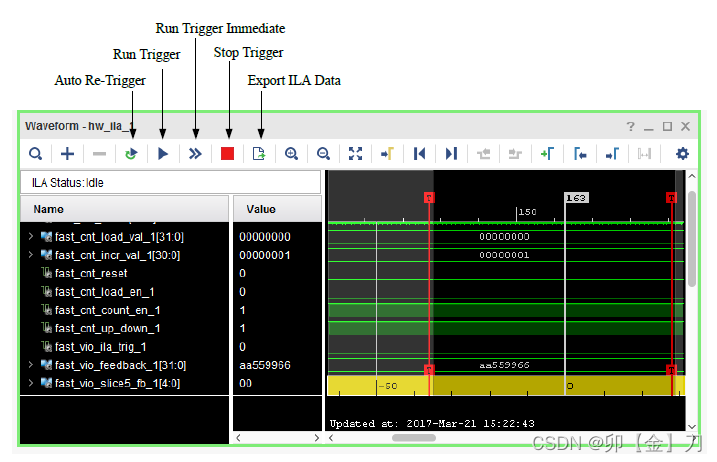

3、使用波形 ILA 触发器和导出功能

您可以使用波形窗口中的图标来装备 ILA 和运行触发器、停止触发器以及导出 ILA 数据,如下所示。

(1)将采集的 ILA 数据保存到文件

除了显示从 ILA 核直接上传的采集数据外,您也可以将采集输入写入文件,然后从文件读取该数据,并将其显示在波形查看器中。

将采集的 ILA 数据保存到文件当前将从 ILA 核采集的数据上传并保存到文件的唯一方法是使用以下 Tcl 命令:

write_hw_ila_data my_hw_ila_data_file.ila [upload_hw_ila_data hw_ila_1]

此 Tcl 命令序列会将从 ILA 核采集的数据上传并写入名为 my_hw_ila_data_file.ila 的存档文件。此存档文件包含波形数据库文件、波形配置文件、波形逗号分隔值文件以及调试探针文件。

(2)从文件恢复采集的 ILA 数据

当前,从文件恢复采集的数据并将其显示在波形查看器中的唯一方法是使用以下 Tcl 命令:

display_hw_ila_data [read_hw_ila_data my_hw_ila_data_file.ila]

此 Tcl 命令序列会读取先前从 ILA 核采集并保存的数据,然后将其显示在“波形 (Waveform)”窗口中。

注释:“ILA 数据波形 (ILA Data Waveform)”窗口的波形配置设置(分频器、标记、颜色、探针基数等)也同样保存在 ILA 采集数据归档文件中。恢复和显示先前保存的任意 ILA 数据时,会使用这些存储的波形配置设置。

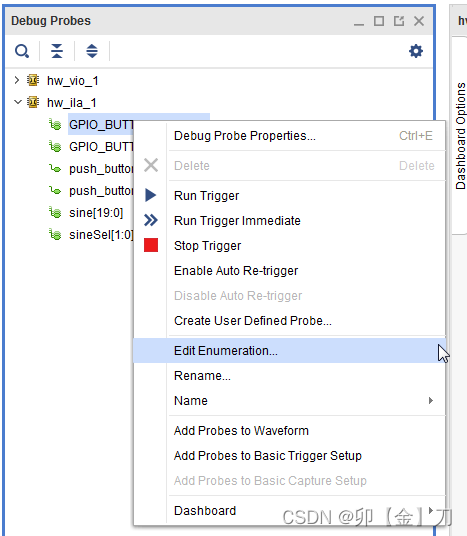

4、探针值枚举(状态机触发)

添加/编辑枚举。使用硬件管理器定义新的枚举。要将新的枚举名称/值对与调试探针相关联,请在“调试探针 (Debug Probes)”窗口或“触发/采集设置 (Trigger/Capture Setup)”窗口中右键单击调试探针,然后选中“Edit Enumeration”。

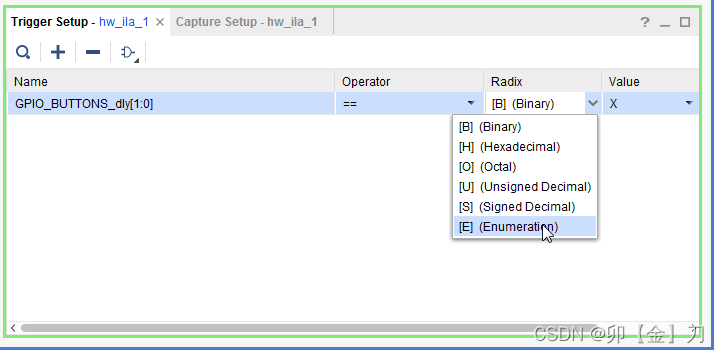

在“触发器设置”窗口中使用枚举

在“触发器设置 (Trigger Setup)”窗口中设置比较值,其语法与数字比较值类似。基数字符为“e”。针对枚举比较值,仅支持运算符“eq”和“neq”。

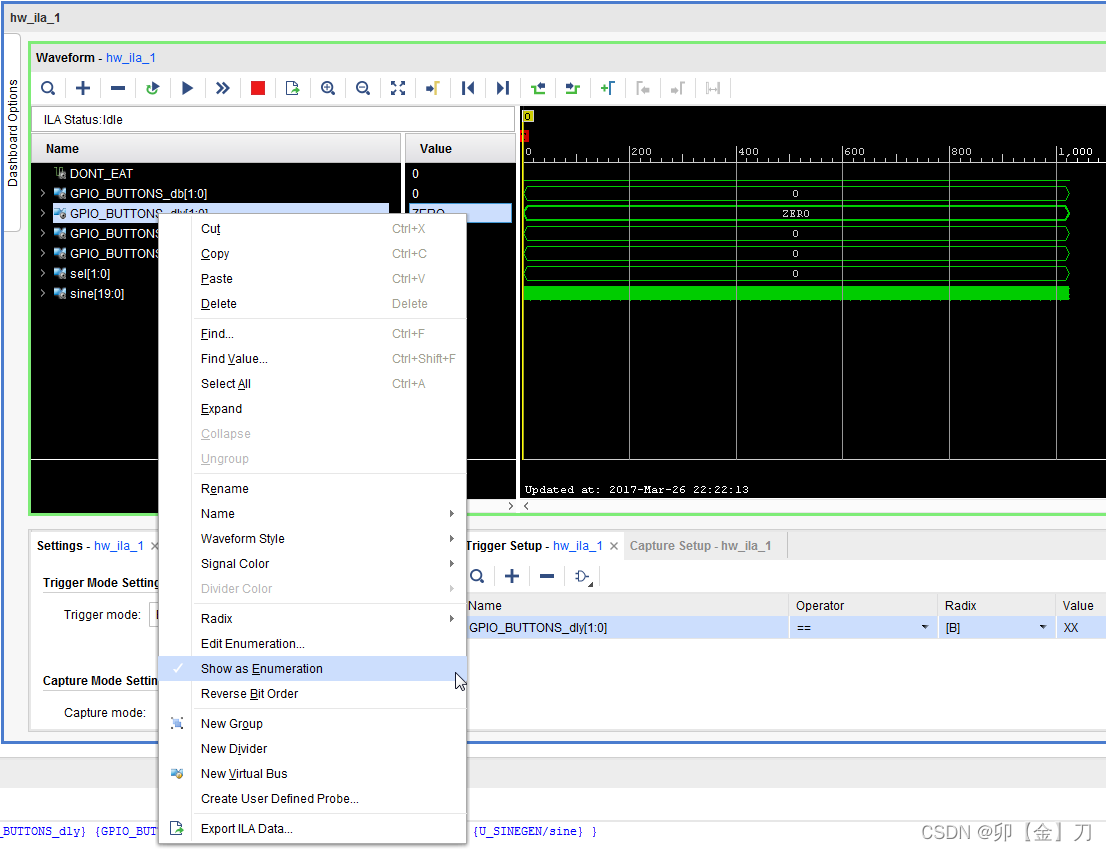

在波形窗口中使用枚举

您可在“波形 (Waveform)”窗口中针对每个信号选中“以枚举方式显示 (Show as Enumeration)”选项来显示枚举。在“波形 (Waveform)”窗口中右键单击信号,并从显示的菜单中选择“Show as Enumeration”。不以枚举方式显示时,总线值根据常规基数选择来显示。

总结

提示:这里对文章进行总结:

本文列举了一些调试中的技巧经验,希望对大家有所帮助,创作不易,感谢大家的阅读和点缀。

本文详细介绍了Vivado工具中ILA调试的核心概念,包括ILA核的创建、调试属性设置、探针功能应用、跨核触发、时序注意事项及窗口调试方法,旨在帮助工程师解决实际项目中的ILA调试问题。

本文详细介绍了Vivado工具中ILA调试的核心概念,包括ILA核的创建、调试属性设置、探针功能应用、跨核触发、时序注意事项及窗口调试方法,旨在帮助工程师解决实际项目中的ILA调试问题。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?