UVM基于功能将classes/utilities分为以下几大类:

Globals

在uvm_pkt的scope中定义了少量types、variables、functions和tasks。

相关文件:

- base/uvm_globals.svh

- base/uvm_object_globals.svh

Base

定义了搭建环境所需要的components、transactions、ports。

其中比较特殊的是uvm_root,它作为所有uvm_components的顶层,对所有uvm_components提供phasing的控制和其它全局的服务。

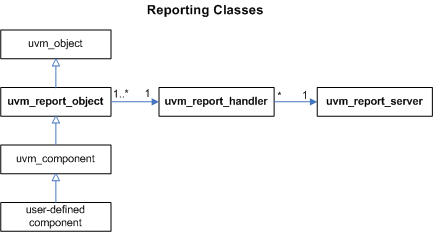

Reporting

为发布一致性的报告提供了工具。其中,uvm_report_hander根据verbosity的设定决定哪些报告可以送至uvm_report_server做进一步的格式处理。

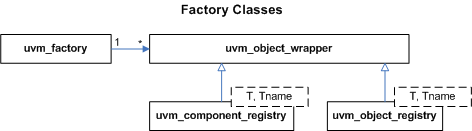

Factory

uvm_factory基于用户需求,创建objects和components。

Phasing

定义了uvm components中的phase机制,让uvm components能够按照一定顺序执行。

Configuration and Resources

Configuration and Resource类提供了一个可配置的数据库(database),用于存储和提取特定的数据。

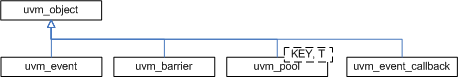

Synchronization

UVM提供了event and barrier synchronization类用于管理并发的进程。

其中,uvm_barrier用于防止仿真中进程无休止的增加下去。

Containers

Container类定义了参数化的数据结构,以实现比systemverilog更高效的数据共享:原因在于Container类之间的复制是基于reference的拷贝,而不是基于原始数据。

- uvm_queue #(T)和systemverilog中的queue类似;

- uvm_pool #(T)和systemverilog中的associative array类似。

Policies

为uvm_object-based objects的printing、comparing、recording、packing和unpacking函数制定策略(policy)。这些策略的实现与uvm_object的实现是分开的,因此你可以在不修改objects代码的情况下改变这些函数的行为。

- uvm_printer:提供了几个可供选择的子类用于指定打印策略:uvm_table_printer、uvm_tree_printer、uvm_line_printer,打印效果可以从名字中看出。

- uvm_comparer:基于该策略指定哪些数据需要compare以及如何报告miscompares。

- uvm_recorder:将uvm_object-based objects记录到transaction database中,这部分开放给EDA vendor实现。

- uvm_packer:用于指定pack和unpack的策略。

TLM

TLM library中定义了基于transaction级别的抽象接口用于简化uvm component之间的通信。

Components

uvm components是uvm中最重要的一部分,Components类将driver、scoreboard等进行了行为级的封装,便于我们继承和使用。

Sequencers

Sequencer作为一个仲裁者,为多个stimulus generators产生数据流提供了控制。

Sequence

Sequences将用户定义的多个数据包封装。这些sequences可以继续被重用、扩展、随机以及组合。uvm提供sequence的目的在于将仿真行为抽象级别提升。我们可以将DUT初始化数据、压力测试流、网络协议控制等封装为sequences,在接下来的验证活动中,基于这些sequences来编写测试用例,让编码更简便且更容易触发corner。

Macros

提供Macros的目的在于使验证活动更高效地开展。

Register Layer

当寄存器模型被正确建立后,Register Layer类可以帮助我们将总线操作抽象为对registers和memories的读写访问。

Command Line Processor

提供了对仿真参数的处理接口。

1071

1071

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?