电路的延迟特性分为惯性延迟和传输延迟,分别具有不同的物理意义。

参考:从仿真语义的角度看Verilog中延时、阻塞与非阻塞赋值

-----------------------------------------------------------------------------------------------------------------------------------------

延迟的添加方法有两种:内定延迟或者正规延迟

内定延迟:C = #2 A+B;(#号在里面)

正规延迟:#2 C = A+B;(#号在外面)

赋值的方法有三种:连续赋值、阻塞赋值和非阻塞赋值

理论的组合方式就有6种,但是连续赋值+内定延迟这种组合描述的电路存在记忆特性,不符合连续赋值意图,所以是非法的。

-----------------------------------------------------------------------------------------------------------------------------------------

根据上述行为,编写代码进行测试。

testcase

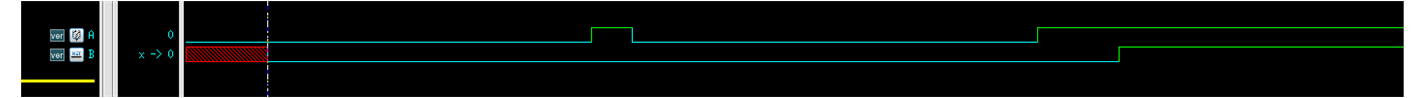

1、连续赋值中的延迟

正规延迟(B):任何小于延迟值的输入变化都会被滤除而不会体现在输出上(和后面的不计算有区别)。

内定延迟+连续赋值因为存在记忆效应,所以是非法的。

结论:用来描述电路的惯性延迟。

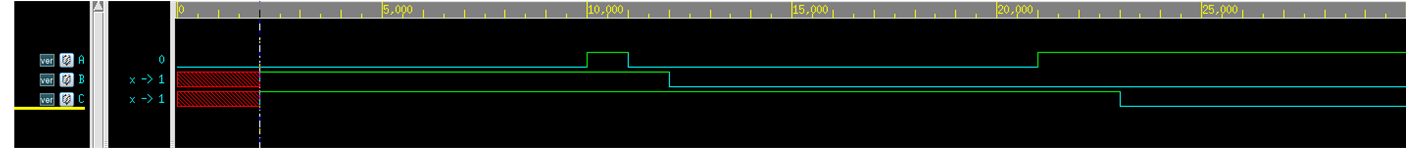

2、阻塞赋值中的延迟

内定延迟(B):always触发-计算-延迟-输出-等待再次触发。

正规延迟(C):always触发-延迟-计算-输出-等待再次触发。

缺点:忽略延迟时间段内的数据变化。

结论:既不能模拟惯性延迟、也不能模拟传输延迟。不建议在阻塞赋值中插入延迟。

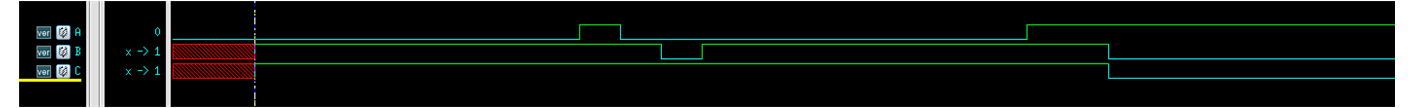

3、非阻塞赋值中的延迟

内定延迟(B):输入的变化延迟后会全部反应在输出上。

正规延迟(C):效果与阻塞赋值相同,会忽略延迟时间段内的数据变化。

结论:非阻塞赋值+内定延迟的方式可以描述传输延迟,这是过程赋值中唯一推荐的延迟描述。

1187

1187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?