一、什么是x态和z态

x态:表示Unknown,仿真发生了不能解决的逻辑冲突。

z态:表示HiZ、High Impedance、Tri-State、Disabled Driver。

——《Verilog编程艺术第7章》

二、仿真时为什么会产生x态和z态

产生x态原因之一:四态逻辑的默认初始值为x态,如果未对逻辑复位(reg或者ram),那么为x态;

产生x态原因之二:后仿真,时序违例后使用notifier将输出端口置为x态;

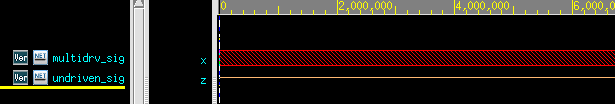

产生x态原因之三:线网信号存在多个驱动,多个驱动之间相互冲突;

产生x态原因只四:功能仿真时取数组值时index越界;

......

产生z态原因之一:综合把部分逻辑优化,导致网表中的输出端口无驱动。

......

example:

module dut ();

wire undriven_sig;

wire multidrv_sig;

logic a = 1; logic b=0;

assign multidrv_sig = a;

assign multidrv_sig = b;

endmodule

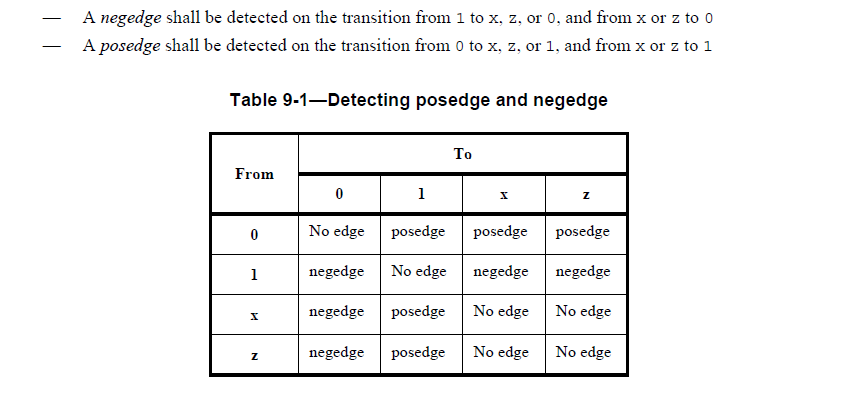

三、x/z态和posedge/negedge怎么关联

《IEEE Std 1364™-2005》

如上图,核心思想即把x态即当成0,又当成1;把z态即当成0,又当成1。

本文详细解释了Verilog中x态与z态的概念及其产生的原因,并通过实例展示了这两种状态的具体应用场景。此外,还探讨了x态与z态如何与posedge/negedge等时序控制关键字相关联。

本文详细解释了Verilog中x态与z态的概念及其产生的原因,并通过实例展示了这两种状态的具体应用场景。此外,还探讨了x态与z态如何与posedge/negedge等时序控制关键字相关联。

895

895

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?