在阅读《基于存算一体集成芯片的大模型专用硬件架构》论文后,对存算一体技术有了新的认识,梳理文章内容如下。本文分析了大模型在参数规模和系统算力需求上的指数级增长趋势,介绍了存算一体集成芯片的优势,包括缓解带宽瓶颈、实现高并行度数据流和多样化的存算一体技术分类。探讨了通过轻量化-存内压缩的协同设计,展示了存算一体架构在带宽需求、功耗和面积效率等方面的优势。总体而言,存算一体集成芯片为大模型的推理提供了一种高效、节能且具有潜力的硬件解决方案,供大家学习参考。

一、引言

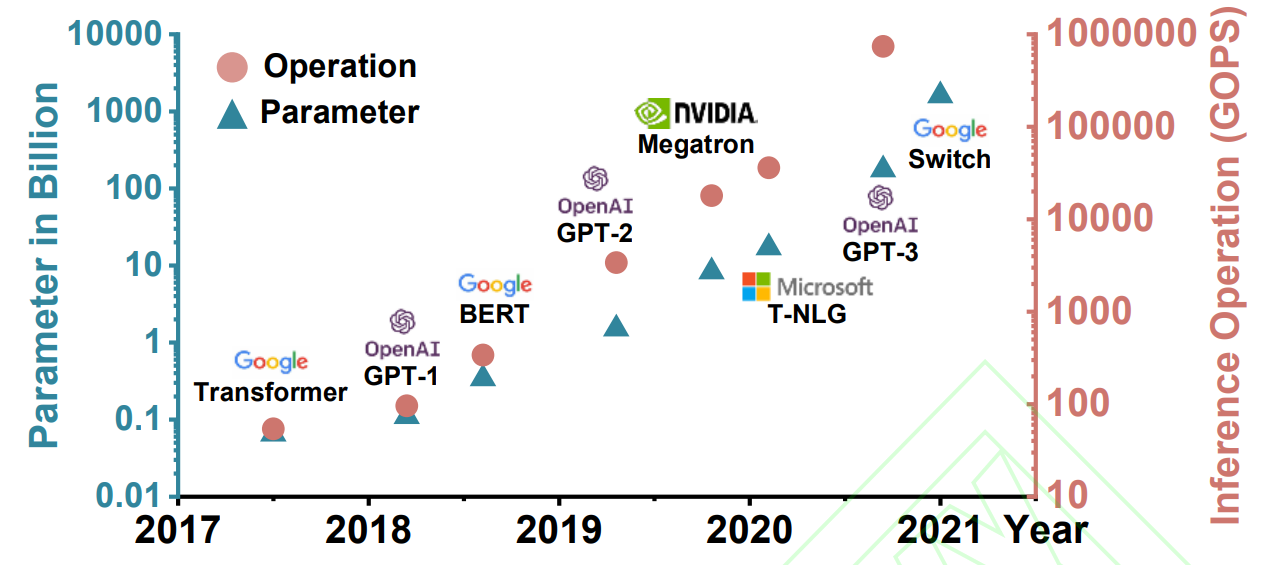

在当今人工智能领域,大模型如同一座座不断崛起的巨型灯塔,照亮了技术发展的新路径,但同时也给传统硬件架构带来了前所未有的挑战。以 ChatGPT 为代表的人工智能大模型,其参数规模和系统算力需求呈指数级迅猛增长。从模型尺寸来看,每两年便增长 240 倍,相应的算力需求更是近乎疯狂地增长近 750 倍。这种爆发式增长使得传统硬件架构逐渐不堪重负。

二、大模型对数据中心的挑战

(一)集成芯片技术

当前,能够支持大型模型的数据中心和超级计算机普遍采用以 xPU+主机内存缓冲器(HBM)集成芯片为核心的高性能处理器芯片系统。这些大算力芯片具备 P 级算力和 100 GB 级存储性能,例如 Nvidia H100 图形处理器(GPU)拥有 2 PFLOPS(每秒执行一千万亿浮点运算)的算力,AMD Instinct MI300 拥有 383 TFLOPS(每秒执行一兆浮点运算)的算力,华为昇腾 910 B 则具备 256 TFLOPS 算力等。然而,传统的超大规模和超大面积的单芯片 SoC 方案已经面临着诸多问题,包括利用率低、良率低、验证复杂度高以及设计成本激增等。同时,集成电路制造已经达到了光刻掩膜版的最大面积上限,而 30.48 cm(12 寸)晶圆的掩膜也在光刻机的要求下存在上限,最大芯片设计面积为 858 mm²。在这种背景下,单芯片 SoC 的算力进一步扩充空间受到限制,潜在的良率问题和面积限制使得算力的提升变得更加困难。自 2023 年起,美国进一步加强了针对中国芯片产业的出口限制,对总处理性能和算力密度超过规定的芯片实施了更加严格的管制。

为了缩小智能计算和处理器芯片技术上的差距,采用微纳架构工艺将多个芯片(粒)集成已经成为克服单芯片制造最大面积极限和芯片电路规模瓶颈的重要手段。不同于单芯片方案,集成芯片方案通过使用先进封装技术将多个小颗粒芯片组件组装在一起,实现了系统上的功能集成。这种方法将大型昂贵的 SoC 分解为更小、良率更高且更具成本效益的单芯片,同时也有助于缩短设计周期,降低成本。集成芯片技术已经成为高性能处理器的不可或缺的组成部分,而它正朝着 3D 多层堆叠、更多种类的芯片以及更大规模集成的方向发展。这一发展趋势的目标是进一步满足大型模型对硬件性能的不断增长的需求,适应日益增加的计算和处理任务。

(二)大模型部署的带宽瓶颈

以下图展示的拥有 70 亿参数的大型模型(LLAMa2-7B)为例,该大型模型的每一层多头注意力都包括多个连续前馈(FCL)计算。与此相关的单层参数量达到 2.03 亿,而 32 层的参数总量达到 65 亿,占用整体系数和计算的 85%以上,远超过单一互补金属氧化物半导体(CMOS)芯片的片上存储空间。注意力模块的计算存储要求则相对较低,CPU/中等性能网络处理器(NPU)即可完成。在大型模型推理中,如果要满足每秒 1 万个令牌的实时要求,即令牌速率为 10 000 个/秒,对 GPU 的带宽需求将达到 64 Tbit/s,而当前的 HBM3 带宽仅为 0.8 Tbit/s。因此,对于十亿级以上规模的大型模型网络应用场景,现有的 GPU/TPU+DRAM 分离计算架构难以满足不断增长的模型参数传输带宽需求。

这种情况表明,随着大型模型的不断发展和应用场景的扩大,现有的硬件架构在满足大规模模型计算需求方面面临着巨大的挑战。具体而言,参数量巨大且算力要求高的大模型导致了计算和存储资源高需求的问题,而当前的 GPU/TPU+DRAM 结构的带宽限制使得数据传输方面的瓶颈日益显现。因此,未来的硬件设计和架构需不断创新,以适应快速增长的大型模型计算需求,提供更高效的数据传输和处理解决方案。

三、存算一体集成芯片的优势

(一)缓解带宽瓶颈

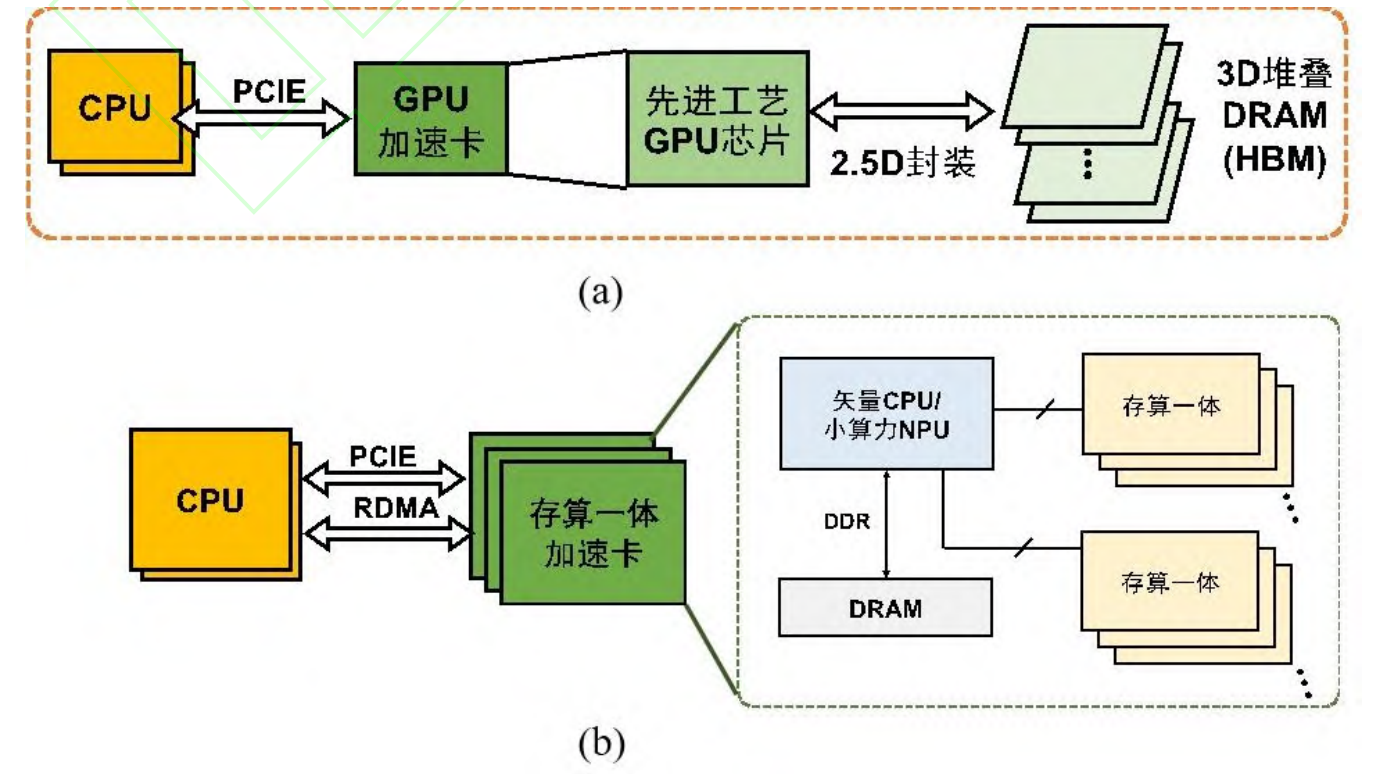

经典存算一体的设计基于交叉阵列。根据欧姆定律和基尔霍夫定律,输入特征用存储阵列的字线上的电压表示,输出特征会表示为位线上的电流大小,因此能够一次性完成矩阵乘加操作。同时,由于在计算过程中仅进行输入输出的搬运,权重系数一直固定在存储阵列中,所以能够显著减少数据搬移开销。我们发现,如果采用 CPU+存算一体的组合的架构,相较于现有的 GPU/TPU + DRAM 分离计算架构(如下图 所示),能够在相同的令牌速率和算力下,实现带宽的显著节约,达到 xPU+HBM 架构下 1 000+倍的水平。举例来说,当采用和第 1 节相同的令牌速率(10 000 个/秒)时,存算一体架构仅需 32~64 Gbit/s 的带宽,就能节省超过 1 000 倍的带宽。

另一方面,当单颗芯粒的算力达 10 TOPS,存储容量达到 200 MB 时,根据 12/14 nm 工艺估算,芯粒的计算电路面积约为 8 mm²,存储面积约为 300 mm²,此时实际的算力密度大约为 0.0325 TOPS/mm²。因此,存算一体集成芯片架构相对于传统的数据中心系统不仅在性能上取得了显著的提升,同时在所需的单芯粒接口速度远低于现有管控指标的前提下,为大规模模型的计算提供了更为可行的解决方案。

(二)存边架构高并行度数据流

以上图所示 LLAMa 模型为例,我们对大模型全连接层算力和存储容量进行分析,其三层连续的全连接层网络的算力需求为:(4 096×11 008 + 11 008×4 096 + 4 096×4 096)×32×10 k ×2 ≈ 68 TOP 存储容量为:(4 096×11 008 + 11 008×4 096 + 4 096×4 096)×32 ≈ 3.4 GB,即模型的算力需求与存储容量的比值为目标令牌速率,与网络大小无关。在数据中心中,令牌速率约为 1~10 000 个/秒,经典的卷积神经网络模型 ResNet-50 的算力与存储比为 4.1×帧率 GOPS/25 MB = 164×帧率(GOPS/kB)),因此大模型的算力存储比远低于以卷积神经网络(CNN)为主的传统深度神经网络(DNN)模型的算力存储比。传统交叉阵列架构算力存储比为时钟频率×2。为适应大模型的算力存储比,我们提出了存边计算架构(COMB),即将乘加计算逻辑分布在片上权重缓冲静态随机存储器(SRAM)的边缘,算力存储比为时钟频率×2/存储深度。近存计算架构中广泛使用的数据流映射方法完全可以运用在存边计算架构中,权重在计算开始前预先加载在 COMB 宏中,权重沿输入通道方向切块后,可以展平存入 COMB 宏的不同列。同时我们可以利用多个 COMB Marco 电路提高输出通道方向的并行度,完成空间并行计算。

(三)存算一体技术分类

目前业界已有一些存储颗粒形态的存边计算商业实现方案。其中,包括海力士(SK Hynix)提出的 AiM。AiM 的每颗 DRAM 芯粒含有 0.5 GB 的存储和 512 GFLOPS 的算力;三星提出的 LPDDR5+存内计算(PIM)颗粒的峰值算力可达 102.4 GFLOPS,与 NPU 相比,该设计提升了 4.5 倍的算力,并节省了 72%的功耗。然而,高密度 DRAM 的工艺专用性强,与 CMOS 逻辑制造工艺的兼容性较差,且受制于读破坏和电荷泄漏,需要定期刷新存储。

传统嵌入式存储介质 SRAM 工艺下的微缩比例远低于逻辑微缩比例。考虑到光刻极限,单芯片的最大 SRAM 在 100 MB 量级,且难以发生剧变。因此在过去,集成度一直限制了 SRAM 存算一体的发展。但随着 2.5D/3D 堆叠技术的发展,代工厂有望在 SRAM 上实现更高的集成密度,实现投影面积上等效晶体管密度的提升。如图 5 所示,我们基于集成扇出(FanOut)工艺,将 4 颗 65 nm SRAM 存边计算芯粒集成为一体,实现了 SRAM 存边计算架构算力和存储容量的显著提升。对于超过 4 颗芯粒集成的情况,映射方法尚需优化以实现算力随着芯粒数量的线性增长。除此之外,另一种存储颗粒形态的存边计算实现方案是阻变存储器(RRAM)。RRAM 是一种能够通过改变二端器件的阻值来存储信息的技术,具有与 CMOS 工艺兼容性高、非易失、低读取功耗等特点。基于 1TnR 的 RRAM 存储器阵列通过三维堆叠技术,能够实现接近 DRAM 的高密度存储。这一技术趋势为存算一体提供了更为灵活和高效的解决方案。

四、轻量化-存内压缩的协同设计

(一)稀疏网络在存算一体上的部署挑战

随着参数和算力需求的不断增加,大型模型网络的存算一体架构的部署面临更多的压力。稀疏技术为这一问题提供了一种软硬件协同设计的解决方案。首先,通过对大型模型网络的全连接层进行权重修剪,能够显著减少在生成查询、键和值矩阵时的参数存储需求。其次,大型模型网络所特有的注意力稀疏性进一步减少了自我注意机制的计算和存储需求。然而,在加速稀疏模型的存算一体架构中,仍然存在一些问题。传统的存算一体架构通常以一个交叉杆的形式组织来支持阵列级的计算并行性。在将非结构化剪枝的权重矩阵映射到交叉杆时,存储单元仍然需要保留零值权重,以维持计算的同步性。相较之下,结构化剪枝技术与并行处理更为兼容,但这会降低网络准确性。为了应对这些挑战,我们提出了一种存内稠密权重系数存储方案和基于蝶形网络的存算一体稀疏提取的激活拓扑网络。

(二)存内稠密权重系数存储

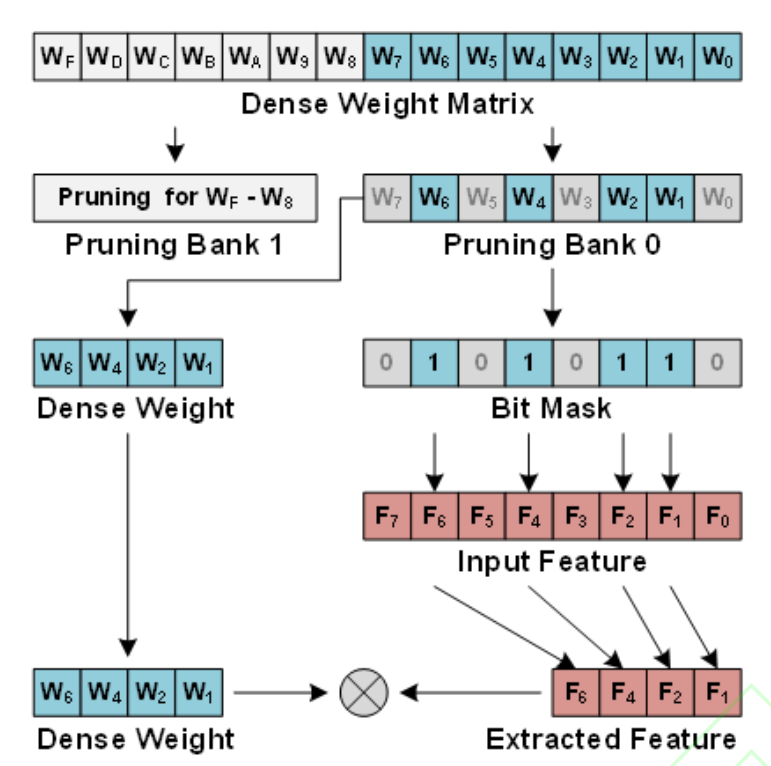

下图展示了模型权重系数稀疏化和稠密存储方案的流程。首先,权重向量被划分为不同的剪枝子组,每个子组具有相同的大小,并按照预定义的稀疏度进行修剪。为了确定稀疏率和剪枝子组的大小,我们在 Enwik-8 和 Text-8 任务上使用 12 层注意力模型。在通过全局修剪对网络进行稀疏化时,我们发现在剪枝子组大小为 32、修剪四分之三的权重时,网络性能保持不变。因此,我们将剪枝子组大小设置为 32,稀疏率设置为 75%,以进行稀疏前馈计算。随后,剪枝后的权重被压缩为密集向量和用二进制编码表示的比特掩码,后者可以指示稠密权重的原始位置。最后,根据比特掩码的信息,我们需要从原始输入中提取和路由那些未跳过的输入特征。这一过程实现了对稀疏权重的有效处理。最终的乘积是通过将这两个稠密向量相乘得到的。整个流程的顺序性和稳健性保证了功能的正确性和高效性。

(三)基于蝶形网络的稀疏提取拓扑

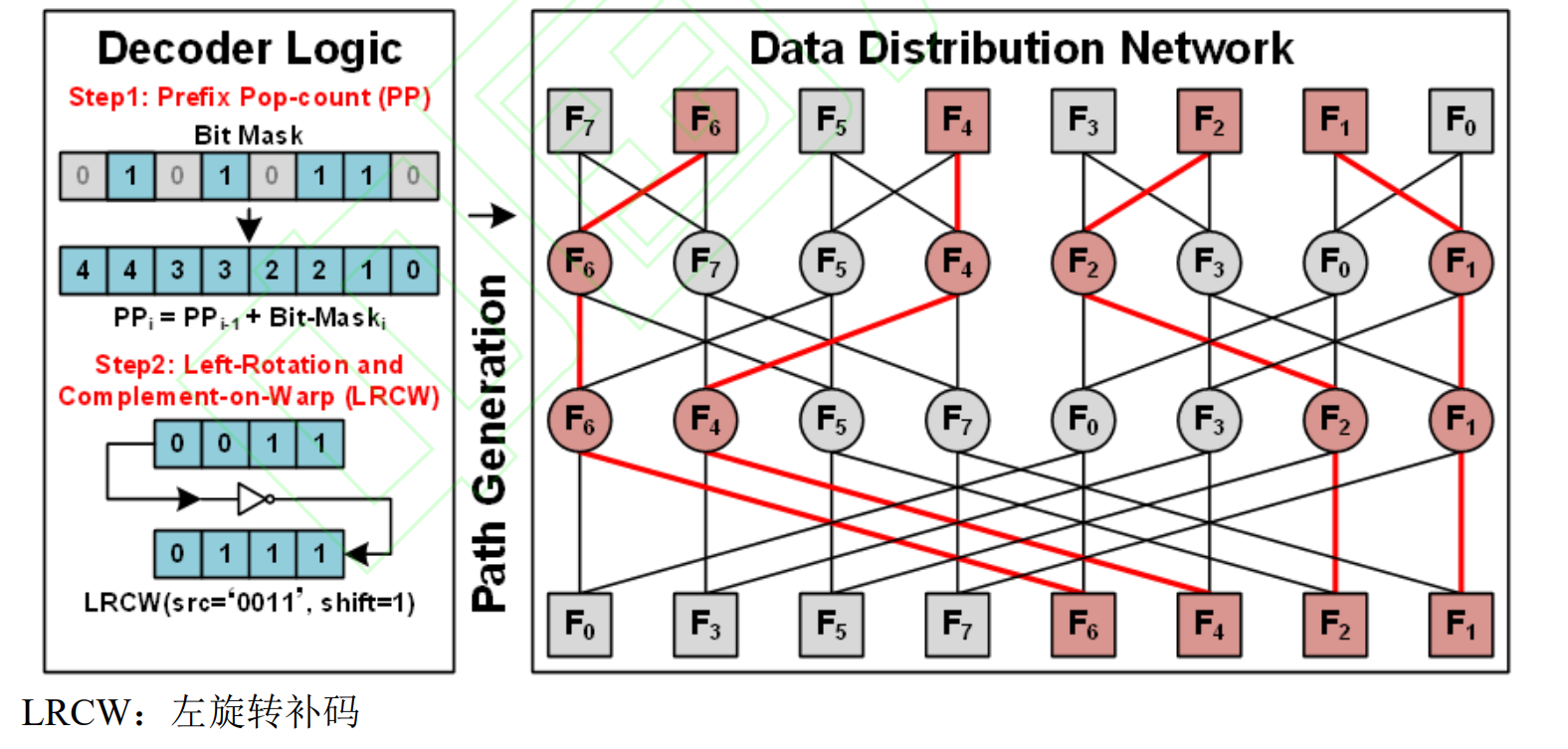

我们运用蝶形网络来提取压缩后的稠密权重所对应的输入激活特征。如下图所示,红色的特征经过蝶形的拓扑网络后,被路由至右侧。这个蝶形网络基于传输管的实现,而传输管的控制信号由解码器实时产生。解码器逻辑接收稠密权重的比特掩码,然后生成控制比特以配置蝶形网络中数据分发的路径。解码机制主要包含两个操作,即前缀 pop 计数和左旋转补码(LRCW)。前缀 pop 计数扫描位掩码的序列,并输出当前位置之前 1 的总数。LRCW 是一个标准的左旋转,其唯一不同之处在于移位在任何时候都以补码形式表示。通过这样的操作,我们能够有效地处理比特掩码,从而实现对蝶形网络的灵活配置和输入特征的提取。

五、性能对比分析

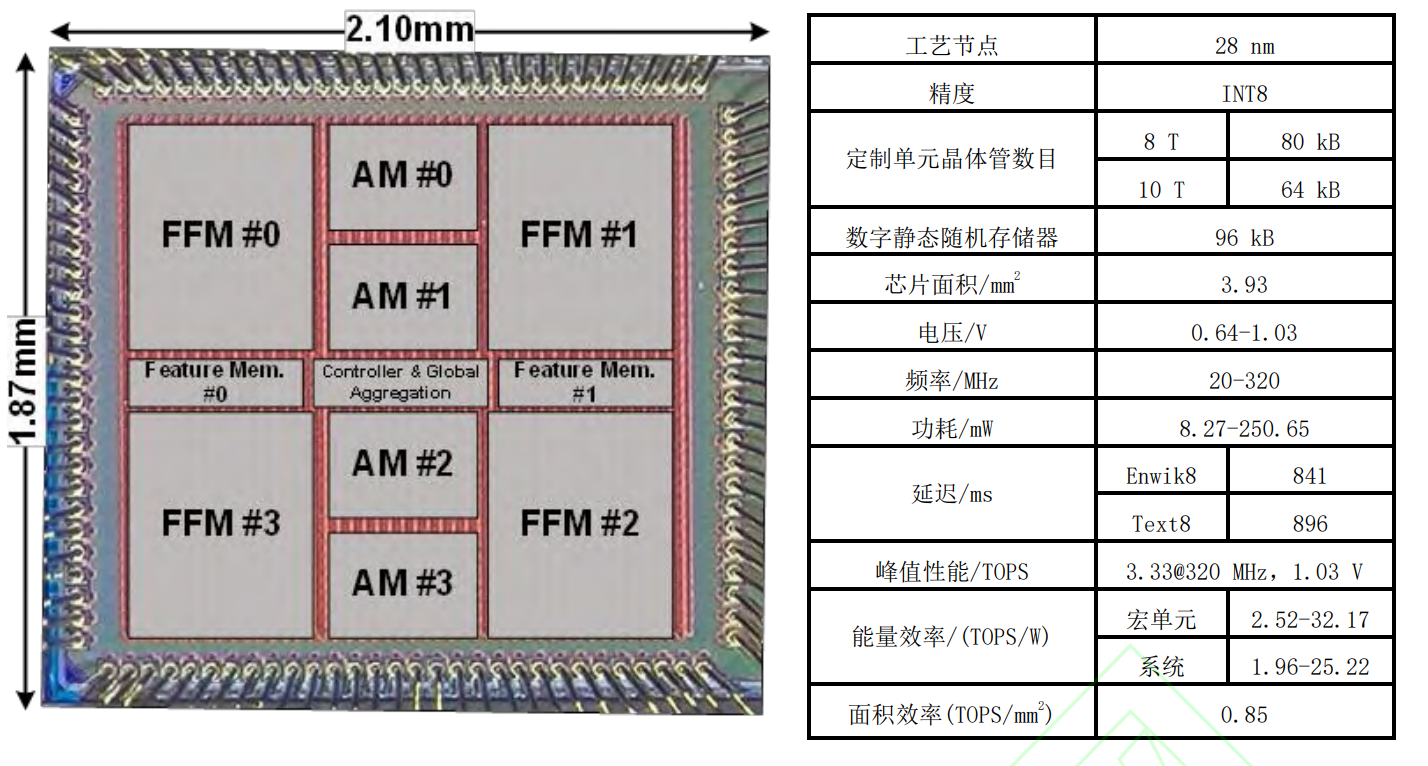

下图展示了采用 28 nm CMOS 工艺制造的芯片,该芯片工作频率高达 320 MHz,总功耗为 250.65 mW。考虑到网络稀疏性,该芯片的峰值性能为 3.3 TOPS。芯片面积 3.93 mm²,面积效率为 0.85 TOPS/mm²。该芯片在生成查询、键和值矩阵和整体注意力方面分别实现了高达 11.83/25.22 TOPS/W 的系统能效。上述轻量化-存内压缩协同设计方案实现了稀疏网络在存算一体硬件上的稠密映射,显著提高存储密度和计算能效。

与传统的 GPU/TPU + DRAM 分离计算架构相比,存算一体架构在带宽需求、功耗和面积效率等方面均表现出显著的优势。在相同的令牌速率和算力要求下,存算一体架构仅需 32~64 Gbit/s 的带宽,相比 xPU+HBM 架构节省了超过 1 000 倍的带宽。此外,存算一体芯片的面积效率达到了 0.85 TOPS/mm²,远高于传统架构。在功耗方面,存算一体芯片的总功耗为 250.65 mW,而传统架构的功耗通常在瓦特级别,这表明存算一体架构在能效方面具有巨大的潜力。

六、未来发展趋势与展望

随着技术的不断进步,存算一体技术将在性能、功耗和集成度等方面实现持续优化。通过改进存储单元结构和材料,以及采用更先进的封装技术如3D堆叠和异构集成,存算一体技术有望进一步提升存储密度和读写速度,实现更高层次的功能集成和性能提升。存算一体架构的设计也将更加灵活和多样化,以满足不同应用场景和模型的需求。未来,矢量计算CPU与存算颗粒的融合将成为重要趋势。矢量计算CPU具备强大的通用计算能力和高效的指令集,能够处理复杂的控制逻辑和数据预处理任务,而存算颗粒则专注于数据密集型的计算任务,通过存内计算实现高效率的数据处理。这种融合架构将充分发挥两者的优点,实现计算资源的最优配置和协同工作,为大模型的推理提供更强大的支持。此外,面向大模型的专用硬件架构将成为未来研究的热点。这些架构将围绕大模型的特点和需求进行设计和优化,如支持稀疏计算、大规模并行处理和高效的存储管理等。通过专用硬件架构的创新,可以进一步提高大模型的推理速度和能效,降低部署成本,推动大模型在更多领域的应用和发展。

725

725

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?