本文将根据异步计数器进行讨论(内含代码及仿真波形)

异步计数器和同步计数器相比不同点在于构成异步计数器中的各个触发器的时钟脉冲不一定都是计数输入脉冲,即各级触发器的状态转移不是在同一时钟作用下发生的。

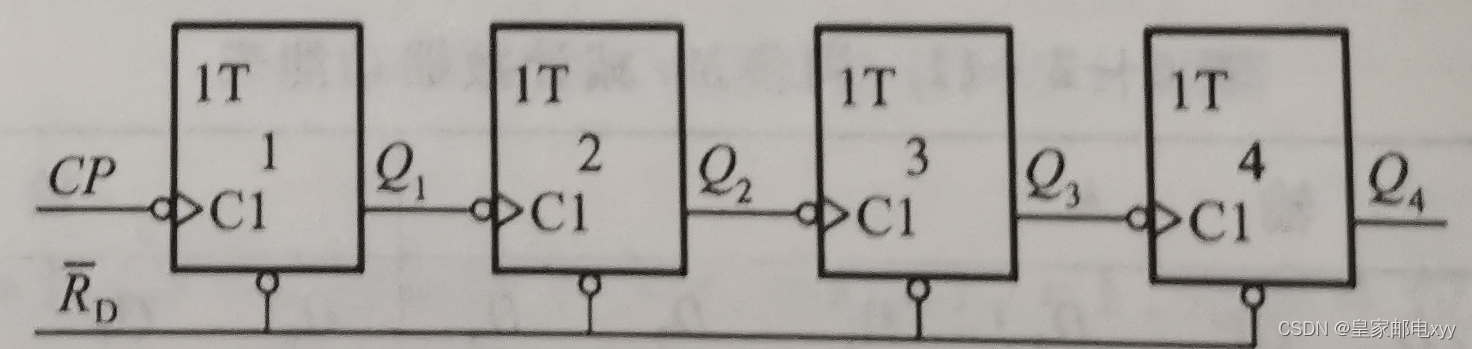

模10计数器原理图

该图描述的是一个由四个T触发器构成的四位二进制异步计数器,其中cp为计数器输入脉冲,Q1,Q2,Q3分别为触发器2,3,4的时钟

然后我们使用verliog语言对其进行描述

基本思想:定义一个计数器count,当时钟的上升沿或者复位信号的下降沿来临时,计数器置0,当计数器从0计到9的时候(即满足计10个数),计数器置0,其他情况计数器加1。

下面展示一些 具体代码以及测试代码。

module counter10(clk,rst_n,count);

input clk,rst_n

本文探讨了异步计数器与同步计数器的区别,并以Verilog语言详细阐述了如何设计一个模10计数器。通过仿真波形展示了计数器在接收到10个脉冲后自动重置回0的过程,从而实现异步计数功能。

本文探讨了异步计数器与同步计数器的区别,并以Verilog语言详细阐述了如何设计一个模10计数器。通过仿真波形展示了计数器在接收到10个脉冲后自动重置回0的过程,从而实现异步计数功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9684

9684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?