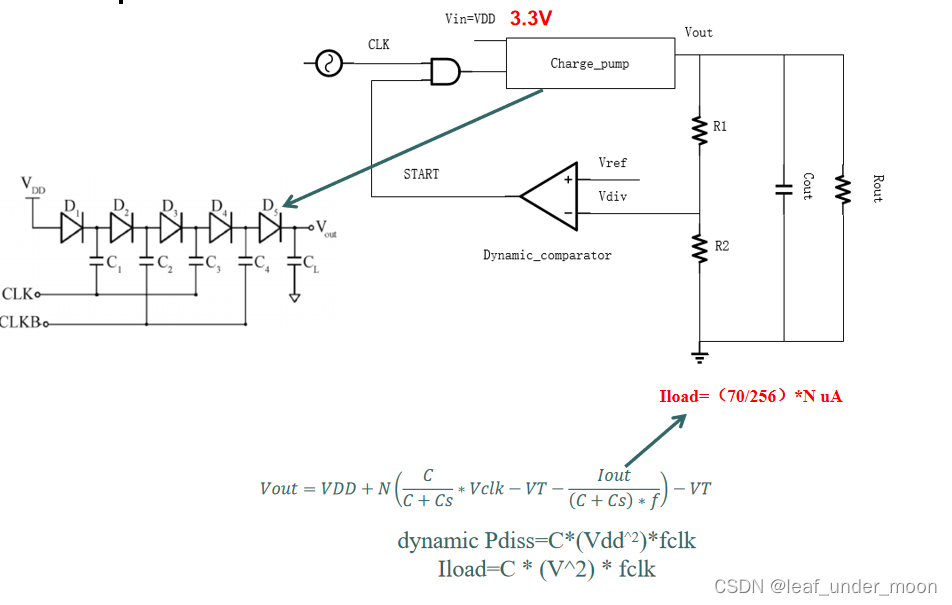

一.电路架构

二. 代码

`include "constants.vams"

`include "disciplines.vams"

module cp_model(vin,vclk,en,vout);

input vin,vclk,en;

output vout;

electrical vin,vclk,en,vout;

parameter real vout_max=21 from (0:inf];

parameter real deltv=0.3 from (0:inf];

parameter real vdd=3 from (0:inf];

parameter real iload=1.2u from [0:inf);

parameter real cstep=2p from [0:inf);

parameter real fclk=10M from [0:inf);

real vout_val;

analog begin

@(initial_step)begin

vout_val=V(vin);

end

@(cross(V(vclk)-vdd/2,1))begin

if(V(en)==0)begin

vout_val=0;

end

else begin

if(iload==0)begin

if(vout_val<vout_max)begin

vout_val=vout_val+deltv;

end

else begin

vout_val=vout_max;

end

end

else begin

if(vout_val<vout_max)begin

vout_val=vout_val+deltv-(iload/(2*fclk*cstep));

end

else begin

vout_val=vout_max-(iload/(2*fclk*cstep));

end

end

end

end

V(vout)<+vout_val;

end

endmodule

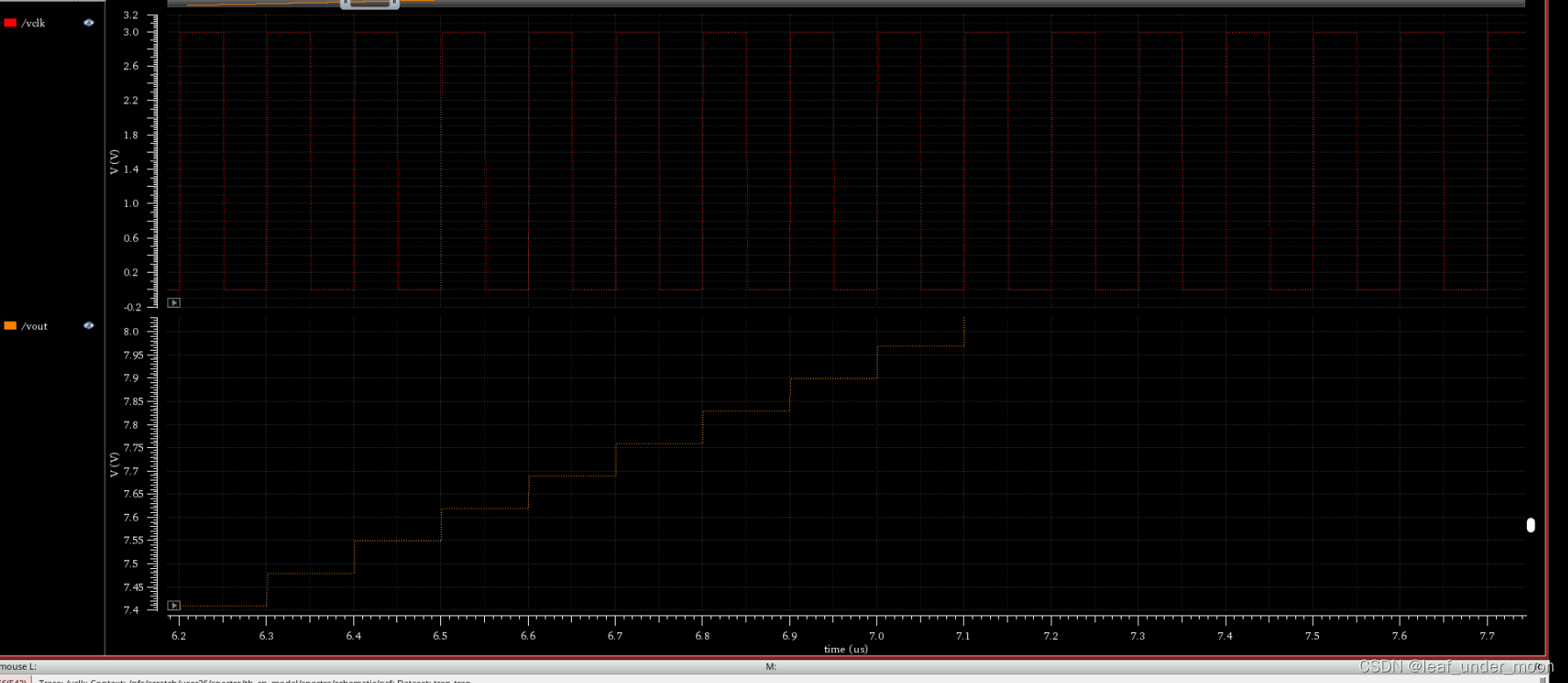

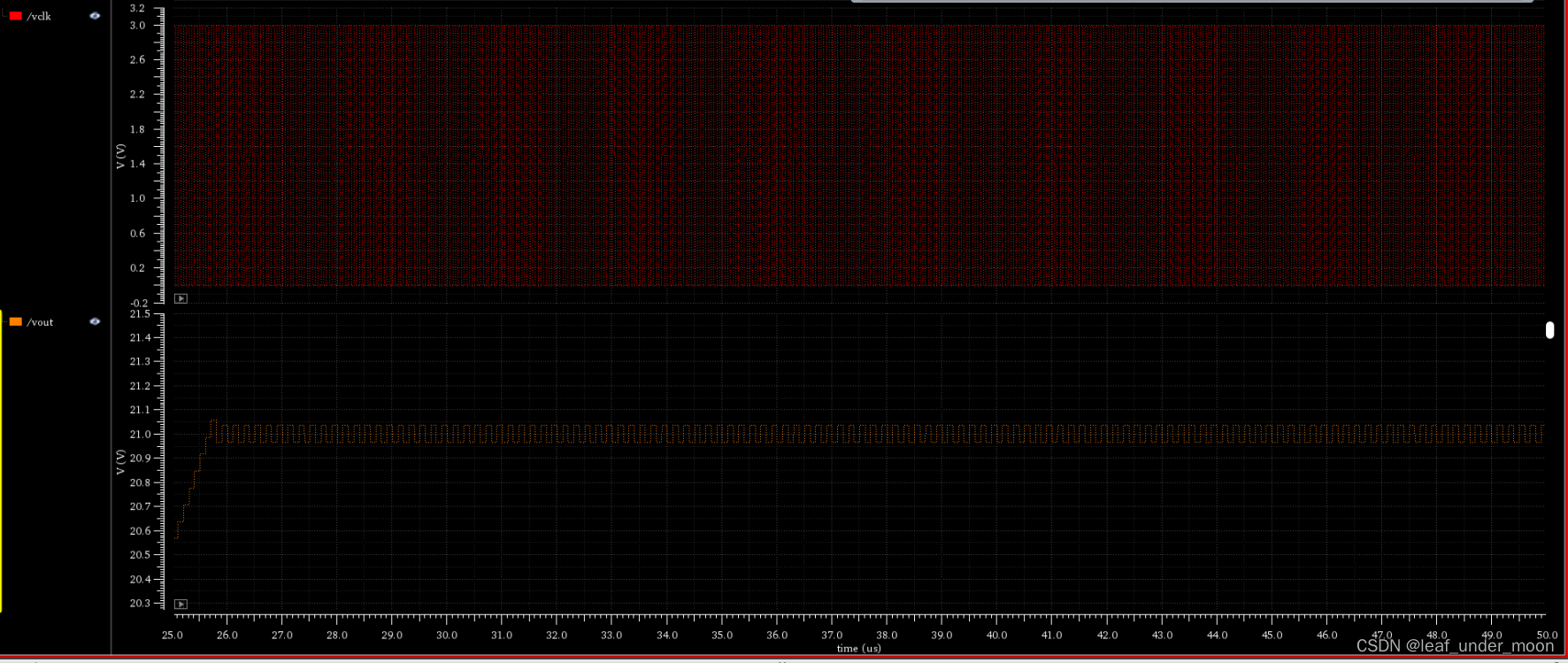

三. 仿真

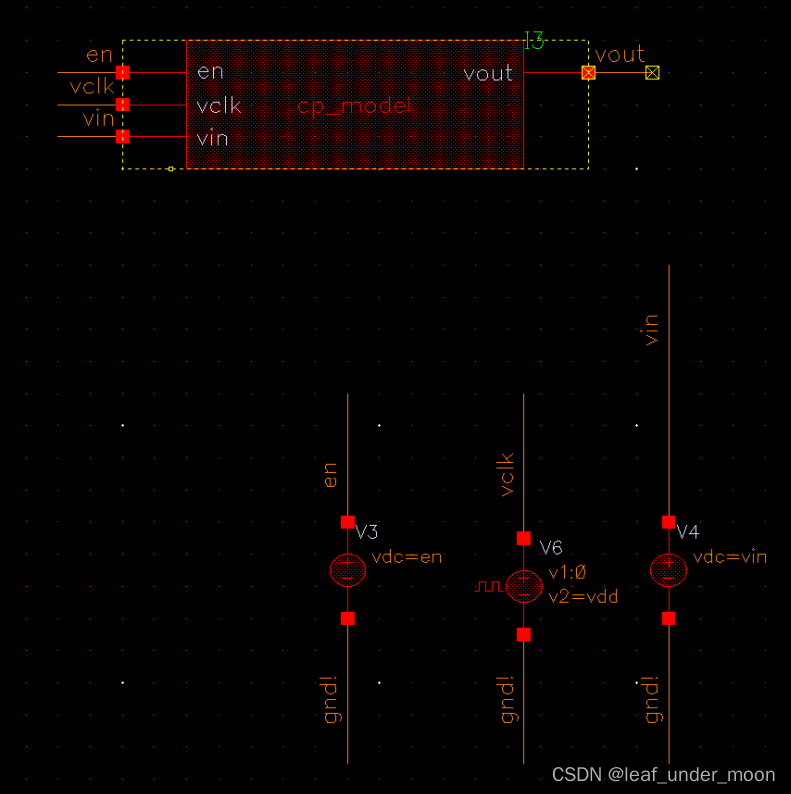

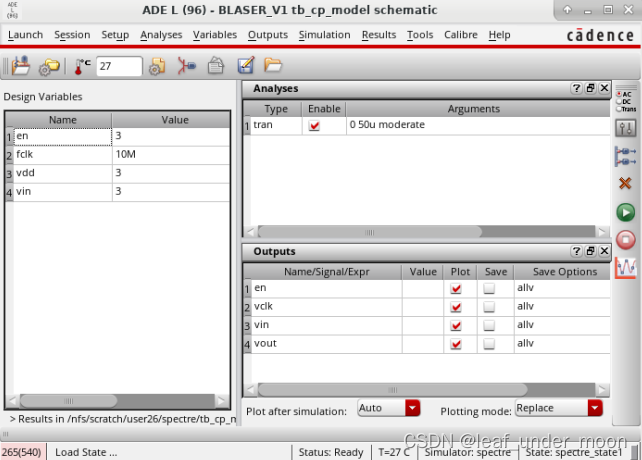

1.testbench

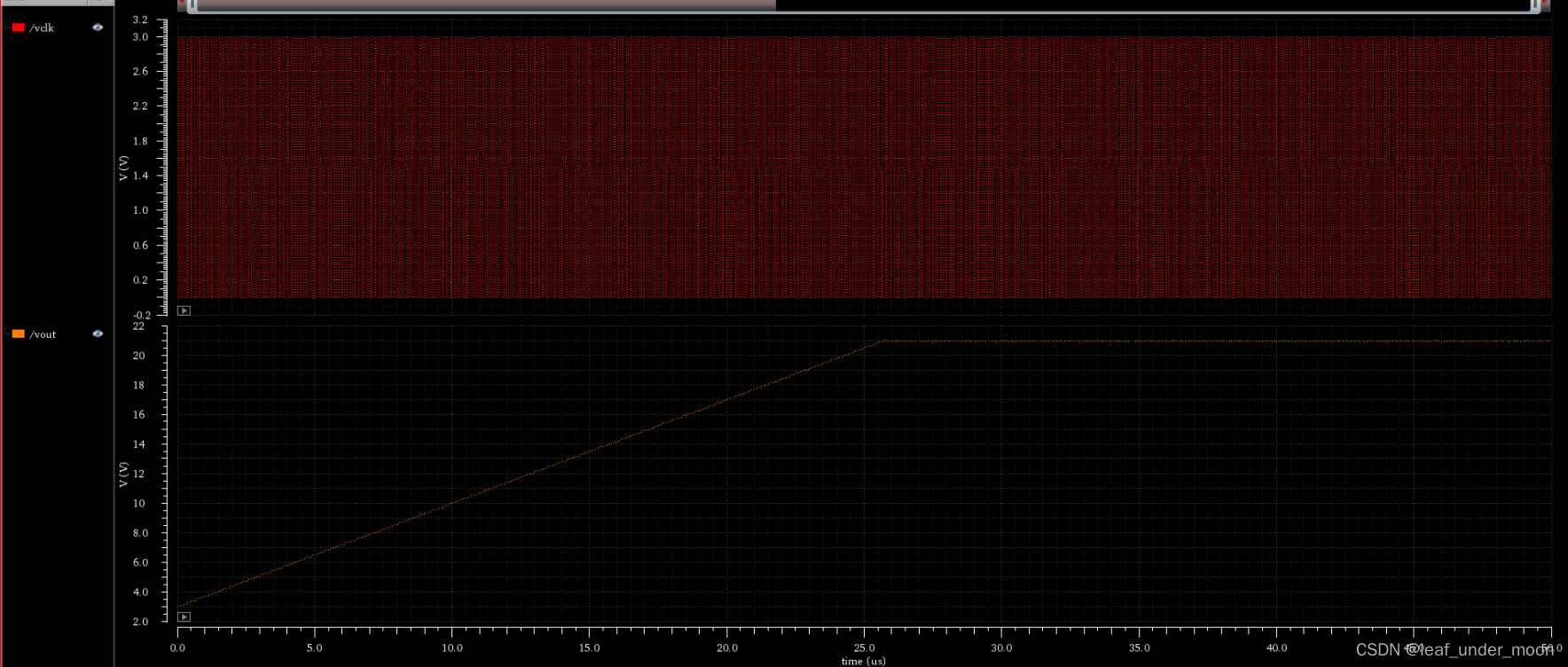

2.仿真结果

该文章介绍了一个基于VerilogHDL的电路模型,模型包含输入Vin,Vclk,En和输出Vout。参数包括最大输出电压、电压步进、电源电压、负载电流和时钟频率。在时钟边沿触发下,根据使能信号En和负载电流调整输出电压。还提到了测试bench和仿真结果。

该文章介绍了一个基于VerilogHDL的电路模型,模型包含输入Vin,Vclk,En和输出Vout。参数包括最大输出电压、电压步进、电源电压、负载电流和时钟频率。在时钟边沿触发下,根据使能信号En和负载电流调整输出电压。还提到了测试bench和仿真结果。

1446

1446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?