预习报告部分

- 实验目的:设计和实现一个数字电子钟(利用蜂鸣器能设定条件进行报时),学会设计模块化和复用,以及时钟信号的生成与管理,学会如何使用VHDL来描述和实现复杂的硬件功能。

- 实验原理:

这个电子钟包括分频模块、计数器模块、去抖动模块、控制模块、控制蜂鸣器模块、解码模块和数码管驱动时间显示模块,计数器模块中又有六十计数器模块和二十四计数器模块。其中六十计数器用来实现分秒计时,二十四计数器用来实现小时计数。并且该实验使用来自外部的高频时钟信号,并将其划分为较低的频率,这些频率适合驱动计算秒、分钟和小时的计时逻辑,并且在计时的同时也将各个部分的计数值输入给数码管驱动电路,电路将编码结果输出给数码管作为字选和段选信号。控制模块中,用户可以通过拨动开关的方式输入时间或启动暂停时间,并使用七段显示显示时间。蜂鸣器,蜂鸣器报时,防抖,用来设定在特定时间启动。(比如秒数个位为9时响一次)。

该实验是通过使用一系列计数器来表示小时、分钟和秒来实现的。这些计数器由时钟信号递增,该时钟信号通常以远高于每秒一个脉冲的频率运行。计数器被设计为在达到最大计数时翻转,如在计数分钟或秒时从 59 移动到 00。

- 实验内容:编写VHDL语言代码来在HDLE-1硬件描述语言综合实验平台上,实现数字电子钟功能。

- 实验所用设备: PC个人计算机、Windows操作系统、Quartus II集成开发环境软件、HDLE-2硬件描述语言综合实验平台。

- 实验步骤:①建立工程、②编辑代码、③编译及修改错误、④实验平台装载程序、⑤演示实验结果。

实验报告部分

- 实验步骤:

- 建立工程

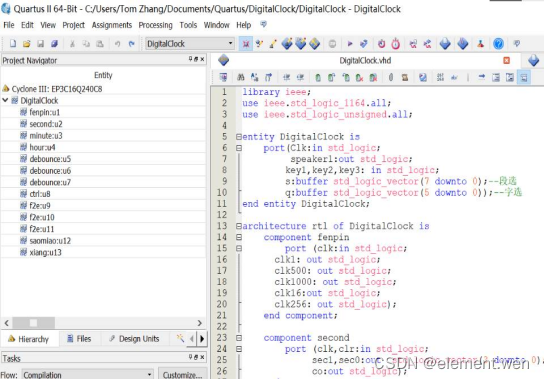

左侧即为建立的各个功能模块,digitalclock作为顶层实体,将其它模块进行综合。

2.编写代码与编译

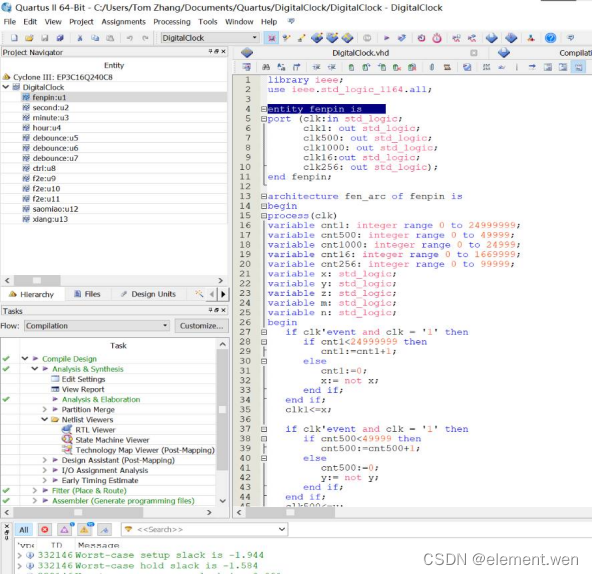

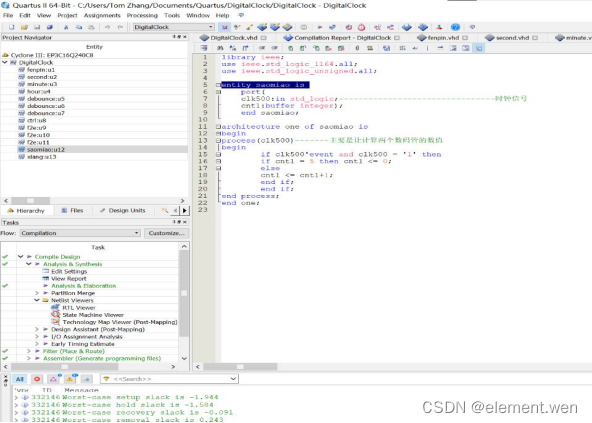

- 分频模块:采用高频时钟输入并生成几个较慢的时钟信号,用于以适当的速度驱动时钟逻辑的不同部分。

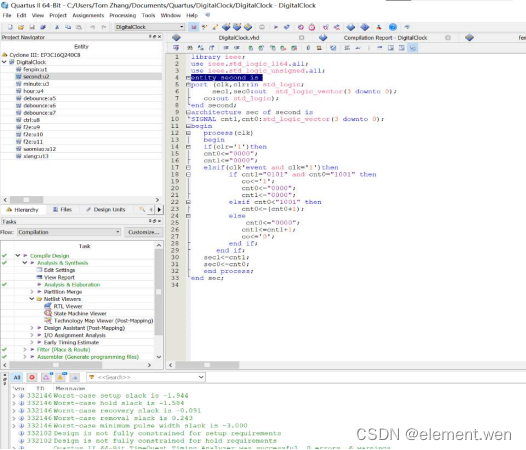

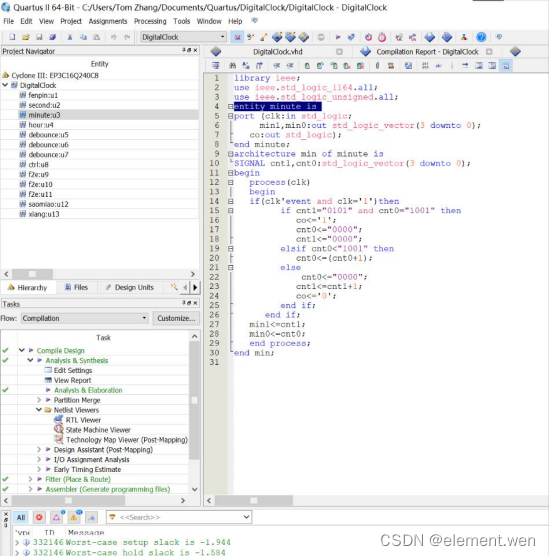

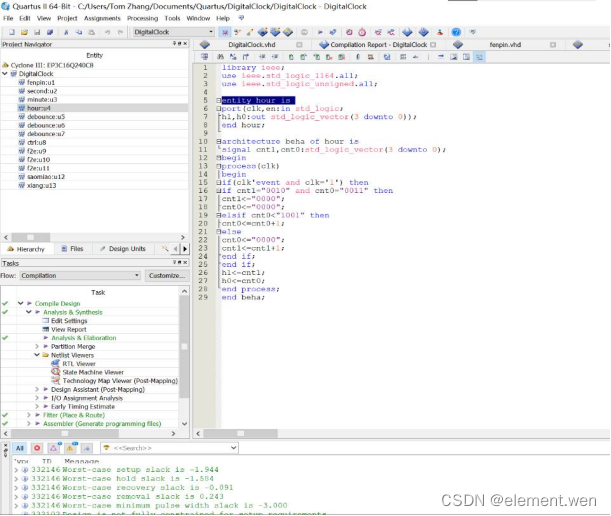

- 计时器模块:用于秒、分钟和小时的计数器模块。它们会增加时间,并在结束复位时提供结转信号 (co)(例如,从 59 秒到 00)。

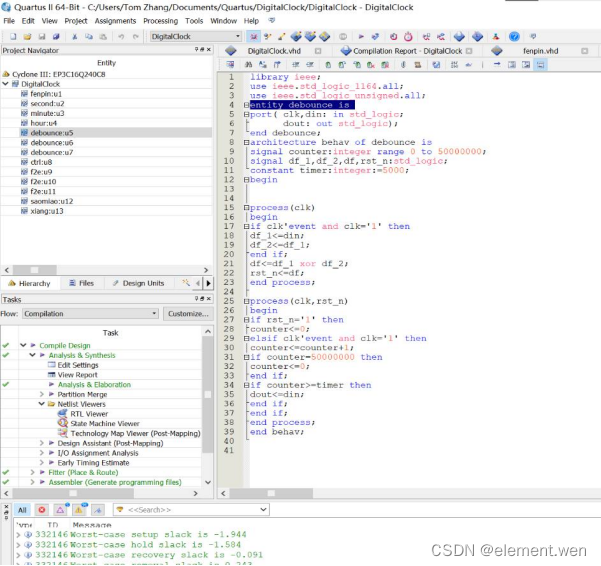

- 去抖动模块:清除来自输入按钮(key1、key2、key3)的信号,过滤掉按下按钮时产生的机械噪音。

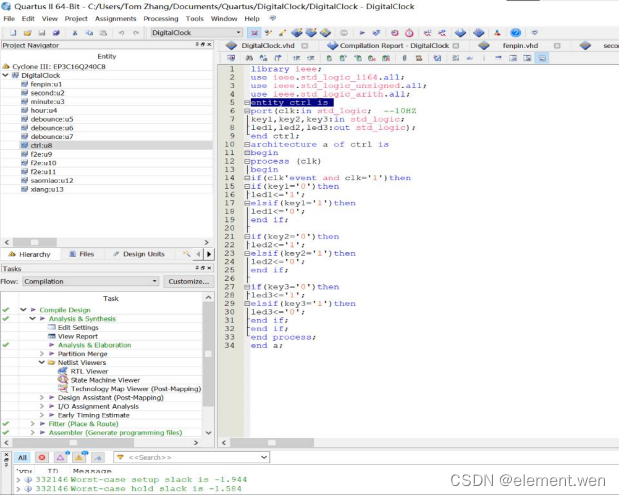

- 控制模块:处理来自按钮的输入以设置时间或控制其他功能。

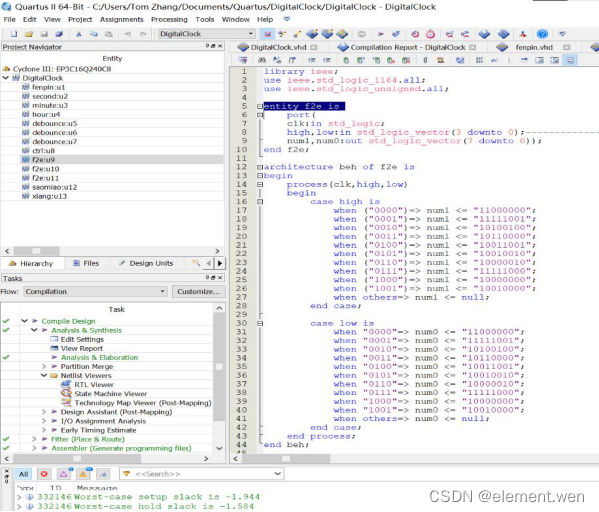

- 解码模块:将二进制编码的十进制 (BCD) 输入转换为用于驱动七段显示器的信号。将高低BCD数字转换为相应的7段代码进行显示。

- saomiao模块:负责扫描或多路复用显示器,驱动数码管显示时间。

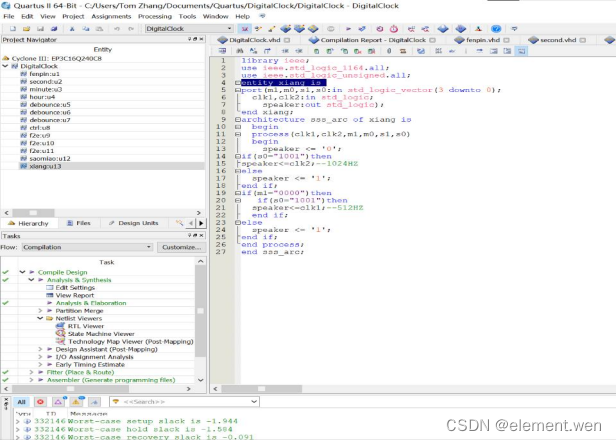

- 蜂鸣器控制模块:

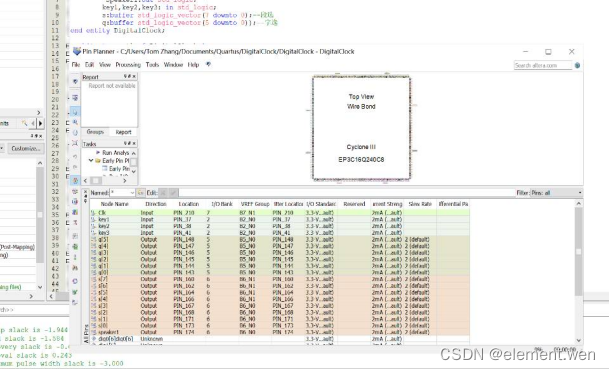

3.分配芯片引脚并编译

4. 实验平台装载程序并演示实验结果

二、 实验数据及结果分析:

编译程序在实验箱上运行结果如下:

- 实验结论:

要用VHDL语言设计一个数字电子时钟,可采用顶层设计的方法,先根据设计系统的功能,从总体要求出发,再从上到下逐步将设计内容细化,最后完成系统硬件的整体设计。在这个实验中,我通过集成分频模块、计数器模块、去抖动模块、控制模块、蜂鸣器控制模块、解码模块以及扫描驱动模块设计了这个数字电子钟系统。该系统能够显示时间,并在设定条件下通过蜂鸣器发出报时信号。实验结果验证了设计的功能性和可靠性,所有模块均能协同工作,符合预期的实验要求。

- 总结及心得体会:

在这次实验中,我选择了数字电子钟作为我的实验内容,这让我受益匪浅。通过这次实验,我深入了解了数字时钟的工作原理和VHDL在硬件设计中的应用。我理解了通过模块化设计能够使问题更加简单化,并且会更便于理解与调试。在实验过程中,我学会了如何处理时钟信号,如何实现模块间的通信,以及如何将抽象概念转化为实际的硬件逻辑,这对我来说无疑是很大的提升。此外,在设计分频器和计数器时,我意识到了精确时序控制的重要性。并且在调试过程中我也遇到了一些困难,但是这些困难与挑战也教会了我在做实验的时候耐心和细致是非常重要的,我意识到了每一个小错误都可能导致整个系统的失败。所以这次实验的成功完成对我来说也有很大帮助,给我带来了许多收获。通过这次实验,我锻炼了我的问题解决和创新思维能力,并且我的专业知识和技能也都有很大提升。当然我也认识到自己还有许多不足,代码设计是一个不断积累和提升的过程,我仍需要去继续努力,提高自己的编程能力,为自己将来可能遇到的工程实践和创新研究打下坚实基础。

- 附录(实验源码)

顶层实体:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity DigitalClock is

port(Clk:in std_logic;

speaker1:out std_logic;

key1,key2,key3: in std_logic;

s:buffer std_logic_vector(7 downto 0);--段选

q:buffer std_logic_vector(5 downto 0));--字选

end entity DigitalClock;

architecture rtl of DigitalClock is

component fenpin

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1910

1910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?