本内容主要介绍了BCD码(Binary-Coded Decimal)的基本概念、8421 BCD码加法原理、BCD码加法电路以及相关的Verilog代码编写的前置知识。

目录:

1、什么是BCD码

2、8421 BCD码加法原理

3、BCD码加法电路

4、元件功能

5、BCD码的Verilog代码

前置知识:卡诺图与逻辑代数化简法、数字电路-时序逻辑电路。

1、什么是BCD码

Binary-Coded Decimal缩写BCD,用4位二进制数来表示1位十进制数中的0~9这10个数码,简称BCD码。日常所说的BCD码大都是指8421 BCD码形式。

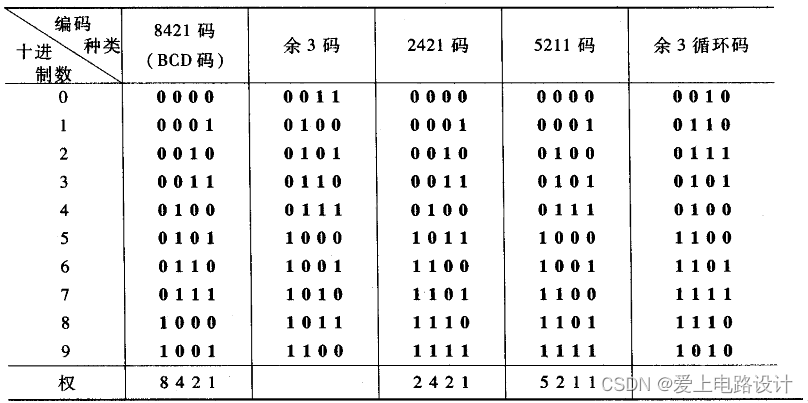

十进制数的几种4位编码

8421 BCD码表示形式如下表所示。

| 1 | 0001 | 4 | 0100 | 7 | 0111 |

| 2 | 0010 | 5 | 0101 | 8 | 1000 |

| 3 | 0011 | 6 | 0110 | 9 | 1001 |

2、8421 BCD码加法原理

BCD码中0~9可以用四位二进制数0000~1001表示,而1010~1111这6个数为无效数。两个4位二进制数相加所得的结果超过1001,则将所得数加0110,来跳过6个无效数,并产生一个进位。

3、BCD码加法电路

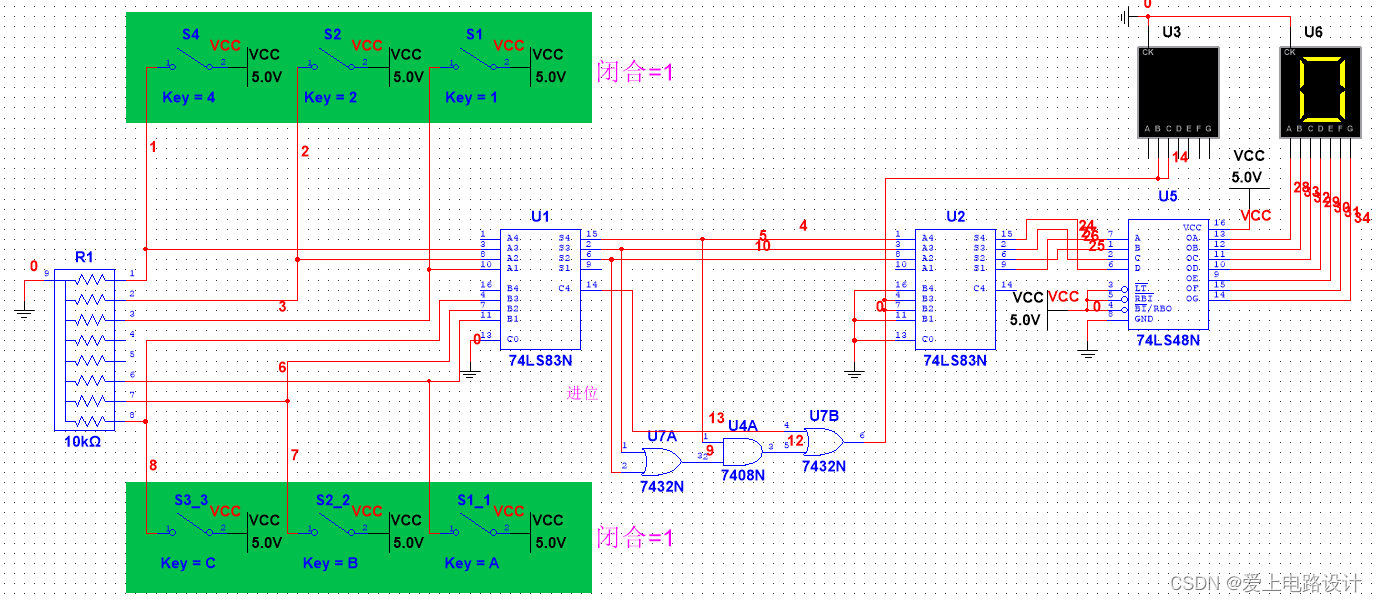

电路由4位二进制超前进位全加器、进位控制电路、译码器74LS47N、显示电路共4个部分组成。其部分电路如下图所示,仿真原文件下载移步:两个BCD码的加法运算。

也可以使用74LS83N,如下图所示。

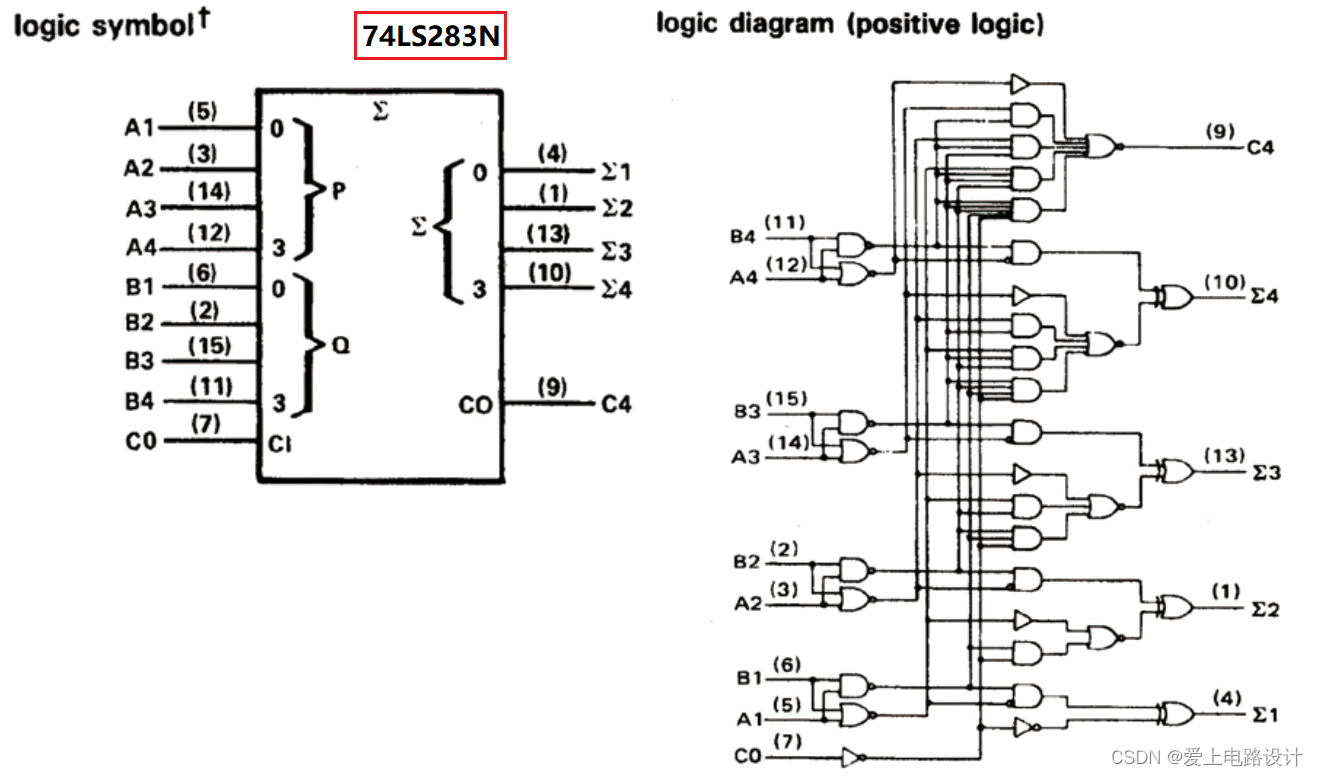

4、元件功能

5、BCD码的Verilog代码

module bcd(cout,sum,ina,inb,cin);

input cin;

input [3:0] ina,inb;

output reg [3:0] sum; //等价于output [3:0] sum;reg [3:0] sum;

output reg cout;

reg [4:0] temp;

always @(ina, inb, cin)

begin

temp<=ina+inb+cin;

if(temp>9)

{cout,sum}<=temp+6;

else

{cout,sum}<=temp;

end

endmodule知我所能,我所能者,尽善尽美;知我所不能,我所不能者,虚怀若谷。觉得不错,动动发财的小手点个赞哦!

本文详细阐述了BCD码的基本概念,重点讲解了8421BCD码的加法规则,介绍了对应的电路结构,包括4位二进制全加器和进位控制机制,并提供了Verilog代码示例。

本文详细阐述了BCD码的基本概念,重点讲解了8421BCD码的加法规则,介绍了对应的电路结构,包括4位二进制全加器和进位控制机制,并提供了Verilog代码示例。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?