文章目录

Verilog

Verilog仿真时在外部调用某个函数内部的task

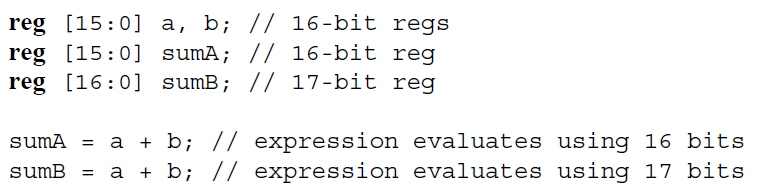

表达式位长

参考《verilog2005标准》、《verilog编程艺术》

规则

self-determined expression

A self-determined expression is one where the bit length of the expression is solely determined by the expression itself—for example,an expression representing a delay value

自决定表达式,就是表达式的位长完全由表达式本身决定——例如,表示延迟值的表达式

context-determined expression

A context-determined expression is one where the bit length of the expression is determined by the bit length of the expression and by the fact that it is part of another expression. For example, the bit size of the righthand expression of an assignment depends on itself and the size of the left-hand side

上下文决定表达式,就是表达式的位长既由表达式决定,也由这样的事实决定(表达式本身也是另一个表达式的一部分)。 例如,赋值RHS的位长既依赖于它本身,也依赖于LHS的位长

几个例子

在计算表达式时,中间结果就取操作数的最大位位长 (如果是赋值,也包含LHS),所以计算时要防止中间结果出现丢失。

《verilog编程艺术》一书中补充的例子

符号表达式

规则

中文版

几个例子

在verilog中使用断言

在verilog中使用下面的方式进行断言,

initial begin

if (AXIS_PCIE_DATA_WIDTH != 64 && AXIS_PCIE_DATA_WIDTH != 128 && AXIS_PCIE_DATA_WIDTH != 256 && AXIS_PCIE_DATA_WIDTH != 512) begin

$error("Error: PCIe interface width must be 64, 128, 256, or 512 (instance %m)");

$finish;

end

end

systemverilog

闲暇之际,抽了点时间了解了一下systemverilog。由于不做测试,重点看了一下可综合的部分语法。

参考书

语法小结

- 四态变量、二态变量的相关知识点

- logic能够代替大多数的reg、wire,但也要注意,

- 当用于inout端口声明、多重驱动时,wire不可以用logic替代

- wire sig = A&b;的写法与logic sig = A & B;并不一致,后者仅仅表示初始化,不能代表连续赋值

- 较简单的用法:设计时,组合逻辑采用always_comb,时序逻辑采用always_ff

- package的用法:和VHDL中package类似,可以包含函数定义(function)、类型声明(typedef、enum)、常量定义(parameter、const);使用package时,import xxx_pkg:: *

- interface不能在package中定义,可以在一个文件中单独定义,也可以在svh文件中定义,使用include语句包含进来;注意modport的用法

- 注意type parameter的用法

- 注意数组packed和unpacked的区别;packed的数组可以直接赋值给一个vector

几点考虑

- ISE不支持systemverilog,vivado支持systemverilog,如此的话,在不考虑使用第三方综合工具的情况下,使用SV的设计无法移植到7系列以下的器件中,这点很值得权衡

- 当SV的设计中不包含IP时,vivado综合出的edn网表可以在ISE中使用(仅仅做过简单测试,不代表所有情况)。考虑到新版本的vivado对于某些原语增加了新的属性,因此,如果网表想在ISE中使用的话,可以尝试使用ISE14.4对应的vivado2012.4版本

- 目前来看,systemverilog的接口部分,VHDL无对应语法;systemverilog的编译预处理指令,VHDL无对应语法(这个的确很有用)。其他的部分,package、自定义类型、enum等特性,VHDL还是很好用的

1705

1705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?